|

|

PDF ADF4218 Data sheet ( Hoja de datos )

| Número de pieza | ADF4218 | |

| Descripción | Dual RF PLL Frequency Synthesizers | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADF4218 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

a

Dual RF PLL Frequency Synthesizers

ADF4216/ADF4217/ADF4218

FEATURES

GENERAL DESCRIPTION

ADF4216: 550 MHz/1.2 GHz

The ADF4216/ADF4217/ADF4218 are dual frequency synthe-

ADF4217: 550 MHz/2.0 GHz

sizers that can be used to implement local oscillators (LOs) in

ADF4218: 550 MHz/2.5 GHz

the upconversion and downconversion sections of wireless

2.7 V to 5.5 V Power Supply

receivers and transmitters. They can provide the LO for both

Selectable Charge Pump Currents

the RF and IF sections. They consist of a low-noise digital PFD

Selectable Dual Modulus Prescaler

(Phase Frequency Detector), a precision charge pump, a pro-

IF: 8/9 or 16/17

RF: 32/33 or 64/65

3-Wire Serial Interface

Power-Down Mode

APPLICATIONS

Wireless Handsets (GSM, PCS, DCS, CDMA, WCDMA)

OBase Stations for Wireless Radio (GSM, PCS, DCS,

CDMA, WCDMA)

BWireless LANS

Communications Test Equipment

SOCATV Equipment

grammable reference divider, programmable A and B counters,

and a dual-modulus prescaler (P/P+1). The A (6-bit) and B

(11-bit) counters, in conjunction with the dual modulus prescaler

(P/P+1), implement an N divider (N = BP + A). In addition,

the 14-bit reference counter (R Counter), allows selectable

REFIN frequencies at the PFD input. A complete PLL (Phase-

Locked Loop) can be implemented if the synthesizers are

used with an external loop filter and VCOs (Voltage Con-

trolled Oscillators).

Control of all the on-chip registers is via a simple 3-wire interface.

The devices operate with a power supply ranging from 2.7 V

to 5.5 V and can be powered down when not in use.

LFUNCTIONAL BLOCK DIAGRAM

EVDD1 VDD2 VP1 VP2

TEN=BP+A

ADF4216/ADF4217/ADF4218

IFINA

IFINB

IF

PRESCALER

11-BIT IF

B-COUNTER

PHASE

COMPARATOR

CHARGE

PUMP

CPIF

6-BIT IF

A-COUNTER

IF

LOCK

DETECT

REFIN

CLOCK

DATA

LE

OSCILLATOR

22-BIT

DATA

REGISTER

SDOUT

RFINA

RFINB

N = BP + A

RF

PRESCALER

14-BIT IF

R-COUNTER

14-BIT IF

R-COUNTER

11-BIT RF

B-COUNTER

6-BIT RF

A-COUNTER

OUTPUT

MUX

MUXOUT

RF

LOCK

DETECT

PHASE

COMPARATOR

CHARGE

PUMP

CPRF

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

DGNDRF AGNDRF DGNDIF DGNDIF AGNDIF

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

1 page

ADF4216/ADF4217/ADF4218

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1 VDD1 Positive Power Supply for the RF Section. Decoupling capacitors to the analog ground plane should be

placed as close as possible to this pin. VDD1 should have a value of between 2.7 V and 5.5 V. VDD1 must

have the same potential as VDD2.

2 VP1

Power Supply for the RF Charge Pump. This should be greater than or equal to VDD.

3 CPRF

Output from the RF Charge Pump. When enabled this provides ± ICP to the external loop filter, which in

turn drives the external VCO.

4 DGNDRF Ground Pin for the RF Digital Circuitry.

5

RFINA

Input to the RF Prescaler. This low-level input signal is normally ac-coupled to the external VCO.

6

RFINB

Complementary Input to the RF Prescaler. This point should be decoupled to the ground plane with a small

bypass capacitor, typically 100 pF.

7 AGNDRF Ground Pin for the RF Analog Circuitry.

8

REFIN

Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and an equivalent input resis-

tance of 100 kΩ. This input can be driven from a TTL or CMOS crystal oscillator or it can be ac-coupled.

9 DGNDIF Ground Pin for the IF Digital (Interface and Control Circuitry).

10 MUXOUT This multiplexer output allows either the IF/RF lock detect, the scaled RF, or the scaled Reference Fre-

O quency to be accessed externally. See Table V.

B11 CLK

Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched

into the 22-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.

S12 DATA Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control bits. This input is

Oa high impedance CMOS input.

L13 LE

Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of

the four latches, the latch being selected using the control bits.

E14 AGNDIF Ground Pin for the IF Analog Circuitry.

TE15 IFINB

Complementary Input to the IF Prescaler. This point should be decoupled to the ground plane with a small

bypass capacitor, typically 100 pF.

16 IFINA

Input to the IF Prescaler. This low-level input signal is normally ac-coupled to the external VCO.

17 DGNDIF Ground Pin for the IF Digital, Interface, and Control Circuitry.

18 CPIF

Output from the IF Charge Pump. When enabled this provides ± ICP to the external loop filter, which in turn

drives the external VCO.

19 VP2

Power Supply for the IF Charge Pump. This should be greater than or equal to VDD.

20 VDD2

Positive Power Supply for the IF, Interface, and Oscillator Sections. Decoupling capacitors to the analog

ground plane should be placed as close as possible to this pin. VDD2 should have a value of between 2.7 V

and 5.5 V. VDD2 must have the same potential as VDD1.

PIN CONFIGURATION

VDD1 1

20 VDD2

VP1 2

19 VP2

CPRF 3

18 CPIF

DGNDRF 4 TSSOP 17 DGNDIF

RFINA 5 ADF4216/ 16 IFINA

RFINB 6 ADF4217/ 15 IFINB

AGNDRF 7 ADF4218 14 AGNDIF

REFIN 8

13 LE

DGNDIF 9

12 DATA

MUXOUT 10

11 CLK

REV. 0

–5–

5 Page

ADF4216/ADF4217/ADF4218

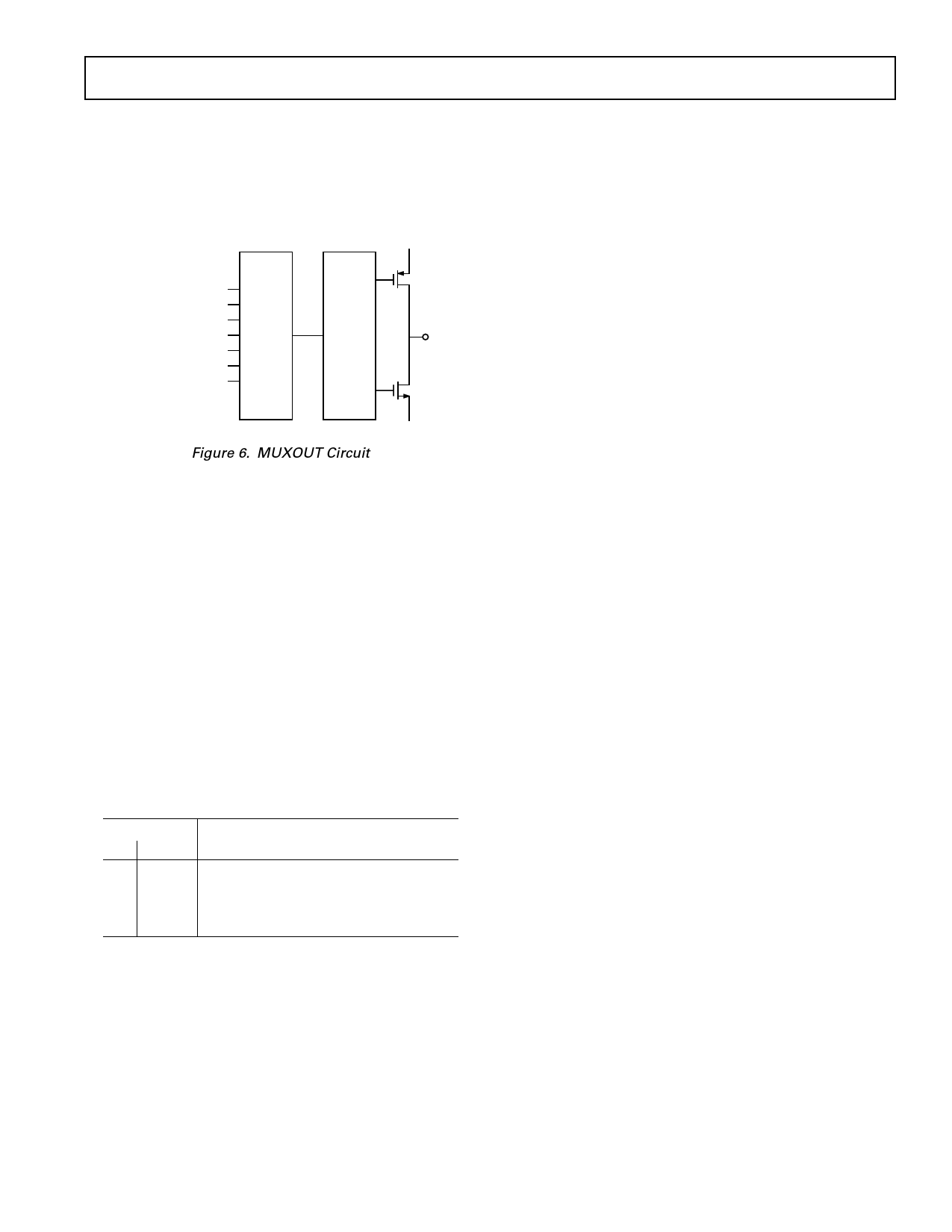

MUXOUT AND LOCK DETECT

The output multiplexer on the ADF4216 family allows the

user to access various internal points on the chip. The state of

MUXOUT is controlled by P3, P4, P11 and P12. See Tables

III and V. Figure 6 shows the MUXOUT section in block dia-

gram form.

2. The IF Counter Reset mode resets the R and N counters in

the IF section and also puts the IF charge pump into three-

state. The RF Counter Reset mode resets the R and N counters

in the RF section and also puts the RF charge pump into

three-state. The IF and RF Counter Reset mode does both

of the above.

Upon removal of the reset bits, the N counter resumes counting

DVDO in close alignment with the R counter (maximum error is one

prescaler output cycle).

IF ANALOG LOCK DETECT

IF R COUNTER OUTPUT

3. The Fastlock mode uses MUXOUT to switch a second loop

filter damping resistor to ground during Fastlock operation.

IF N COUNTER OUTPUT

Activation of Fastlock occurs whenever RF CP Gain in the

IF/RF ANALOG LOCK DETECT

MUX

CONTROL

MUXOUT

RF Reference counter is set to one.

RF R COUNTER OUTPUT

RF N COUNTER OUTPUT

RF ANALOG LOCK DETECT

DGND

O Figure 6. MUXOUT Circuit

BLock Detect

MUXOUT can be programmed for analog lock detect. The N-

Schannel open-drain analog lock detect should be operated with

an external pull-up resistor of 10 kΩ nominal. When lock has

Obeen detected it is high with narrow low-going pulses.

LINPUT SHIFT REGISTER

EThe functional block diagram for the ADF4216 family is shown

Ton Page 1. The main blocks include a 22-bit input shift register,

Ea 14-bit R counter and an 17-bit N counter, comprising a 6-bit

POWER-DOWN

It is possible to program the ADF4216 family for either synchro-

nous or asynchronous power-down on either the IF or RF side.

Synchronous IF Power-Down

Programming a “1” to P7 of the ADF4216 family will initiate a

power-down. If P2 of the ADF4216 family has been set to “0”

(normal operation), a synchronous power-down is conducted.

The device will automatically put the charge pump into three-

State and then complete the power-down.

Asynchronous IF Power-Down

If P2 of the ADF4216 family has been set to “1” (three-state the

IF charge pump), and P7 is subsequently set to “1,” then an

asynchronous power-down is conducted. The device will go into

power-down on the rising edge of LE, which latches the “1” to

the IF power-down bit (P7).

A counter and an 11-bit B counter. Data is clocked into the 22- Synchronous RF Power-Down

bit shift register on each rising edge of CLK. The data is clocked in Programming a “1” to P16 of the ADF4216 family will initiate a

MSB first. Data is transferred from the shift register to one of

power-down. If P10 of the ADF4216 family has been set to “0”

four latches on the rising edge of LE. The destination latch is

(normal operation), a synchronous power-down is conducted. The

determined by the state of the two control bits (C2, C1) in the

device will automatically put the charge pump into three-state

shift register. These are the two LSBs DB1, DB0 as shown in

and then complete the power-down.

the timing diagram of Figure 1. The truth table for these bits is

shown in Table I.

Asynchronous RF Power-Down

If P10 of the ADF4216 families has been set to “1” (three-state

Table I. C2, C1 Truth Table

the RF charge pump), and P16 is subsequently set to “1,” an

asynchronous power-down is conducted. The device will go into

Control Bits

C2 C1

Data Latch

power-down on the rising edge of LE, which latches the “1” to

the RF power-down bit (P16).

0 0 IF R Counter

0 1 IF AB Counter (and Prescaler Select)

1 0 RF R Counter

1 1 RF AB Counter (and Prescaler Select)

PROGRAM MODES

Table III and Table V show how to set up the Program Modes

in the ADF4216 family. The following should be noted:

Activation of either synchronous or asynchronous power-down

forces the IF/RF loop’s R and N dividers to their load state

conditions and the IF/RF input section is debiased to a high

impedance state.

The REFIN oscillator circuit is only disabled if both the IF and

RF power-downs are set.

The input register and latches remain active and are capable of

loading and latching data during all the power-down modes.

1. IF and RF Analog Lock Detect indicate when the PLL is in

lock. When the loop is locked and either IF or RF Analog

Lock Detect is selected, the MUXOUT pin will show a logic

The IF/RF section of the devices will return to normal powered

up operation immediately upon LE latching a “0” to the appro-

priate power-down bit.

high with narrow low-going pulses. When the IF/RF Analog

Lock Detect is chosen, the locked condition is indicated only

when both IF and RF loops are locked.

REV. 0

–11–

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet ADF4218.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADF4210 | Dual RF/IF PLL Frequency Synthesizers | Analog Devices |

| ADF4211 | Dual RF/IF PLL Frequency Synthesizers | Analog Devices |

| ADF4212 | Dual RF/IF PLL Frequency Synthesizers | Analog Devices |

| ADF4213 | Dual RF/IF PLL Frequency Synthesizers | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |