|

|

PDF IS49NLC36800 Data sheet ( Hoja de datos )

| Número de pieza | IS49NLC36800 | |

| Descripción | Common I/O RLDRAM 2 Memory | |

| Fabricantes | Integrated Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de IS49NLC36800 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

IS49NLC93200,IS49NLC18160,IS49NLC36800

288Mb (x9, x18, x36) Common I/O RLDRAM® 2 Memory

FEATURES

ADVANCED INFORMATION

JUNE 2012

• 533MHz DDR operation (1.067 Gb/s/pin data

rate)

• 38.4Gb/s peak bandwidth (x36 at 533 MHz

clock frequency)

• Reduced cycle time (15ns at 533MHz)

• 32ms refresh (8K refresh for each bank; 64K

refresh command must be issued in total each

32ms)

• 8 internal banks

• Non-multiplexed addresses (address

multiplexing option available)

• SRAM-type interface

• Programmable READ latency (RL), row cycle

time, and burst sequence length

• Balanced READ and WRITE latencies in order to

optimize data bus utilization

• Data mask signals (DM) to mask signal of

WRITE data; DM is sampled on both edges of

DK.

• Differential input clocks (CK, CK#)

• Differential input data clocks (DKx, DKx#)

• On-die DLL generates CK edge-aligned data and

output data clock signals

• Data valid signal (QVLD)

• HSTL I/O (1.5V or 1.8V nominal)

• 25-60Ω matched impedance outputs

• 2.5V VEXT, 1.8V VDD, 1.5V or 1.8V VDDQ I/O

• On-die termination (ODT) RTT

• IEEE 1149.1 compliant JTAG boundary scan

• Operating temperature:

Commercial

(TC = 0° to +95°C; TA = 0°C to +70°C),

Industrial

(TC = -40°C to +95°C; TA = -40°C to +85°C)

OPTIONS

• Package:

− 144-ball FBGA (leaded)

− 144-ball FBGA (lead-free)

• Configuration:

− 32Mx9

− 16Mx18

− 8Mx36

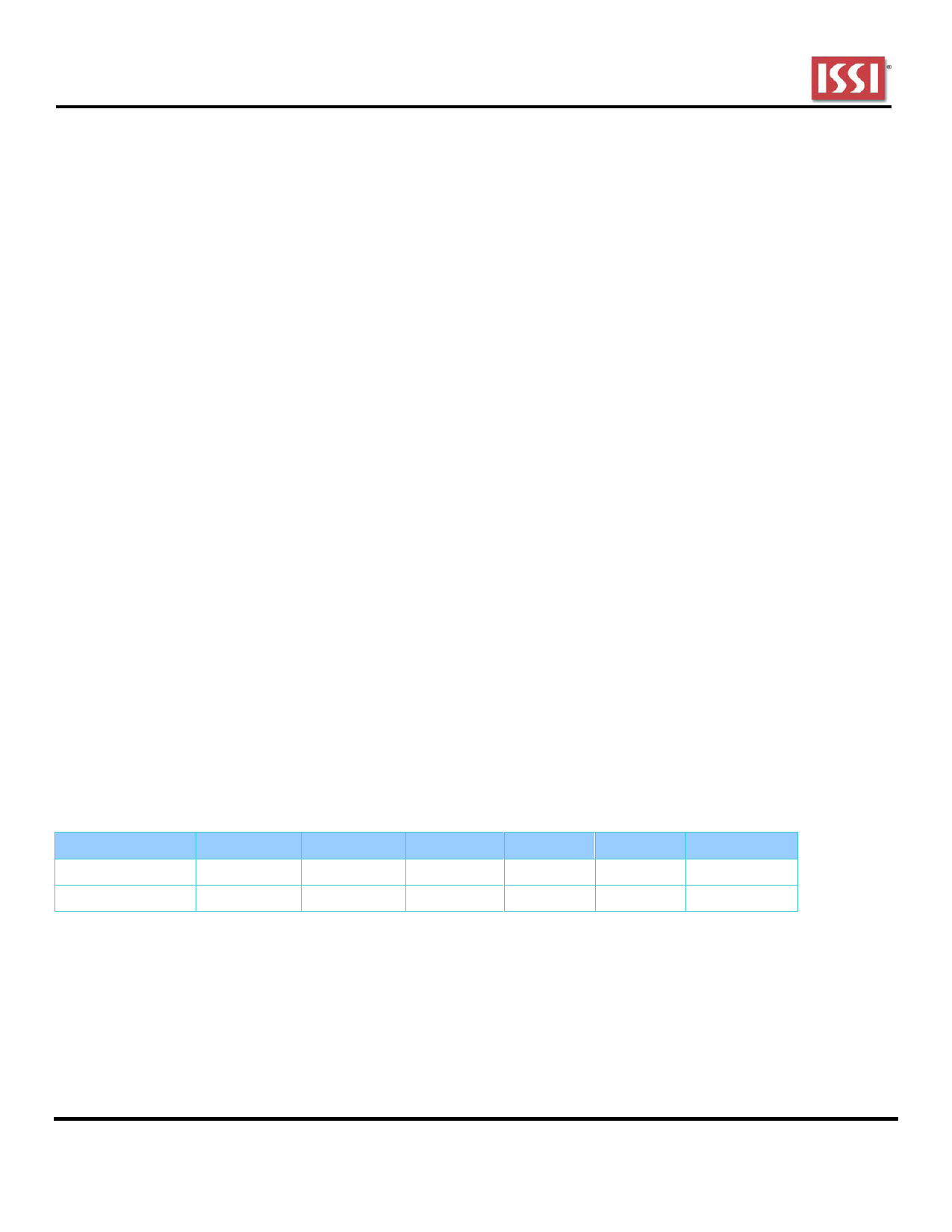

• Clock Cycle Timing:

Speed Grade

-18

tRC 15

tCK 1.875

-25E

15

2.5

-25 -33 -5

20 20 20

2.5 3.3

5

Unit

ns

ns

Copyright © 2012 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without

notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the

latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can

reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such

applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

RLDRAM® is a registered trademark of Micron Technology, Inc.

Integrated Silicon Solution, Inc. – www.issi.com –

Rev. 00F, 06/20/2012

1

1 page

IS49NLC93200,IS49NLC18160,IS49NLC36800

1.4 Ball Descriptions

Symbol

A*

BA*

CK, CK#

Type

Input

Input

Input

Description

Address inputs: Defines the row and column addresses for READ and WRITE operations. During a MODE

REGISTER SET, the address inputs define the register settings. They are sampled at the rising edge of

CK.

Bank address inputs: Selects to which internal bank a command is being applied to.

Input clock: CK and CK# are differential input clocks. Addresses and commands are latched on the rising

edge of CK. CK# is ideally 180 degrees out of phase with CK.

CS#

Input

Chip select: CS# enables the command decoder when LOW and disables it when HIGH. When the

command decoder is disabled, new commands are ignored, but internal operations continue.

DQ*

DK*, DK*#

DM

TCK

TMS,TDI

WE#, REF#

VREF

ZQ

QK*, QK*#

QVLD

TDO

VDD

VDDQ

VEXT

VSS

VSSQ

VTT

A21

A22

DNU

NF

I/O

Input

Input

Input

Input

Input

Input

I/O

Output

Output

Output

Supply

Supply

Supply

Supply

Supply

Supply

-

-

-

-

Data input: The DQ signals form the data bus. During READ commands, the data is referenced to both

edges of QK*. During WRITE commands, the data is sampled at both edges of DK.

Input data clock: DK* and DK*# are the differential input data clocks. All input data is referenced to

both edges of DK*. DK*# is ideally 180 degrees out of phase with DK*. For the x36 device, DQ0–DQ17

are referenced to DK0 and DK0# and DQ18–DQ35 are referenced to DK1 and DK1#. For the x9 and x18

devices, all DQ* are referenced to DK and DK#. All DK* and DK*# pins must always be supplied to the

device.

Input data mask: The DM signal is the input mask signal for WRITE data. Input data is masked when DM

is sampled HIGH. DM is sampled on both edges of DK (DK1 for the x36 configuration). Tie signal to

ground if not used.

IEEE 1149.1 clock input: This ball must be tied to VSS if the JTAG function is not used.

IEEE 1149.1 test inputs: These balls may be left as no connects if the JTAG function is not used.

Command inputs: Sampled at the positive edge of CK, WE# and REF# define (together with CS#) the

command to be executed.

Input reference voltage: Nominally VDDQ/2. Provides a reference voltage for the input buffers.

External impedance (25–60Ω): This signal is used to tune the device outputs to the system data bus

impedance. DQ output impedance is set to 0.2 × RQ, where RQ is a resistor from this signal to ground.

Connecting ZQ to GND invokes the minimum impedance mode.

Output data clocks: QK* and QK*# are opposite polarity, output data clocks. They are free running, and

during READs, are edge-aligned with data output from the memory. QK*# is ideally 180 degrees out of

phase with QK*. For the x36 device, QK0 and QK0# are aligned with DQ0-DQ17, and QK1 and QK1# are

aligned with DQ18-DQ35. For the x18 device, QK0 and QK0# are aligned with DQ0-DQ8, while QK1 and

QK1# are aligned with Q9-Q17. For the x9 device, all DQs are aligned with QK0 and QK0#.

Data valid: The QVLD pin indicates valid output data. QVLD is edge-aligned with QK* and QK*#.

IEEE 1149.1 test output: JTAG output. This ball may be left as no connect if the JTAG function is not

used.

Power supply: Nominally, 1.8V.

DQ power supply: Nominally, 1.5V or 1.8V. Isolated on the device for improved noise immunity.

Power supply: Nominally, 2.5V.

Ground.

DQ ground: Isolated on the device for improved noise immunity.

Power supply: Isolated termination supply. Nominally, VDDQ/2.

Reserved for future use: This signal is internally connected.

Reserved for future use: This signal is not connected and can be connected to ground.

Do not use: These balls may be connected to ground. Note that if ODT is enabled, these pins are High-Z.

No function: These balls can be connected to ground.

Integrated Silicon Solution, Inc. – www.issi.com –

Rev. 00F, 06/20/2012

5

5 Page

IS49NLC93200,IS49NLC18160,IS49NLC36800

4. AC timing and IDD tests may use a VIL-to-VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or the crossing point for

CK/CK#), and parameters specifications are tested for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals

used to test the device is 2V/ns in the range between VIL(AC) and VIH(AC).

5. The AC and DC input level specifications are as defined in the HSTL Standard (i.e. the receiver will effectively switch as a result of the signal crossing the AC input

level, and will remain in that state as long as the signal does not ring back above[below] the DC input LOW[HIGH] level).

6. The CK/CK# input reference level (for timing referenced to CK/CK#) is the point at which CK and CK# cross. The input reference level for signal other than CK/CK#

is VREF.

7. CK and CK# input slew rate must be ≥ 2V/ns (≥ 4V/ns if measured differentially).

8. VID is the magnitude of the difference between the input level on CK and input level on CK#.

9. The value of VIX is expected to equal VDDQ/2 of the transmitting device and must track variations in the DC level of the same.

10. CK and CK# must cross within the region.

11. CK and CK# must meet at least VID(DC) (MIN.) when static and centered on VDDQ/2.

12. Minimum peak-to-peak swing.

Integrated Silicon Solution, Inc. – www.issi.com –

Rev. 00F, 06/20/2012

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IS49NLC36800.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS49NLC36800 | Common I/O RLDRAM 2 Memory | Integrated Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |