|

|

PDF S25FS128S Data sheet ( Hoja de datos )

| Número de pieza | S25FS128S | |

| Descripción | Serial Peripheral Interface | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S25FS128S (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S25FS128S

S25FS256S

1.8 V, Serial Peripheral Interface with

Multi-I/O, MirrorBit® Non-Volatile Flash

Features

Density

– S25FS128S-128 Mbits (16 Mbytes)

– S25FS256S-256 Mbits (32 Mbytes)

Serial Peripheral Interface (SPI)

– SPI Clock polarity and phase modes 0 and 3

– Double Data Rate (DDR) option

– Extended Addressing: 24- or 32-bit address options

– Serial Command subset and footprint compatible with S25FL-A,

S25FL-K, S25FL-P, and S25FL-S SPI families

– Multi I/O Command subset and footprint compatible with S25FL-P,

and S25FL-S SPI families

Read

– Commands: Normal, Fast, Dual I/O, Quad I/O, DDR Quad I/O

– Modes: Burst Wrap, Continuous (XIP), QPI

– Serial Flash Discoverable Parameters (SFDP) and Common

Flash Interface (CFI), for configuration information

Program

– 256- or 512-byte Page Programming buffer

– Program suspend and resume

Erase

– Hybrid sector option

– Physical set of eight 4-kbyte sectors and one 32-kbyte sector at

the top or bottom of address space with all remaining sectors of 64

kbytes

– Uniform sector option

– Uniform 64-kbyte or 256-kbyte blocks for software compatibility

with higher density and future devices

– Erase suspend and resume

– Erase status evaluation

– 100,000 Program-Erase Cycles on any sector, minimum

– 20 Year Data Retention, typical

Security Features

– One-Time Program (OTP) array of 1024 bytes

– Block Protection:

– Status Register bits to control protection against program or erase

of a contiguous range of sectors

– Hardware and software control options

– Advanced Sector Protection (ASP)

– Individual sector protection controlled by boot code or password

– Option for password control of read access

Technology

– Spansion 65 nm MirrorBit Technology with Eclipse™ Architecture

Supply Voltage

– 1.7V to 2.0V

Temperature Range

– Industrial (0°C to +85°C)

– Industrial Plus (–40°C to +105°C)

Packages (All Pb-Free)

– 8-lead SOIC 208 mil (SOC008) - FS128S only

– WSON 6x5 mm (WND008) - FS128S only

– WSON 6x8 mm (WNH008) - FS256S only

– 16-lead SOIC 300 mil (SO3016- FS256S only)

– BGA-24 6x8 mm

– 5x5 ball (FAB024) footprint

– 4x6 ball (FAC024) footprint

– Known Good Die, and Known Tested Die

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 002-00368 Rev. *G

• San Jose, CA 95134-1709 • 408-943-2600

Revised February 02, 2016

1 page

S25FS128S

S25FS256S

2.2 Migration Notes

2.2.1 Features Comparison

The S25FS-S family is command subset and footprint compatible with prior generation FL-S, FL-K, and FL-P families. However, the

power supply and interface voltages are nominal 1.8 V.

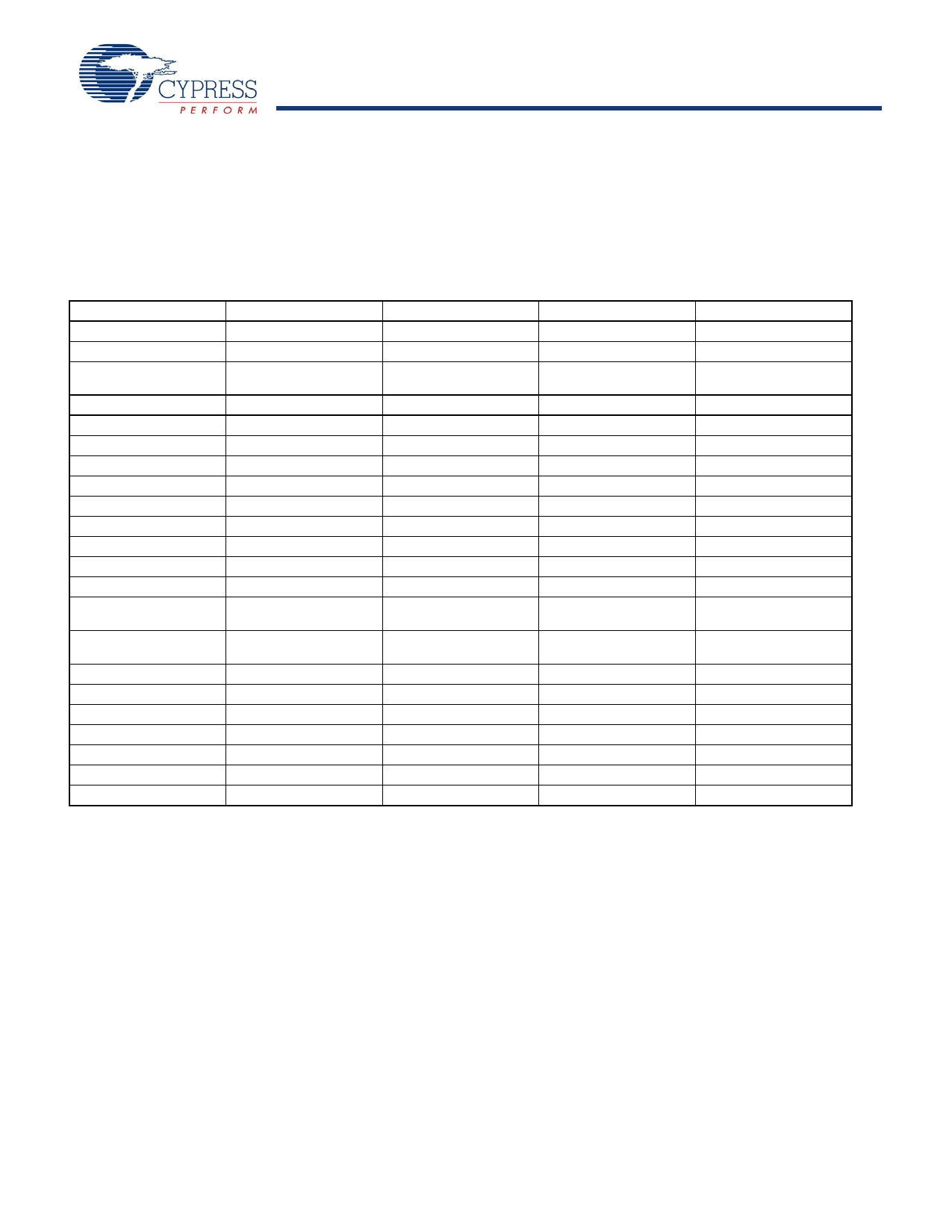

Spansion SPI Families Comparison

Parameter

Technology Node

Architecture

Density

Bus Width

Supply Voltage

Normal Read Speed (SDR)

Fast Read Speed (SDR)

Dual Read Speed (SDR)

Quad Read Speed (SDR)

Quad Read Speed (DDR)

Program Buffer Size

Erase Sector Size

Parameter Sector Size

FS-S

65 nm

MirrorBit Eclipse

128 Mb, 256 Mb

x1, x2, x4

1.7 V–2.0 V

6 MB/s (50 MHz)

16.5 MB/s (133 MHz)

33 MB/s (133 MHz)

66 MB/s (133 MHz)

80 MB/s (80 MHz)

256B / 512B

64 kB / 256 kB

4 kB (option)

FL-S

65 nm

MirrorBit Eclipse

128 Mb, 256 Mb, 512 Mb, 1

Gb

x1, x2, x4

2.7 V–3.6 V / 1.65 V–3.6 V VIO

6 MB/s (50 MHz)

17 MB/s (133 MHz)

26 MB/s (104 MHz)

52 MB/s (104 MHz)

80 MB/s (80 MHz)

256B / 512B

64 kB / 256 kB

4 kB (option)

Sector Erase Rate (typ.)

500 kB/s

500 kB/s

Page Programming Rate (typ.)

OTP

Advanced Sector Protection

Auto Boot Mode

Erase Suspend/Resume

Program Suspend/Resume

Deep Power-Down

Operating Temperature

0.71 MB/s (256B)

1.08 MB/s (512B)

1024B

Yes

No

Yes

Yes

Yes

–40 °C to +85 °C / +105 °C

1.2 MB/s (256B)

1.5 MB/s (512B)

1024B

Yes

Yes

Yes

Yes

No

–40 °C to +85 °C / +105 °C

FL-K

90 nm

Floating Gate

4 Mb - 128 Mb

x1, x2, x4

2.7 V–3.6 V

6 MB/s (50 MHz)

13 MB/s (104 MHz)

26 MB/s (104 MHz)

52 MB/s (104 MHz)

256B

4 kB / 32 kB / 64 kB

4 kB

136 kB/s (4 kB)

437 kB/s (64 kB)

365 kB/s

768B (3x256B)

No

No

Yes

Yes

Yes

–40 °C to +85 °C

FL-P

90 nm

MirrorBit

32 Mb - 256 Mb

x1, x2, x4

2.7 V–3.6 V

6 MB/s (40 MHz)

13 MB/s (104 MHz)

20 MB/s (80 MHz)

40 MB/s (80 MHz)

256B

64 kB / 256 kB

4 kB

130 kB/s

170 kB/s

506B

No

No

No

No

Yes

–40 °C to +85 °C / +105 °C

Notes:

1. The 256B program page option only for 128-Mb and 256-Mb density FL-S devices.

2. The FL-P column indicates FL129P MIO SPI device (for 128-Mb density), FL128P does not support MIO, OTP, or 4-kB sectors.

3. 64-kB Sector Erase option only for 128-Mb/256-Mb density FL-P, FL-S and FS-S devices.

4. The FL-K family devices can erase 4-kB sectors in groups of 32 kB or 64 kB.

5. 512-Mb/1-Gb FL-S devices support 256-kB sector only.

6. Only 128-Mb/256-Mb density FL-S devices have 4-kB parameter sector option.

7. Refer to individual data sheets for further details.

2.2.2 Known Differences from Prior Generations

2.2.2.1 Error Reporting

FL-K and FL-P memories either do not have error status bits or do not set them if program or erase is attempted on a protected

sector. The FS-S and FL-S families do have error reporting status bits for program and erase operations. These can be set when

there is an internal failure to program or erase, or when there is an attempt to program or erase a protected sector. In these cases

the program or erase operation did not complete as requested by the command. The P_ERR or E_ERR bits and the WIP bit will be

set to and remain 1 in SR1V. The clear Status Register command must be sent to clear the errors and return the device to standby

state.

Document Number: 002-00368 Rev. *G

Page 5 of 153

5 Page

S25FS128S

S25FS256S

The WP# function is not available when the Quad Mode is enabled (CR1V[1] = 1). The WP# function is replaced by IO2 for input and

output during Quad Mode for receiving addresses, and data to be programmed (values are latched on rising edge of the SCK signal)

as well as shifting out data (on the falling edge of SCK, in SDR commands, and on every edge of SCK, in DDR commands).

WP# has an internal pull-up resistance; when unconnected, WP# is at VIH and may be left unconnected in the host system if not

used for Quad Mode or protection.

3.8 IO3 / RESET#

IO3 is used for input and output during Quad Mode (CR1V[1] = 1) for receiving addresses, and data to be programmed (values are

latched on rising edge of the SCK signal) as well as shifting out data (on the falling edge of SCK, in SDR commands, and on every

edge of SCK, in DDR commands).

The IO3 / RESET# signal may also be used to initiate the hardware reset function when the reset feature is enabled by writing

Configuration Register 2 non-volatile bit 5 (CR2V[5] = 1). The input is only treated as RESET# when the device is not in Quad-I/O

mode, CR1V[1] = 0, or when CS# is high. When Quad I/O mode is in use, CR1V[1]=1, and the device is selected with CS# low, the

IO3 / RESET# is used only as IO3 for information transfer. When CS# is high, the IO3 / RESET# is not in use for information transfer

and is used as the RESET# input. By conditioning the reset operation on CS# high during Quad Mode, the reset function remains

available during Quad Mode.

When the system enters a reset condition, the CS# signal must be driven high as part of the reset process and the IO3 / RESET#

signal is driven low. When CS# goes high the IO3 / RESET# input transitions from being IO3 to being the RESET# input. The reset

condition is then detected when CS# remains high and the IO3 / RESET# signal remains low for tRP. If a reset is not intended, the

system is required to actively drive IO3 / Reset# to high along with CS# being driven high at the end of a transfer of data to the

memory. Following transfers of data to the host system, the memory will drive IO3 high during tCS. This will ensure that IO3 / Reset

is not left floating or being pulled slowly to high by the internal or an external passive pull-up. Thus, an unintended reset is not

triggered by the IO3 / RESET# not being recognized as high before the end of tRP.

The IO3 / RESET# signal is unused when the reset feature is disabled (CR2V[5] = 0).

The IO3 / RESET# signal has an internal pull-up resistor and may be left unconnected in the host system if not used for Quad Mode

or the reset function. The internal pull-up will hold IO3 / RESET high after the host system has actively driven the signal high and

then stops driving the signal.

Note that IO3 / RESET# cannot be shared by more than one SPI-MIO memory if any of them are operating in Quad I/O mode as IO3

being driven to or from one selected memory may look like a reset signal to a second non-selected memory sharing the same

IO3 / RESET# signal.

3.9 Voltage Supply (VDD)

VDD is the voltage source for all device internal logic. It is the single voltage used for all device internal functions including read,

program, and erase.

3.10 Supply and Signal Ground (VSS)

VSS is the common voltage drain and ground reference for the device core, input signal receivers, and output drivers.

3.11 Not Connected (NC)

No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The

connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB).

3.12 Reserved for Future Use (RFU)

No device internal signal is currently connected to the package connector but there is potential future use of the connector. It is

recommended to not use RFU connectors for PCB routing channels so that the PCB may take advantage of future enhanced

features in compatible footprint devices.

Document Number: 002-00368 Rev. *G

Page 11 of 153

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S25FS128S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S25FS128S | MirrorBit Flash Non-Volatile Memory | SPANSION |

| S25FS128S | Serial Peripheral Interface | Cypress Semiconductor |

| S25FS128SAGBHI203 | MirrorBit Flash Non-Volatile Memory | SPANSION |

| S25FS128SAGBHI300 | MirrorBit Flash Non-Volatile Memory | SPANSION |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |