|

|

PDF NB3H60113G Data sheet ( Hoja de datos )

| Número de pieza | NB3H60113G | |

| Descripción | 3.3V / 2.5V Programmable OmniClock Generator | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3H60113G (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

NB3H60113G

3.3 V / 2.5 V Programmable

OmniClock Generator

with Single Ended (LVCMOS/LVTTL) and

Differential (LVPECL/LVDS/ HCSL/CML)

Outputs

www.onsemi.com

The NB3H60113G, which is a member of the OmniClock family, is

a one−time programmable (OTP), low power PLL−based clock

generator that supports any output frequency from 8 kHz to 200 MHz.

The device accepts fundamental mode parallel resonant crystal or a

single ended (LVCMOS/LVTTL) reference clock as input. It

WDFN8

CASE 511AT

generates either three single ended (LVCMOS/LVTTL) outputs, or

one single ended output and one differential

MARKING DIAGRAM

(LVPECL/LVDS/HCSL/CML) output. The output signals can be

modulated using the spread spectrum feature of the PLL

(programmable spread spectrum type, deviation and rate) for

applications demanding low electromagnetic interference (EMI).

Using the PLL bypass mode, it is possible to get a copy of the input

clock on any or all of the outputs. The device can be powered down

using the Power Down pin (PD#). It is possible to program the internal

input crystal load capacitance and the output drive current provided by

1

H0MG

G

H0 = Specific Device Code

M = Date Code

G = Pb−Free Device

(Note: Microdot may be in either location)

the device. The device also has automatic gain control (crystal power

limiting) circuitry which avoids the device overdriving the external

ORDERING INFORMATION

crystal.

See detailed ordering and shipping information on page 21 of

this data sheet.

Features

• Member of the OmniClock Family of Programmable Clock

Generators

• Operating Power Supply: 3.3 V ± 10%, 2.5 V ± 10%

• I/O Standards

♦ Inputs: LVCMOS/LVTTL, Fundamental Mode

Crystal

♦ Outputs: LVCMOS/LVTTL

♦ Outputs: LVPECL, LVDS, CML and HCSL

• 3 Programmable Single Ended (LVCMOS/LVTTL)

Outputs from 8 kHz to 200 MHz

• 1 Programmable Differential Clock Output up to

200 MHz

• Input Frequency Range

• Power Saving mode through Power Down Pin

• Programmable PLL Bypass Mode

• Programmable Output Inversion

• Programming and Evaluation Kit for Field

Programming and Quick Evaluation

• Temperature Range −40°C to 85°C

• Packaged in 8−Pin WDFN

• These are Pb−Free Devices

♦ Crystal: 3 MHz to 50 MHz

♦ Reference Clock: 3 MHz to 200 MHz

• Configurable Spread Spectrum Frequency Modulation

Parameters (Type, Deviation, Rate)

• Programmable Internal Crystal Load Capacitors

• Programmable Output Drive Current for Single Ended

Outputs

Typical Applications

• eBooks and Media Players

• Smart Wearables, Portable Medical and Industrial

Equipment

• Set Top Boxes, Printers, Digital Cameras and

Camcorders

© Semiconductor Components Industries, LLC, 2016

January, 2016 − Rev. 2

1

Publication Order Number:

NB3H60113G/D

1 page

NB3H60113G

Programmable Clock Outputs

Output Type and Frequency

The NB3H60113G provides three independent single

ended LVCMOS/LVTTL outputs, or one single ended

LVCMOS/LVTTL output and one LVPECL/LVDS/HCSL/

CML differential output. The device supports any single

ended output or differential output frequency from 8 kHz up

to 200 MHz with or without frequency modulation. It should

be noted that certain combinations of output frequencies and

spread spectrum configurations may not be recommended

for optimal and stable operation.

For differential clocking, CLK0 and CLK1 can be

configured as LVPECL, LVDS, HCSL or CML. Refer to the

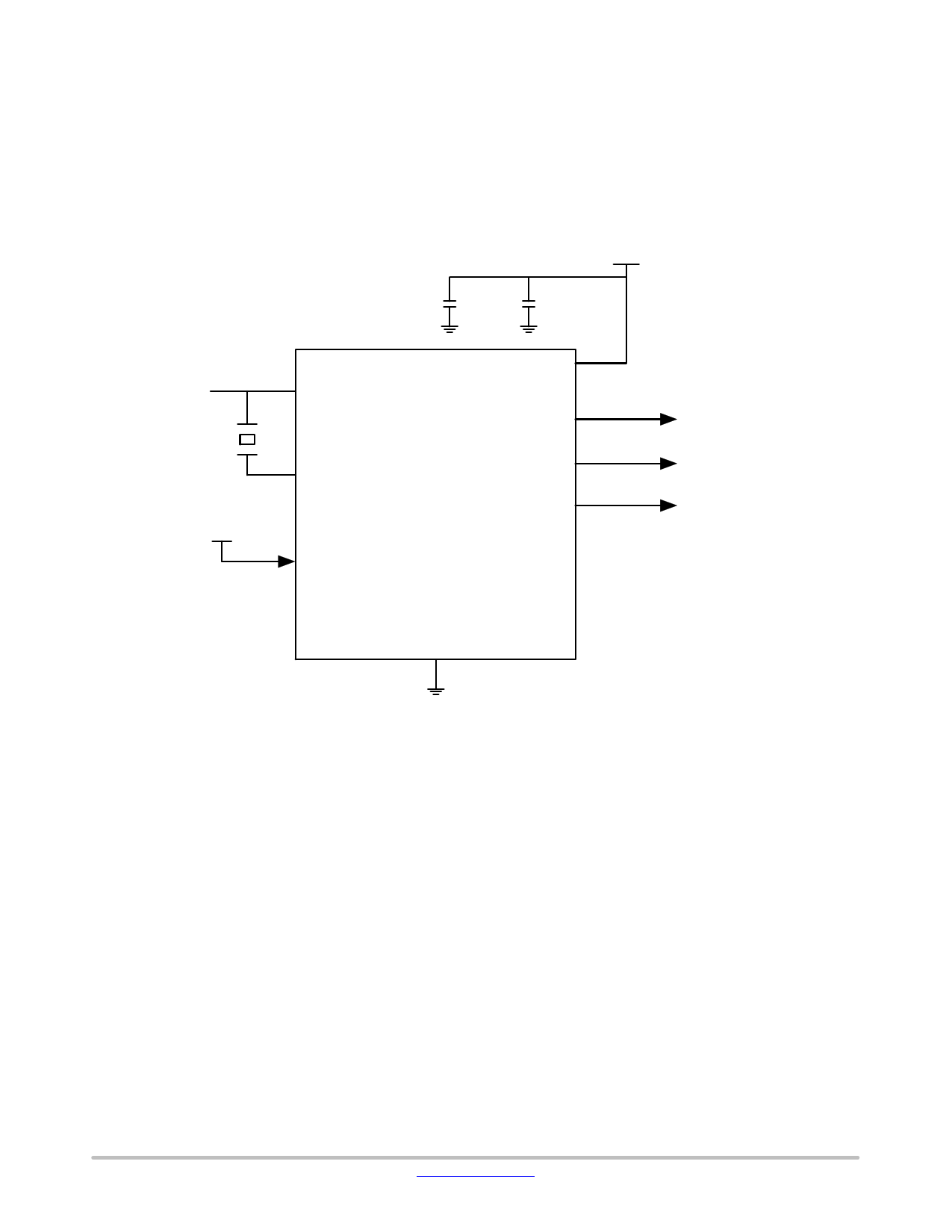

Application Schematic in Figure 4.

3.3 V / 2.5V

0.1 mF

0.01 mF

Crystal or

Reference

Clock Input

VDD

XIN / CLKIN

XOUT

PD#

NB3H60113G

VDD

CLK2

CLK1

CLK0

Single Ended Clock

Differential Clock

LVPECL/LVDS/HCSL/CML

GND

Figure 4. Application Setup for Differential Output Configuration

Programmable Output Drive

The drive strength or output current of each of the

LVCMOS clock outputs is programmable. For VDD of 3.3 V

and 2.5 V four distinct levels of LVCMOS output drive

strengths can be selected as mentioned in the DC Electrical

Characteristics. This feature provides further load drive and

signal conditioning as per the application requirement.

PLL BYPASS Mode

PLL Bypass mode can be used to buffer the input clock on

any of the outputs or all of the outputs. Any of the clock

outputs can be programmed to generate a copy of the input

clock.

Output Inversion

All output clocks of the NB3H60113G can be

phase inverted relative to each other. This feature can also be

used in conjunction with the PLL Bypass mode.

Spread Spectrum Frequency Modulation

Spread spectrum is a technique using frequency

modulation to achieve lower peak electromagnetic

interference (EMI). It is an elegant solution compared to

techniques of filtering and shielding. The NB3H60113G

modulates the output of its PLL in order to “spread” the

bandwidth of the synthesized clock, decreasing the peak

amplitude at the center frequency and at the frequency’s

harmonics. This results in significantly lower system EMI

compared to the typical narrow band signal produced by

oscillators and most clock generators. Lowering EMI by

increasing a signal’s bandwidth is called ‘spread spectrum

modulation’.

www.onsemi.com

5

5 Page

NB3H60113G

Table 9. AC ELECTRICAL CHARACTERISTICS

(VDD = 3.3 V ± 10%; 2.5 V ± 10%, GND = 0 V, TA = −40°C to 85°C, Notes 18, 19 and 22)

Symbol

Parameter

Conditions

Min Typ

fout Single Ended Output Frequency

0.008

fMOD

SS

Spread Spectrum Modulation Rate

Percent Spread Spectrum

(deviation from nominal frequency)

fclkin ≥ 6.75 MHz

Down Spread

Center Spread

30

0

0

SSstep

Percent Spread Spectrum change

step size

Down Spread step size

Center Spread step size

0.25

0.125

SSCRED Spectral Reduction, 3rd harmonic

@SS=−0.5%, fout = 100 MHz, fclkin =

25 MHz crystal, RES BW at 30 kHz, All

Output Types

−10

tPU

Stabilization time from Power−up

VDD = 3.3 V, 2.5 V with Frequency

Modulation

3.0

tPD Stabilization time from Power Down Time from falling edge on PD# pin to

tri−stated outputs (Asynchronous)

3.0

Eppm

Synthesis Error

Configuration Dependent

0

SINGLE ENDED OUTPUTS (VDD = 3.3 V ±10%, 2.5 V ±10%; TA = −40°C to 85°C, Notes 18, 19 and 22)

tJITTER−3.3 V Period Jitter Peak−to−Peak

Configuration Dependent. 25 MHz xtal

input , fout = 100 MHz, SS off

(Notes 20, 22 and 24, see Figure 14)

100

Cycle−Cycle Peak Jitter

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off

(Notes 20, 22 and 24, see Figure 14)

100

tJITTER−2.5 V Period Jitter Peak−to−Peak

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off

(Notes 20, 22 and 24, see Figure 14)

100

Cycle−Cycle Peak Jitter

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off

(Notes 20, 22 and 24, see Figure 14)

100

tr / tf 3.3 V

Rise/Fall Time

Measured between 20% to 80% with

15 pF load, fout = 100 MHz,

VDD = VDDO = 3.3 V,

Max Drive

Min Drive

1

2

tr / tf 2.5 V

Rise/Fall Time

Measured between 20% to 80% with

15 pF load, fout = 100 MHz,

VDD = VDDO = 2.5 V,

Max Drive

Min Drive

1

2

tDC Output Clock Duty Cycle

VDD = 3.3 V, 2.5 V;

Duty Cycle of Ref clock is 50%

PLL Clock

Reference Clock

45

40

50

50

DIFFERENTIAL OUTPUT (CLK1, CLK0) (VDD = 3.3 V, ±10% 2.5 V ±10%; TA = −40°C to 85°C, Notes 18, 22 and 23)

tJITTER−3.3 V Period Jitter Peak−to−Peak

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off, CLK = OFF

(Notes 21, 22, and 24, see Figure 14)

100

Cycle−Cycle Peak to Peak Jitter

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off, CLK2 = OFF

(Notes 21, 22, and 24, see Figure 14)

100

tJITTER−2.5 V Period Jitter Peak−to−Peak

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off, CLK = OFF

(Notes 21, 22, and 24, see Figure 14)

100

Cycle−Cycle Peak to Peak Jitter

Configuration Dependent. 25 MHz xtal

input, fout = 100 MHz, SS off, CLK2 = OFF

(Notes 21, 22, and 24, see Figure 14)

100

Max

200

130

−4

±3

55

60

Unit

MHz

kHz

%

%

%

%

dB

ms

ms

ppm

ps

ps

ns

ns

%

ps

ps

ps

ps

www.onsemi.com

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet NB3H60113G.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3H60113G | 3.3V / 2.5V Programmable OmniClock Generator | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |