|

|

PDF ISL68200 Data sheet ( Hoja de datos )

| Número de pieza | ISL68200 | |

| Descripción | Single-Phase R4 Digital Hybrid PWM Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL68200 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATASHEET

SInintegglera-PtehdasDeriRve4r™, PDMigBituasl/HSyMbBriudsP/IW2CMaCnodnPtrFoMller with

ISL68200

The ISL68200 is a single-phase synchronous-buck PWM

controller featuring Intersil’s proprietary R4™ Technology. It

supports a wide 4.5V to 24V input voltage range and a wide

0.5V to 5.5V output range. Integrated LDOs provide controller

bias voltage, allowing for single supply operation. The

ISL68200 includes a PMBus/SMBus/I2C interface for device

configuration and telemetry (VIN, VOUT, IOUT and temperature)

and fault reporting.

Intersil’s proprietary R4™ control scheme has extremely fast

transient performance, accurately regulated frequency control

and all internal compensation. An efficiency enhancing PFM

mode can be enabled to greatly improve light-load efficiency.

The ISL68200’s series bus allows for easy R4™ loop

optimization, resulting in fast transient performance over a

wide range of applications, including all ceramic output filters.

Built-in MOSFET drivers minimize external components,

significantly reducing design complexity and board space,

while also lowering BOM cost. The 4A drive strength allows for

faster switching time, improving regulator efficiency. An

integrated high-side gate-to-source resistor helps avoid Miller

coupling shoot-through and improve system reliability.

The ISL68200 has four 8-bit configuration pins, which provide

very flexible configuration options (frequency, VOUT, R4™ gain,

etc.) without the need for built-in NVM memory. This results in

a design flow that closely matches traditional analog

controllers, while still offering the design flexibility and feature

set of a digital PMBus/SMBus/I2C interface. The ISL68200

also features remote voltage sensing and completely eliminates

any potential difference between remote and local grounds. This

improves regulation and protection accuracy. A precision enable

input is available to coordinate the start-up of the ISL68200 with

other voltage rails, especially useful for power sequencing.

Applications

• High efficiency and high density POL digital power

• FPGA, ASIC and memory supplies

• Datacenter: servers, storage systems

• Wired infrastructure: routers/switches/optical networking

• Wireless infrastructure: base station

Features

• Intersil’s proprietary R4™ Technology

- Linear control loop for optimal transient response

- Variable frequency and duty cycle control during load

transient for fastest possible response

- Inherent voltage feed-forward for wide range input

• Input voltage range: 4.5V to 24V

• Output voltage range: 0.5V to 5.5V

• ±0.5% DAC accuracy with remote sense

• Support all ceramic solutions

• Integrated LDOs for single input rail solution

• SMBus/PMBus/I2C compatible, up to 1.25MHz

• 256 boot-up voltage levels with a configuration pin

• Eight switching frequency options from 300kHz to 1.5MHz

• PFM operation option for improved light-load efficiency

• Start-up into precharged load

• Precision enable input to set higher input UVLO and power

sequence as well as fault reset

• Power-good monitor for soft-start and fault detection

• Comprehensive fault protection for high system reliability

- Over-temperature protection

- Output overcurrent and short-circuit protection

- Output overvoltage and undervoltage protection

- Open remote sense protection

- Integrated high-side gate-to-source resistor to prevent self

turn-on due to high input bus dv/dt

• Integrated power MOSFETs 4A drivers with adaptive

shoot-through protection and bootstrap function

• Compatible with Intersil’s PowerNavigator™ software

Related Literature

UG067, “ISL68200DEMO1Z Demonstration Board User Guide”

PART

NUMBER

ISL68200

ISL68201

INTEGRATED

DRIVER

Yes

No

TABLE 1. SINGLE-PHASE R4™ DIGITAL HYBRID PWM CONTROLLER OPTIONS

PWM

OUTPUT

PMBus/SMBus/I2C

INTERFACE

COMPATIBLE DEVICES

No Yes Discrete MOSFETs or Dual Channel MOSFETs

Yes Yes Intersil Power Stages: ISL99140

Intersil Drivers: ISL6596, ISL6609, ISL6627, ISL6622, ISL6208

March 7, 2016

FN8705.1

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC 2016. All Rights Reserved.

Intersil (and design), R3 Technology, R4 Technology and PowerNavigator are trademarks owned by Intersil Corporation or

one of its subsidiaries. All other trademarks mentioned are the property of their respective owners.

1 page

Pin Configuration

ISL68200

ISL68200

(24 LD 4x4 QFN)

TOP VIEW

24 23 22 21 20 19

EN 1

18 PROG1

VIN 2

17 PROG2

7VLDO 3

VCC 4

25

GND PAD

16 PROG3

15 PROG4

SCL 5

14 IOUT

SALERT 6

13 NTC

7 8 9 10 11 12

Functional Pin Descriptions

PIN NUMBER SYMBOL

DESCRIPTION

1 EN Precision Enable input. Pulling EN above the rising threshold voltage initiates the soft-start sequence, while pulling EN below the

failing threshold voltage suspends the Voltage Regulator (VR) operation.

2 VIN Input voltage pin for R4™ loop and LDOs (5V and 7V). Place a high quality low ESR ceramic capacitor (1.0μF, X7R) in close

proximity to the pin. External series resistor is not advised.

3 7VLDO 7V LDO from VIN is used to bias current sensing amplifier. Place a high quality low ESR ceramic capacitor (1.0μF, X7R, 10V+)

in close proximity to the pin.

4 VCC Logic bias supply that should be connected to PVCC rail externally. Place a high quality low ESR ceramic capacitor (1.0μF,

X7R) from this pin to GND.

5 SCL Synchronous clock signal input of SMBus/PMBus/I2C.

6 SALERT Output pin for transferring the active low signal driven asynchronously from the VR controller to SMBus/PMBus.

7 SDA I/O pin for transferring data signals between SMBus/PMBus/I2C host and VR controller.

8 PGOOD Open-drain indicator output.

9 RGND This pin monitors the negative rail of regulator output. Connect to ground at point of regulation.

10 VSEN This pin monitors the positive rail of regulator output. Connect to point of regulation

11 CSRTN This pin monitors the negative flow of output current for overcurrent protection and telemetry.

12 CSEN This pin monitors the positive flow of output current with a series resistor and for overcurrent protection and telemetry. The

series resistor sets the current gain and should be within 40Ωand 3.5kΩ.

13 NTC Input pin for the temperature measurement. Connect this pin through an NTC thermistor (10kΩ, ~ 3380) and a decoupling

capacitor (~0.1μF) to GND and a resistor (1.54kΩ)to VCC of the controller. The voltage at this pin is inversely proportional to

the VR temperature.

14 IOUT Output current monitor pin. An external resistor sets the gain and an external capacitor provides the averaging function; an

external pull-up resistor to VCC is recommended to calibrate the no load offset. See “IOUT Calibration” on page 19.

15 PROG4 Programming pin for Modulator (R4™) RR impedance and output slew rate during Soft-Start (SS) and Dynamic VID (DVID).

It also sets AV gain multiplier to 1x or 2x and determines the AV gain on PROG3.

16 PROG3 Programming pin for ultrasonic PFM operation, fault behavior, switching frequency and R4™ (AV) control loop gain.

Submit Document Feedback

5

FN8705.1

March 7, 2016

5 Page

ISL68200

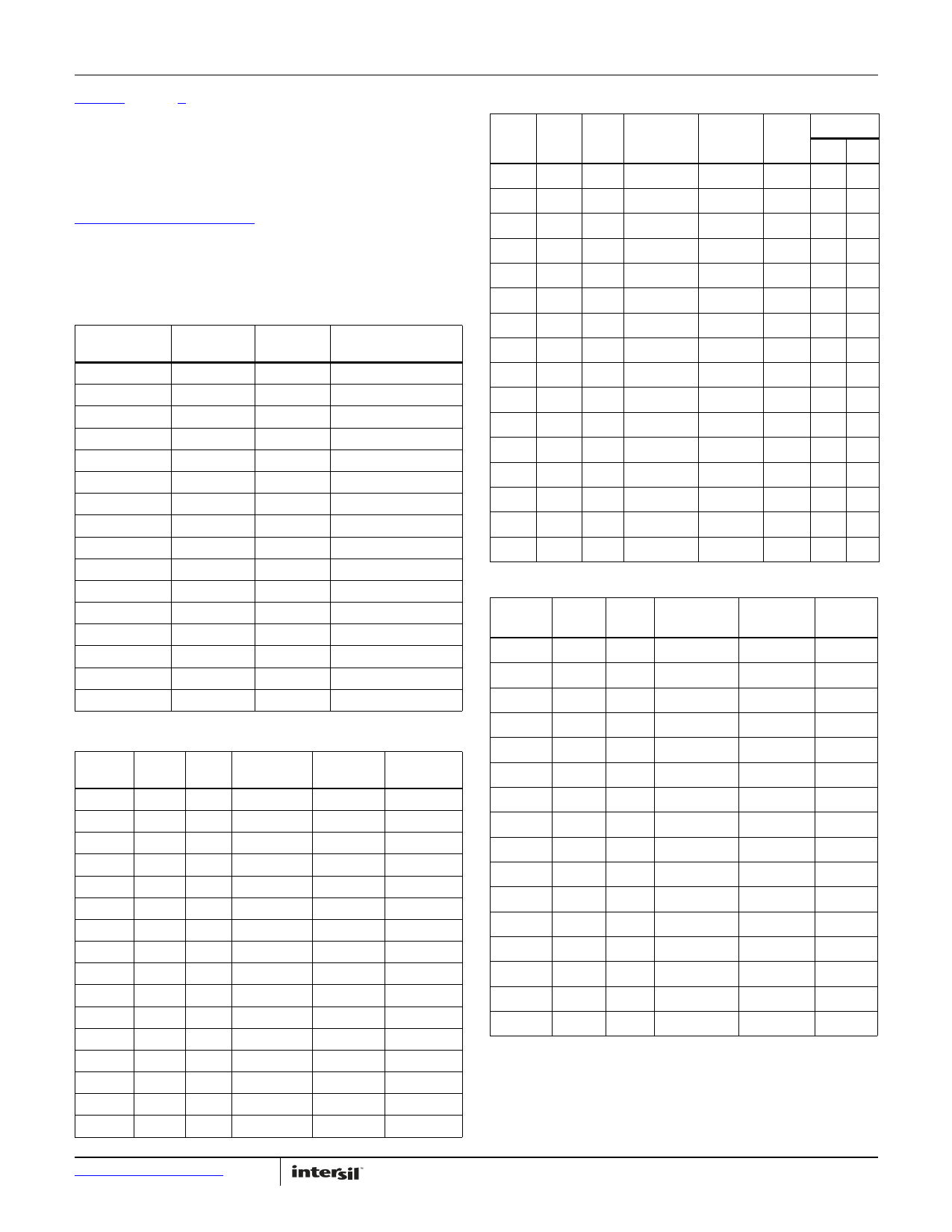

Tables 3 through 6 show the RUP and RDW values of each pin for

a specific system design with some tie-high and tie-low options,

which are for easy programming with reduced resistors and can

be used to validate the regulator operation during In-Circuit Test

(ICT) for 0V boot-up voltage option. Additional options are

available using Intersil’s PowerNavigator™ or Resistor Reader

calculator, please contact Intersil Application support at

www.intersil.com/en/support. DATA for corresponding registers

can be read out via series bus command (DC to DF). Note that

more options are in PowerNavigator™ GUI or Resistor Reader

calculator and the case of 10kΩ tie-high or tie-low is equivalent

0Ω tie-high or tie-low.

TABLE 3. PROG 1 RESISTOR READER EXAMPLE

PROG1 (DC)

RUP

(kΩ)

RDW

(kΩ)

VOUT

(V)

00h

Open

0

0.797

20h

Open

20

0.852

40h

Open

34.8

0.898

60h

Open

52.3

0.953

80h

Open

75

1.000

A0h

Open

105

1.047

C0h

Open

147

1.102

E0h

Open

499

1.203

1Fh 0 Open 1.352

3Fh 20 Open 1.500

5Fh

34.8

Open

1.797

7Fh

52.3

Open

2.500

9Fh 75 Open 3.000

BFh 105 Open

3.297

DFh 147 Open

5.000

FFh 499 Open

0.000

PROG2

(DD)

00h

20h

40h

60h

80h

A0h

C0h

E0h

1Fh

3Fh

5Fh

7Fh

9Fh

BFh

DFh

FFh

TABLE 4. PROG 2 RESISTOR READER EXAMPLE

RUP RDW

(kΩ) (kΩ) PWM/PFM

TEMP

COMP

PM_ADDR

(7-BIT)

Open

0

Enabled

30

60h

Open 20

Enabled

15

60h

Open 34.8 Enabled

5

60h

Open 52.3 Enabled

OFF

60h

Open 75

Disabled

30

60h

Open 105 Disabled

15

60h

Open 147 Disabled

5

60h

Open 499 Disabled

OFF

60h

0 Open Enabled

30

7F

20 Open Enabled

15

7F

34.8 Open Enabled

5

7F

52.3 Open Enabled

OFF

7F

75 Open Disabled

30

7F

105 Open Disabled

15

7F

147 Open Disabled

5

7F

499 Open Disabled

OFF

7F

TABLE 5. PROG 3 RESISTOR READER EXAMPLE

PROG3 RUP

(DE) (kΩ)

RDW ULTRASONIC FAULT

fSW

(kΩ) PFM BEHAVIOR (kHz)

R4 GAIN

1x 2x

00h Open 0

Disabled

Retry

300 42 84

20h Open 21.5 Disabled

Retry

700 42 84

40h Open 34.8 Disabled

Latch

300 42 84

60h Open 52.3 Disabled

Latch

700 42 84

80h Open 75 Enabled

Retry

300 42 84

A0h Open 105 Enabled

Retry

700 42 84

C0h Open 147 Enabled

Latch 300 42 84

E0h Open 499 Enabled

Latch 700 42 84

1Fh 0 Open Disabled Retry 600 1 2

3Fh 21.5 Open Disabled

Retry 1500 1 2

5Fh 34.8 Open Disabled

Latch

600 1 2

7Fh 52.3 Open Disabled

Latch 1500 1 2

9Fh 75 Open Enabled

Retry

600 1 2

BFh 105 Open Enabled

Retry 1500 1 2

DFh 147 Open Enabled

Latch 600 1 2

FFh 499 Open Enabled

Latch 1500 1 2

TABLE 6. PROG 4 RESISTOR READER EXAMPLE

PROG4 RUP RDW

(DF (kΩ) (kΩ)

SS RATE

(mV/µs)

RR

(kΩ AVMLTI

00h Open 0

1.25

200

1

20h Open 20

2.5

200 1

40h Open 34.8

5

200 1

60h Open 52.3

10

200 1

80h Open 75

0.078

200

1

A0h Open 105

0.157

200

1

C0h Open 147

0.315

200

1

E0h Open 499

0.625

200

1

1Fh

0 Open

1.25

800

2

3Fh 20 Open

2.5

800 2

5Fh 34.8 Open

5

800 2

7Fh 52.3 Open

10

800 2

9Fh

75 Open

0.078

800

2

BFh 105 Open 0.157 800 2

DFh 147 Open 0.315 800 2

FFh 499 Open 0.625 800 2

Submit Document Feedback 11

FN8705.1

March 7, 2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISL68200.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL68200 | Single-Phase R4 Digital Hybrid PWM Controller | Intersil Corporation |

| ISL68201 | Single-Phase R4 Digital Hybrid PWM Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |