|

|

PDF ISL78229 Data sheet ( Hoja de datos )

| Número de pieza | ISL78229 | |

| Descripción | 2-Phase Boost Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL78229 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATASHEET

2-Phase Boost Controller with Drivers and I2C/PMBus™

ISL78229

The ISL78229 is an automotive grade (AEC-Q100 Grade 1),

2-phase 55V synchronous boost controller intended to simplify

the design of high power boost applications. It integrates

strong half-bridge drivers, an analog/digital tracking input,

comprehensive protection functions and a PMBus™ interface

for added control and telemetry.

ISL78229 enables a simple, modular design for systems

requiring power and thermal scalability. It offers peak-current

mode control for fast line response and simple compensation.

Its synchronous 2-phase architecture enables it to support

higher current while reducing the size of input and output

capacitors. The integrated drivers feature programmable

adaptive dead time control offering flexibility in power stage

design. ISL78229 offers a 90°output clock and supports 1-,

2- and 4-phases.

ISL78229 offers a highly robust solution for the most

demanding environments. Its unique soft-start control

prevents large negative current even in extreme cases, such as

a restart under high output prebias on high volume

capacitances. It also offers two levels of cycle-by-cycle

overcurrent protection, average current limiting, input OVP,

output UVP/OVP and internal OTP. A thermistor input is

provided for external OTP for the power-stage elements. In the

event of a fault, the ISL78229 offers individually

programmable latch-off or hiccup recovery for each fault type.

Also integrated are several functions that ease system design.

A unique tracking input is available that can control the output

voltage, allowing it to track either a digital duty cycle (PWM)

signal or an analog reference. ISL78229 provides input

average current limiting so the system can deliver transient

bursts of high load current while limiting the average current to

avoid overheating. Finally, the ISL78229 PMBus™ interface

provides fault reporting, telemetry and system control to

support functional safety qualification.

Features

• Input/output voltage range: 5V to 55V, withstands 60V

transients

• Supports synchronous or standard boost topology

• Peak current mode control with adjustable slope

compensation

• Secondary average current control loop

• Integrated 5V 2A sourcing/3A sinking N-channel MOSFET

drivers

• Switching frequency: 50kHz to 1.1MHz per phase

• External synchronization

• Programmable minimum duty cycle

• Programmable adaptive dead time control

• Optional diode emulation and phase dropping

• PWM and analog track function

• Forced PWM operation with negative current limiting and

protection

• Comprehensive protection/fault reporting

• Selectable hiccup or latch-off fault response

• I2C/PMBus™ compatible digital interface

• AEC-Q100 qualified, Grade 1: -40°C to +125°C

• 6mmx6mm 40 Ld WFQFN (Wettable Flank QFN) package

Applications

• Automotive power system (e.g., 12V to 24V, 12V to 48V, etc.)

- Trunk audio amplifier

- Start-stop system

- Automotive boost applications

• Industrial and telecommunication power supplies

VIN

EN_IC

PMBus

POWER-GOOD

CLOCK_OUT

VIN

EN BOOT1

NTC

UG1

PH1

LG1

SDA

SCL

SALERT

PGOOD

ISEN1N

ISEN1P

ISL78229

BOOT2

TRACK

CLKOUT

SS

COMP

UG2

PH2

LG2

ISEN2N

ISEN2P

FB

PVCC

RSEN1

VOUT

VIN

RSEN2

FIGURE 1. SIMPLIFIED APPLICATION SCHEMATIC, 2-PHASE

SYNCHRONOUS BOOST

100

95

90 VO = 18V

85

80 VO = 24V

75

70

VO = 36V

65

60

55

50

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

LOAD CURRENT (A)

NOTE: (See Typical Application in Figure 4 on page 8.)

FIGURE 2. EFFICIENCY CURVES, VIN = 12V, TA = +25°C

February 12, 2016

FN8656.3

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC 2015, 2016. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL78229

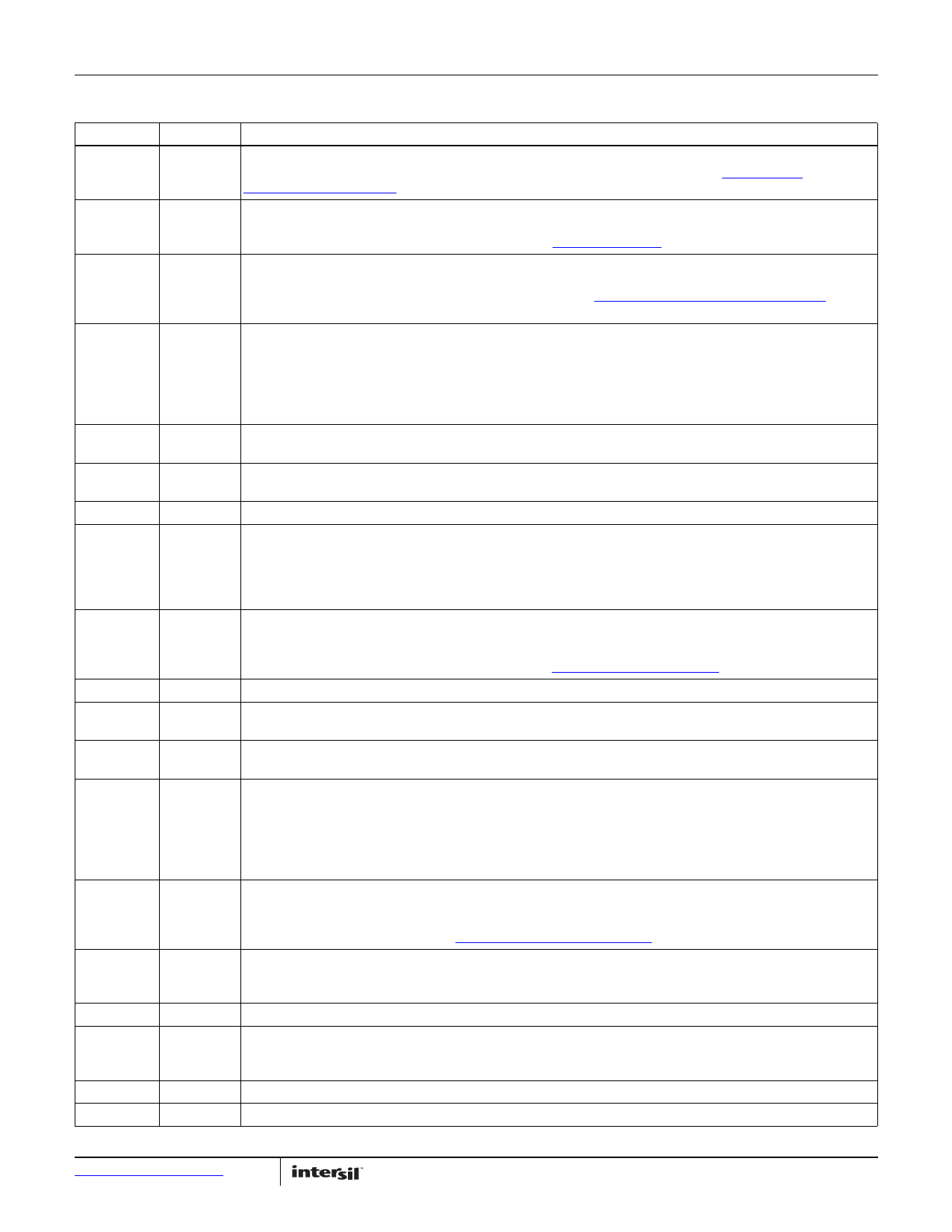

Functional Pin Description (Continued)

PIN NAME

PLLCOMP

EN

CLKOUT

BOOT2

UG2

PH2

LG2

PGND

PVCC

LG1

PH1

UG1

BOOT1

VIN

ISEN1N

ISEN1P

ISEN2N

ISEN2P

NC

PIN #

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

DESCRIPTION

This pin serves as the compensation node for the switching frequency clock’s PLL (Phase Lock Loop). A second order

passive loop filter connected between this pin and ground compensates the PLL loop. Refer to “Oscillator and

Synchronization” on page 29 for more details.

This pin is a threshold-sensitive enable input for the controller. When the EN pin is driven above 1.2V, the ISL78229 is

enabled and the internal LDO is activated to power up PVCC followed by a start-up procedure. Driving the EN pin below

0.95V will disable the IC and clear all fault states. Refer to “Enable” on page 31 for more details.

This pin outputs a clock signal with same frequency to one phase’s switching frequency. The rising edge signal on the CLKOUT

pin is delayed by 90° from the rising edge of LG1 of the same IC. With CLKOUT connected to the FSYNC pin of the second

ISL78229, a 4-phase interleaving operation can be achieved. Refer to “Oscillator and Synchronization” on page 29 for more

details.

This pin provides bias voltage to the Phase 2 high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable

to drive the external N-channel MOSFET. A 0.47µF ceramic capacitor in series with a 1.5Ω resistor are recommended between

the BOOT2 and PH2 pins. In the typical configuration, PVCC is providing the bias to BOOT2 through a fast switching diode.

In applications where a high-side driver is not needed (standard boost application for example), BOOT2 is recommended

to be connected to ground. The ISL78229 IC can detect BOOT2 being grounded during start-up and both the Phase 1 and

Phase 2 high-side drivers will be disabled. In addition, PH1 and PH2 should also be tied to ground.

Phase 2 high-side gate driver output. This output can be disabled by tying either BOOT1 and PH1 to ground or BOOT2 and

PH2 to ground.

Connect this pin to the source of the Phase 2 high-side MOSFETs and the drain of the low-side MOSFETs. This pin

represents the return path for the Phase 2 high-side gate drive.

Phase 2 low-side gate driver output. It should be connected to the Phase 2 low-side MOSFETs’ gates.

Provides the return path for the low-side MOSFET drivers. This pin carries a noisy driving current and the traces

connecting from this pin to the low-side MOSFET source and PVCC decoupling capacitor ground pad should be as short

as possible. All the sensitive analog signal traces should not share common traces with this driver return path. Connect

this pin to the ground copper plane (wiring away from the IC instead of connecting through the IC bottom PAD) through

several vias as close as possible to the IC.

Output of the internal linear regulator that provides bias for the low-side driver, high-side driver (PVCC connected to BOOTx

through diodes) and VCC bias (PVCC and VCC are typically connected through a small resistor like 10Ω or smaller, which helps

to filter out the noises from PVCC to VCC). The PVCC operating range is 4.75V to 5.5V. A minimum 10µF decoupling ceramic

capacitor should be used between PVCC and PGND. Refer to “Internal 5.2V LDO” on page 39 for more details.

Phase 1 low-side gate driver output. It should be connected to the Phase 1 low-side MOSFETs’ gates.

Connect this pin to the source of the Phase 1 high-side MOSFETs and the drain of the low-side MOSFETs. This pin

represents the return path for the Phase 1 high-side gate drive.

Phase 1 high-side MOSFET gate drive output. This output can be disabled by tying either BOOT1 and PH1 to ground or

BOOT2 and PH2 to ground.

This pin provides bias voltage to the Phase 1 high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable

to drive the external N-channel MOSFET. A 0.47µF ceramic capacitor in series with a 1.5Ω resistor are recommended between

BOOT1 and PH1 pins. In typical configuration, PVCC is providing the bias to BOOT1 through a fast switching diode.

In applications where a high-side driver is not needed (for example, standard boost application), the BOOT1 is

recommended to be connected to ground. The ISL78229 IC can detect BOOT1 being grounded during start-up and both

the Phase 1 and Phase 2 high-side drivers will be disabled. In addition, PH1 and PH2 should also be tied to ground.

Connect supply rail to this pin. Typically, connect boost input voltage to this pin. This pin is connected to the input of the internal

linear regulator, generating the power necessary to operate the chip. The DC voltage applied to the VIN should not exceed 55V

during normal operation. VIN can withstand transients up to 60V, but in this case, the device's overvoltage protection will stop

it from switching to protect itself. Refer to “Input Overvoltage Fault” on page 35 for more details.

The ISEN1N pin is the negative potential input to the Phase 1 current sense amplifier. This amplifier continuously senses

the Phase 1 inductor current through a power current sense resistor in series with the inductor. The sensed current signal

is used for current mode control, peak current limiting, average current limiting and diode emulation.

The ISEN1P pin is the positive potential input to the Phase 1 current sense amplifier.

The ISEN2N pin is the negative potential input to the Phase 2 current sense amplifier. This amplifier continuously senses

the Phase 2 inductor current through a power current sense resistor in series with the inductor. The sensed current signal

is used for current mode control, peak current limiting, average current limiting and diode emulation.

The ISEN2P pin is the positive phase input to the Phase 2 current sense amplifier.

Not Connected - This pin is not electrically connected internally.

Submit Document Feedback

5

FN8656.3

February 12, 2016

5 Page

ISL78229

Electrical Specifications Refer to Figure 3 on page 7 and Typical Application Schematics (page 8). Operating conditions unless

otherwise noted: VIN = 12V, VPVCC = 5.2V, and VVCC = 5.2V, TA = -40°C to +125°C (Note 8). Typicals are at TA = +25°C.

Boldface limits apply across the operating temperature range, -40°C to +125°C. (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

MIN MAX

(Note 7) TYP (Note 7) UNIT

Input Minimum Pulse Width - Fall-to-Rise

20 ns

Delay Time from Input Pulse Rising to LG1

Rising Edge Minus Dead Time tDT1

Input Impedance

CLG = OPEN, RDT = 50kΩ

Input impedance before synchronization

mode

35 ns

1 kΩ

Input impedance after synchronization mode

200

MΩ

CLKOUT

CLKOUTH

ICLKOUT = 500µA

VCC - VCC - 0.1

0.5

V

CLKOUTL

Output Pulse Width

ICLKOUT = -500µA

CCLKOUT = 100pF, tSW is each phase’s

switching period

0.1

1/12 * tSW

0.4

V

Phase Shift from LG1 Rising Edge to CLKOUT

Pulse Rising Edge

CLG1 = OPEN, CCLKOUT = OPEN,

fSW = 300kHz, tDT1 = 60ns (Refer to

Figure 65 on page 29 for the timing

diagram)

87 °

SOFT-START

Soft-Start Current

Minimum Soft-Start Prebias Voltage

ISS

4.5 5.0 5.5 µA

0V

Maximum Soft-Start Prebias Voltage

1.6 V

Soft-Start Prebias Voltage Accuracy

VFB = 500mV

-25

Soft-Start Clamp Voltage

VSSCLAMP

3.25

HICCUP RETRY DELAY (Refer to “Fault Response Register SET_FAULT_RESPONSE (D2h)” on page 35 for more details)

0

3.47

25

3.70

mV

V

Hiccup Retry Delay

If Hiccup fault response selected

500 ms

REFERENCE VOLTAGE FOR OUTPUT VOLTAGE REGULATION

System Reference Accuracy

Measured at the FB pin

1.576 1.600 1.620 V

FB Pin Input Bias Current

VFB = 1.6V, TRACK = Open

ERROR AMPLIFIER FOR OUTPUT VOLTAGE REGULATION (Gm1)

-0.05

0.01

0.05 µA

Transconductance Gain

2 mA/V

Output Impedance

7.5 MΩ

Unity Gain Bandwidth

Slew Rate

Output Current Capability

CCOMP = 100pF from COMP pin to GND

CCOMP = 100pF from COMP pin to GND

3.3

±3

±300

MHz

V/µs

µA

Maximum Output Voltage

3.5 3.7

V

Minimum Output Voltage

0.1 0.3 V

PWM CORE

SLOPE Pin Voltage

480 500 520 mV

SLOPE Accuracy

Duty Cycle Matching

RSLOPE = 20k (0.1%)

-20 0 20 %

RSLOPE = 40.2k (0.1%)

-20 3 20 %

VRSENx = 30mV, RSETx = 665Ω (0.1%),

RSLOPE = 27k, fSW = 150kHz,

VCOMP = 2.52V, Measure

(TON_LG2 - TON_LG1)/(TON_LG2 + TON_LG1)*2

3

%

Submit Document Feedback 11

FN8656.3

February 12, 2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISL78229.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL78220 | 6-Phase Interleaved Boost PWM Controller | Intersil Corporation |

| ISL78223 | ZVS Full-Bridge PWM Controller | Intersil Corporation |

| ISL78225 | 4-Phase Interleaved Boost PWM Controller | Intersil Corporation |

| ISL78227 | 2-Phase Boost Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |