|

|

PDF M48Z512AV Data sheet ( Hoja de datos )

| Número de pieza | M48Z512AV | |

| Descripción | 4 Mbit (512 Kbit x 8) ZEROPOWER SRAM | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M48Z512AV (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

M48Z512A

M48Z512AY, M48Z512AV

4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM

Not recommended for new design

Features

■ Integrated, ultra low power SRAM, power-fail

control circuit, and battery

■ Conventional SRAM operation; unlimited

)WRITE cycles

t(s■ 10 years of data retention in the absence of

cpower

du■ Automatic power-fail chip deselect and WRITE

roprotection

P■ Two WRITE protect voltages:

te(VPFD = power-fail deselect voltage)

le– M48Z512A: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

so– M48Z512AY: VCC = 4.5 to 5.5 V;

b4.2 V ≤ VPFD ≤ 4.5 V

O– M48Z512AV: VCC = 3.0 to 3.6 V;

-2.8 V ≤ VPFD ≤ 3.0 V

t(s)■ Battery internally isolated until power is applied

c■ Pin and function compatible with JEDEC

ustandard 512 K x 8 SRAMs

rod■ PMDIP32 is an ECOPACK® package

■ RoHS compliant

Obsolete P– Lead-free second level interconnect

32

1

PMDIP32 module

Description

The M48Z512A/Y/V ZEROPOWER® RAM is a

non-volatile, 4,194,304-bit static RAM organized

as 524,288 words by 8 bits. The devices combine

an internal lithium battery, a CMOS SRAM and a

control circuit in a plastic, 32-pin DIP module.

June 2011

Doc ID 5146 Rev 9

This is information on a product still in production but not recommended for new designs.

1/21

www.st.com

1

1 page

M48Z512A, M48Z512AY, M48Z512AV

1 Device overview

Device overview

Figure 1. Logic diagram

VCC

19

A0-A18

8

DQ0-DQ7

M48Z512A

W M48Z512AY

)M48Z512AV

t(sE

cG

Obsolete Product(s) - Obsolete ProduTable 1.

Signal names

A0-A18

DQ0-DQ7

E

G

W

VCC

VSS

VSS

Address inputs

Data inputs/outputs

Chip enable input

Output enable input

WRITE enable input

Supply voltage

Ground

AI02043

Doc ID 5146 Rev 9

5/21

5 Page

M48Z512A, M48Z512AY, M48Z512AV

Operating modes

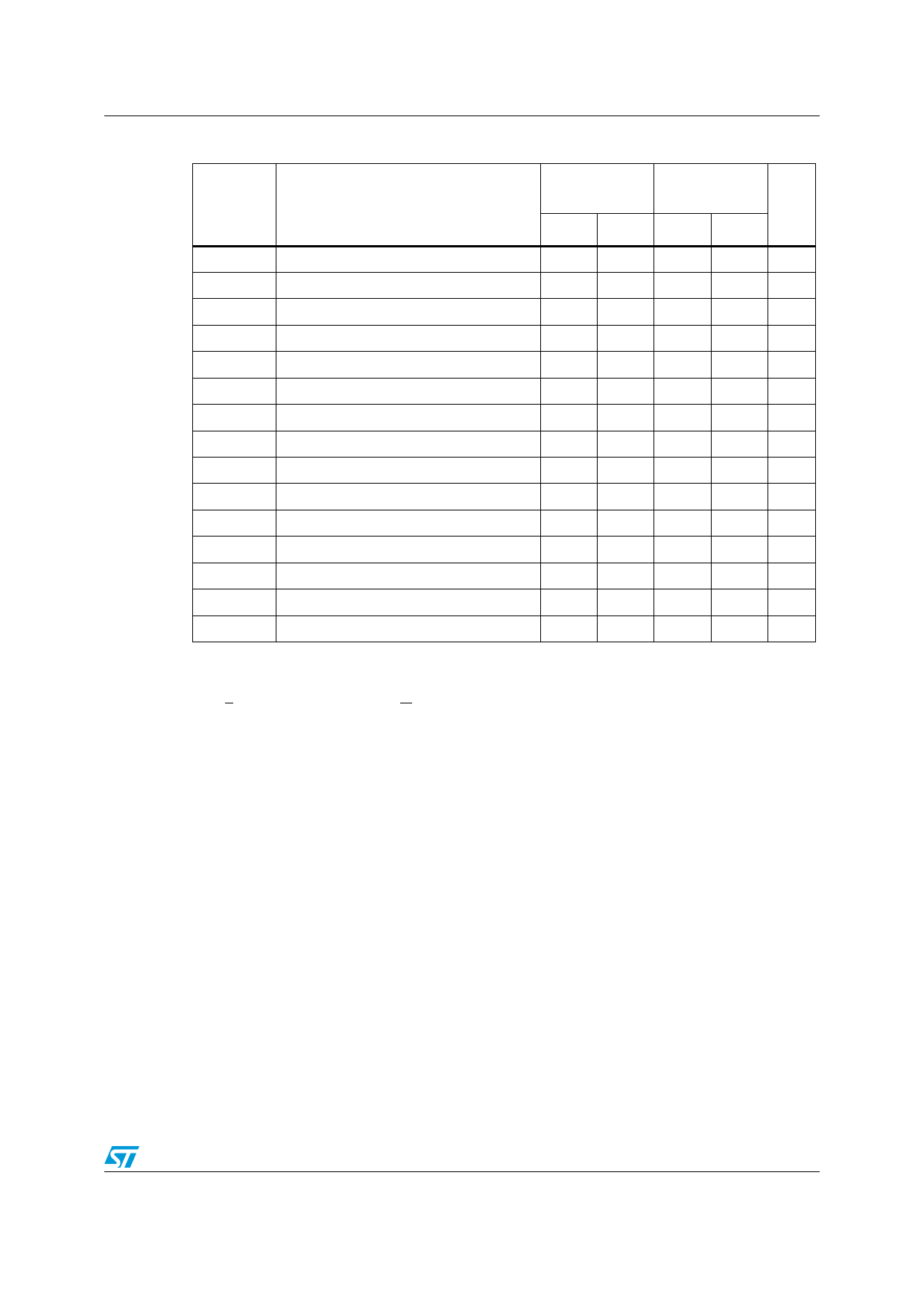

Table 4. WRITE mode AC characteristics

Symbol

Parameter(1)

M48Z512A/Y

–70

Min Max

M48Z512A/Y/V

–85

Min Max

Unit

tAVAV WRITE cycle time

70 85 ns

tAVWL Address valid to WRITE enable low

0

0 ns

tAVEL Address valid to chip enable low

0

0 ns

tWLWH WRITE enable pulse width

55 65 ns

Obsolete Product(s) - Obsolete Product(s)2.3

tELEH Chip enable low to chip enable high

55

75 ns

tWHAX WRITE enable high to address transition

5

5 ns

tEHAX Chip enable high to address transition

15

15 ns

tDVWH Input valid to WRITE enable high

30

35 ns

tDVEH Input valid to chip enable high 30 35 ns

tWHDX WRITE enable high to input transition

0

0 ns

tEHDX Chip enable high to input transition

tWLQZ(2)(3) WRITE enable low to output Hi-Z

10 10 ns

25 30 ns

tAVWH Address valid to WRITE enable high

65

75 ns

tAVEH Address valid to chip enable high

tWHQX(2)(3) WRITE enable high to output transition

65

5

75 ns

5 ns

1. Valid for ambient operating temperature: TA = 0 to 70 °C or –40 to 85 °C; VCC = 4.75 to 5.5 V, 4.5 to 5.5 V

or 3.0 to 3.6 V (except where noted).

2. CL = 5 pF.

3. If E goes low simultaneously with W going low, the outputs remain in the high impedance state.

Data retention mode

With valid VCC applied, the M48Z512A/Y/V operates as a conventional BYTEWIDE™ static

RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect,

WRITE protecting itself tWP after VCC falls below VPFD. All outputs become high impedance,

and all inputs are treated as “don't care.”

If power fail detection occurs during a valid access, the memory cycle continues to

completion. If the memory cycle fails to terminate within the time tWP, WRITE protection

takes place. When VCC drops below VSO, the control circuit switches power to the internal

energy source which preserves data.

The internal coin cell will maintain data in the M48Z512A/Y/V after the initial application of

VCC for an accumulated period of at least 10 years when VCC is less than VSO. As system

power returns and VCC rises above VSO, the battery is disconnected, and the power supply

is switched to external VCC. WRITE protection continues for tER after VCC reaches VPFD to

allow for processor stabilization. After tER, normal RAM operation can resume.

For more information on battery storage life refer to the application note AN1012.

Doc ID 5146 Rev 9

11/21

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet M48Z512AV.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M48Z512A | 4 Mbit (512 Kbit x 8) ZEROPOWER SRAM | ST Microelectronics |

| M48Z512AV | 4 Mbit (512 Kbit x 8) ZEROPOWER SRAM | STMicroelectronics |

| M48Z512AY | 4 Mbit (512 Kbit x 8) ZEROPOWER SRAM | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |