|

|

PDF DA7210 Data sheet ( Hoja de datos )

| Número de pieza | DA7210 | |

| Descripción | Ultra-low power stereo codec | |

| Fabricantes | Dialog Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DA7210 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DA7210

Ultra-low power stereo codec

Company confidential

General description

The DA7210 is a high fidelity audio codec with integrated true-ground capless headphone driver

suitable for a variety of low power, digital portable audio products.

Featuring a high efficiency headphone amplifier and supporting economic single supply voltages

down to 1.8 V, the ultra-low 2.5 mW power consumption extends music playback time for battery

operated equipment.

Eight analogue input pins allow multiple audio sources to be internally mixed, eliminating the need for

external switches. Both single-ended and fully-differential line and microphone inputs are supported

with built-in variable gain amplifiers to optimise dynamic range prior to digitisation.

DA7210 provides simultaneous connection to stereo headphone, stereo line outputs, and a mono

differential output. Stereo line outputs can be differential or single-ended. Both stereo outputs have

volume control from -54 dB to +15 dB.

Filtering and gain control is performed digitally including 5-band EQ and a digital input AGC with

programmable attack and decay parameters. A configurable signal processing engine allows various

enhancements and effects on the digital audio signal like acoustic filtering, wind noise suppression

and 3D sound.

The multi-slot I2S/PCM interface supports all common sample rates between 8 and 96 kHz in master

or slave mode operation.

Key features

■ Stereo multi-bit Delta Sigma DAC with SNR ■ Audio serial data bus supports I2S,

100 dB ('A' weighted @ 48 kHz)

left/right justified, DSP and TDM modes

■ Stereo multi-bit Delta Sigma ADC with SNR ■ Stereo or mono differential microphone

96 dB ('A' weighted @ 48 kHz)

interface

■ Ultra low-power stereo headphone driver with ■ Programmable ultra-low noise bias supply for

□ Stereo DAC to HP playback power:

2.5 mW

electret microphones

■ Volume controlled stereo auxiliary inputs and

□ 2x58 mW output power (16 Ω)

outputs supporting FM Radio and fixed gain

□

□

‘Capless’ output via GND centred signals

Four level charge pump with continuous

tracking of audio signal (Class G)

■

■

speaker amplifiers

Multi-mode audio routing and mixers

Pop & click suppression circuitry

□ Short circuit protection

■ ASSP DSP filter engine for digital audio

■ Support of 8, 11.025, 12, 16, 22.05, 24, 32,

enhancements (acoustic filtering, wind noise

suppression, 5-band equaliser, 3D sound,

44.1, 48 and 96 kHz sample rates

automatic gain control)

■ On-chip PLL with signal shaper and audio ■ Supports supply from single voltage

Sample Rate Matching

(1.8/2.5 V)

■ Wide range of external clocks including

■ Extensive modular power control

industry standard 256xFs, system clock 12,

13, 24, 26 or 27 MHz and low power 32 kHz

■ Package: 49 bump WL-CSP – 0.4 mm pitch

mode

Applications

■ Personal media players

■ Portable consumer devices

■ Music handsets

■ Personal navigation devices

Datasheet

CFR0011-120-00 Rev 5

Revision 3a

1 of 113

15-Oct-2015

© 2015 Dialog Semiconductor

1 page

DA7210

Ultra-low power stereo codec

Company confidential

Table 13: Electrical characteristics: Headphone amplifier .................................................................. 21

Table 14: Electrical characteristics: Phase locked loop (MCLK) ......................................................... 22

Table 15: Electrical characteristics: Digital I/O .................................................................................... 22

Table 16: I2S/DSP timing characteristics ............................................................................................ 23

Table 17: 2-wire control timing characteristics .................................................................................... 24

Table 18: 4-wire control timing characteristics .................................................................................... 25

Table 19: Start-up times after setting SC_MST_EN = 1 ..................................................................... 25

Table 20: ADC digital high pass filter specifications ........................................................................... 28

Table 21: Permitted register values for ALC_NOIS (0x85 [5:0]) ......................................................... 31

Table 22: DAC digital high pass filter specifications ........................................................................... 33

Table 23: Headphone/OUT1 amplifier gain settings ........................................................................... 37

Table 24: GP filter section enable bits................................................................................................. 41

Table 25: Band-equaliser corner frequencies ..................................................................................... 41

Table 26: 5-band-equaliser turn-over/centre frequencies ................................................................... 41

Table 27: Voice mode recording high-pass filter specifications .......................................................... 47

Table 28: Voice mode playback high-pass filter specifications ........................................................... 49

Table 29: Internal system clock frequency .......................................................................................... 54

Table 30: Block enable and system standby bits ................................................................................ 54

Table 31: ADC and DAC clock frequencies ........................................................................................ 55

Table 32: Master mode PLL-DIV look up table ................................................................................... 56

Table 33: SRM mode PLL-DIV look up table ...................................................................................... 56

Table 34: PLL master mode register setting recommendations.......................................................... 57

Table 35: MCLK frequencies in non-PLL slave mode......................................................................... 59

Table 36: Non-PLL slave mode and PLL master mode sample rate settings ..................................... 60

Table 37: SRM mode PLL division ratio settings ................................................................................ 62

Table 38: Slave mode PLL-enabled register setting recommendations ............................................. 62

Table 39: 4 wire interface .................................................................................................................... 65

Table 40: 4 wire clock configurations .................................................................................................. 66

Table 41: Register map ....................................................................................................................... 69

Table 42: PAGE0 0x00........................................................................................................................ 72

Table 43: CONTROL 0x01 .................................................................................................................. 72

Table 44: STATUS 0x02...................................................................................................................... 72

Table 45: STARTUP 1 0x03 ................................................................................................................ 73

Table 46: STARTUP 2 0x04 ................................................................................................................ 73

Table 47: STARTUP 3 0x05 ................................................................................................................ 74

Table 48: MIC_L 0x07 ......................................................................................................................... 74

Table 49: MIC_R 0x08......................................................................................................................... 75

Table 50: AUX1_L 0x09 ...................................................................................................................... 75

Table 51: AUX1_R 0x0A ..................................................................................................................... 75

Table 52: AUX2 0x0B .......................................................................................................................... 76

Table 53: IN_GAIN 0x0C..................................................................................................................... 77

Table 54: INMIX_L 0x0D ..................................................................................................................... 78

Table 55: INMIX_R 0x0E..................................................................................................................... 78

Table 56: ADC_HPF 0x0F................................................................................................................... 79

Table 57: ADC 0x10 ............................................................................................................................ 79

Table 58: ADC_EQ1_2 0x11 ............................................................................................................... 80

Table 59: ADC_EQ3_4 0x12 ............................................................................................................... 81

Table 60: ADC_EQ5 0x13 ................................................................................................................... 82

Table 61: DAC_HPF 0x14 ................................................................................................................... 83

Table 62: DAC_L 0x15 ........................................................................................................................ 83

Table 63: DAC_R 0x16........................................................................................................................ 84

Table 64: DAC_SEL 0x17 ................................................................................................................... 84

Table 65: SOFTMUTE 0x18 ................................................................................................................ 85

Table 66: DAC_EQ1_2 0x19 ............................................................................................................... 86

Table 67: DAC_EQ3_4 0x1A .............................................................................................................. 87

Table 68: DAC_EQ5 0x1B................................................................................................................... 88

Table 69: OUTMIX_L 0x1C ................................................................................................................. 88

Table 70: OUTMIX_R 0x1D................................................................................................................. 89

Table 71: OUT1_L 0x1E...................................................................................................................... 89

Datasheet

CFR0011-120-00 Rev 5

Revision 3a

5 of 113

15-Oct-2015

© 2015 Dialog Semiconductor

5 Page

DA7210

Ultra-low power stereo codec

Company confidential

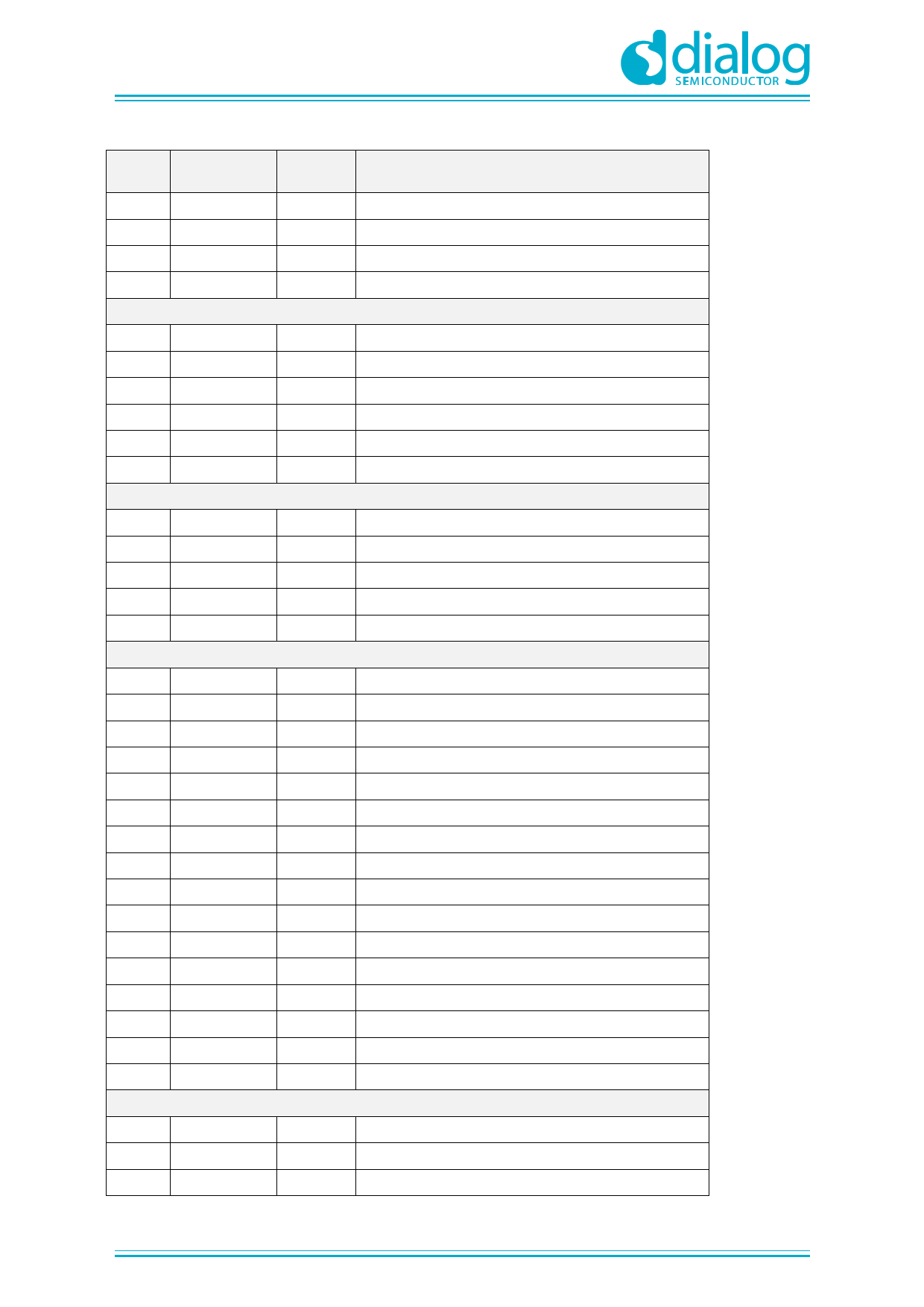

Pin no. Pin name

1A GPO

6B AGND

3D AGND1

1E GNDCP

5F SO

5G SI

6G SK

4F nCS

4E PD

2B HPS

4G CLK

3F WCLK

7F DATIN

6F DATOUT

7G MCLK

6C MICP_L

7B MICN_L

7C MICP_R

6D MICN_R

5D AUX1_L

6E AUX1_R

7D AUX2P

7E AUX2N

4C OUT1P_L

5A OUT1N_L

4A OUT1P_R

4B OUT1N_R

3C OUT2N

3B OUT2P

1B HP_L

2C HP_R

3E HPCF1P

1F HPCF1N

2E HPCF2P

Type

Description

(Table 2)

AIO General Purpose Output

VSS

Analogue GND

VSS

Analogue GND

VSS

Digital and charge pump ground, attached to paddle

Control

DO 4-WIRE Data output

DIO 4-WIRE Data input/2-WIRE bidirectional Data

DI 4-WIRE/2-WIRE Clock

DI 4-wire Chip select

DI Power down signal (power down when high)

AIO Headphone Ground Sense

Digital Audio Interface

DIO Digital Audio bit clock

DIO Digital Audio left/right clock

DI Digital Audio Data input

DO Digital Audio Data output

DI Master clock input

Audio inputs/outputs

AI Left channel differential microphone +ve input

AI Left channel differential microphone –ve input

AI Right channel differential microphone +ve input

AI Right channel differential microphone –ve input

AI Left channel single-ended auxiliary input

AI Right channel single-ended auxiliary input

AI 2nd channel differential auxiliary +ve input

AI 2nd channel differential auxiliary –ve input

AO Differential or single ended +ve line out left

AO Differential –ve line out left

AO Differential or single ended +ve line out right

AO Differential –ve line out right

AO 2nd channel differential auxiliary -ve output

AO 2nd channel differential auxiliary +ve output

AO Left head phone amp output

AO Right head phone amp output

Charge pump

PS Head phone amp charge pump floating cap1 +ve

PS Head phone amp charge pump floating cap1 –ve

PS Head phone amp charge pump floating cap2 +ve

Datasheet

CFR0011-120-00 Rev 5

Revision 3a

11 of 113

15-Oct-2015

© 2015 Dialog Semiconductor

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DA7210.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DA7210 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7211 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7212 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7217 | Ultra-Low Power Stereo Codec | Dialog Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |