|

|

PDF SGN5210 Data sheet ( Hoja de datos )

| Número de pieza | SGN5210 | |

| Descripción | 2.4 GHz RF Transceiver | |

| Fabricantes | SIGNIA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SGN5210 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

Product Description:

The Signia SGN5210 IC is a low-cost, fully integrated CMOS

radio frequency (RF) transceiver, optimized for applications in

the globally available 2.4~2.5 GHz ISM band. It contains

transmit, receive, VCO and PLL functions, including VCO

resonator, thus minimizing the need for external components.

The synthesizer is designed for fast hopping and ease of use,

requiring only an external RC loop filter. The on-chip reference

divider accepts integer reference frequencies between 4~25

MHz, for 1 MHz channel spacing.

The transmit section features digitally adjustable output power,

ranging from approx. +2 to -32 dBm. Nominal mark and space

deviation is ±167 kHz. IQ modulation yields transmit data rates

from DC up to 333 kbps (1 Mbps max.). Low in-band spurious

signals, and internal Gaussian filtering of the transmit data,

ease regulatory compliance.

The superhetrodyne receiver is comprised of LNA, active

image-reject down-converter, and “low-IF” amplifier/limiter

chain. IF bandwidth is typically 1.2 MHz. FM demodulation is

completely internal, utilizing digital delay-line discriminator

architecture. The receiver may be used in applications

requiring data rates from DC to 333 kbps (1 Mbps max.).

Symbol rate can be 3 or more µS, and is optimized for an

integer number of µS per symbol.

The SGN5210 also features a fully digital baseband interface,

greatly simplifying the interface to commonly used

microprocessors and ASICs.

Internal DC block on the antenna pin means only a low-cost

bandpass filter is needed between the antenna and the IC.

For longer battery life, power consumption is minimized by

providing separate power controls for transmit, receive, PLL,

VCO, and PA sections, as well as a sleep state to reduce

standby battery usage.

This product is available in 48-lead 7x7 mm JEDEC standard

QFN package, featuring an exposed pad on the bottom for

best RF characteristics.

Ordering Information

SGN5210

2.4 GHz RF Transceiver IC

Signia Technologies, Inc.

245 Sinclair Frontage Road

Milpitas, CA 95035 USA

Phone: (408) 941-0490

FAX: (408) 941-0493

SGN5210

2.4 GHz RF Transceiver

Production Data Sheet

Key Features:

• Complete fully Integrated radio transceiver in

lowest-cost silicon CMOS

• Low power consumption:

- Tx 40mA

- Rx 50mA

• Max. Transmit power: 1.6 mW (+2 dBm)

• Fast Hopping: up to 1600 hops per second

• Direct IQ up-conversion for stable PLL and

modulation index

• Clean Transmit output needs minimum filtering

• Nominal Receiver sensitivity: -80 dBm

• Low-IF approach to minimize DC offset

• LO Leakage very low, << -60 dBm

• Built-in AutoTune circuitry for the internal receive

IF filters

• No external RF balun or T/R switch required

• Fully digital baseband interface

• Flexible power management

for minimizing current consumption

• 7x7mm QFN package

with minimum RF parasitics

• A component of Signia’s 2.4 GHz

RFIC Transceiver family

Applications:

• Wireless Game controllers

• Wireless keyboard, mice

• Wireless headsets, audio

• Remote controls

• Home automation

• Industrial controls

May, 2003

SGN5210 Data Sheet

www.signiatech.com

Page 1 of 20

1 page

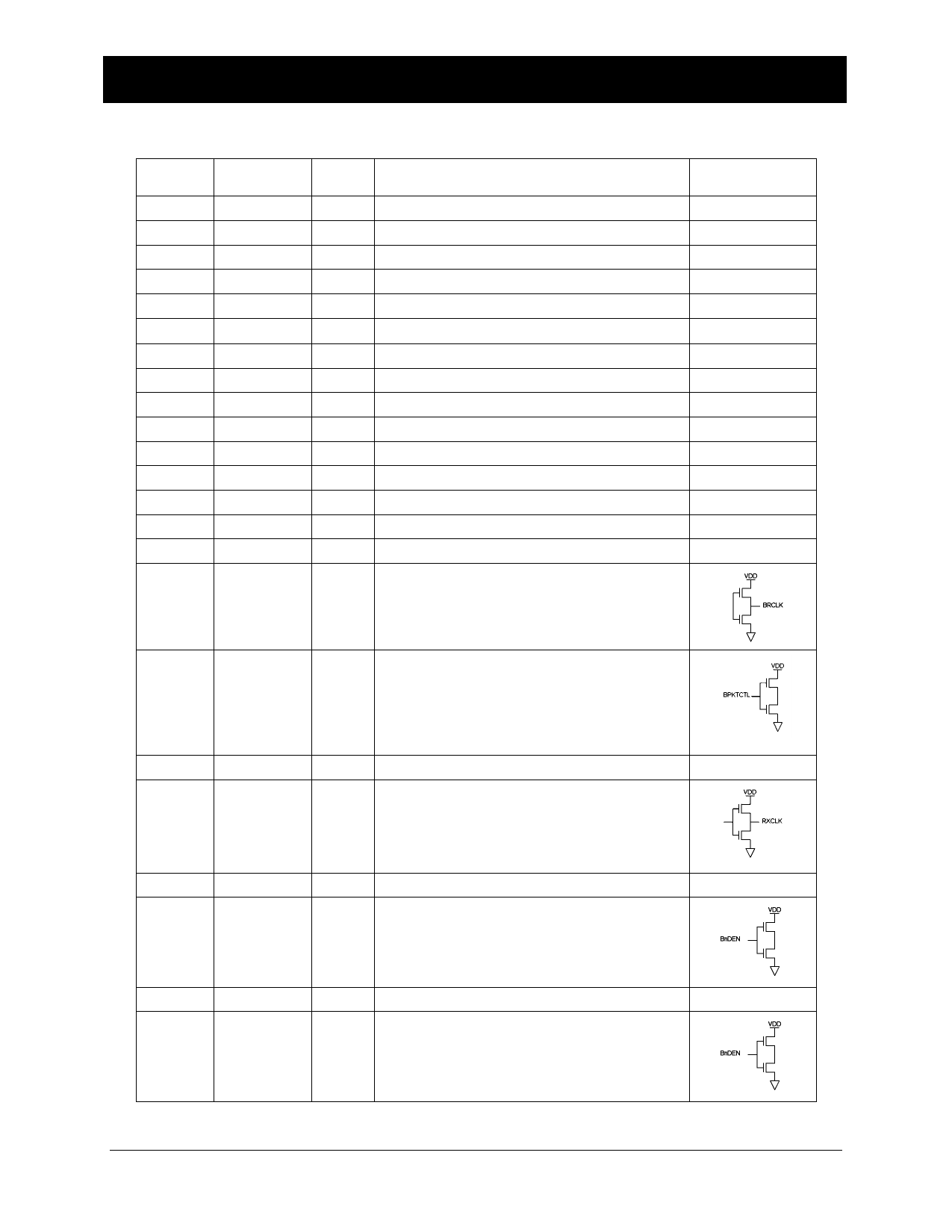

Pin Description

Pin No. Pin Name Type

Description

1

2

3

4

5, 6, 7

8

9

10, 11

12

13, 14

15

16

17

18 ~ 21

22, 23

24

PA_EN

VDD

GND

VDD

GND

TX/RX

GND

VDD

GND

VDD

GND

VDD

GND

TEST

GND

BRCLK

O

PWR

GND

PWR

GND

50Ω RF

GND

PWR

GND

PWR

GND

PWR

GND

--

GND

O

DO NOT CONNECT.

Power supply voltage.

Ground connection.

Power supply voltage.

Ground connections.

RF Input/output pin, to antenna.

Ground connection.

Power supply voltage.

Ground connection.

Power supply voltage.

Ground Connection.

Power supply voltage.

Ground Connection.

DO NOT CONNECT. Reserved for factory test.

Ground Connections

Outputs either 1MHz Tx symbol clock, or 12 MHz

APLL output.

SGN5210

Interface

25 BPKTCTL I In transmit state this pin turns on PA_ON by receiving

a high signal from the baseband.

In receive state, this pin controls the DC estimation

behavior in two different states: a low state is used to

set the DC estimation for fast acquisition and a high

state is used for slower or fixed DC estimation.

26

(Reserved)

- DO NOT CONNECT.

27

RXCLK

O Receiver symbol clock recovery output.

Fixed at 1 MHz fundamental rate.

Useful for over-sampling the BDATA1 Rx data output.

28

TEST-SE

-- DO NOT CONNECT. Reserved for factory test.

29

BXTLEN

I This sets the chip into SLEEP state by supplying a

low signal.

30

TEST3

-- Reserved for factory test.

31

BnDEN

I Enable line for the 3-wire bus. Active low.

May, 2003

SGN5210 Data Sheet

www.signiatech.com

Page 5 of 20

5 Page

SGN5210

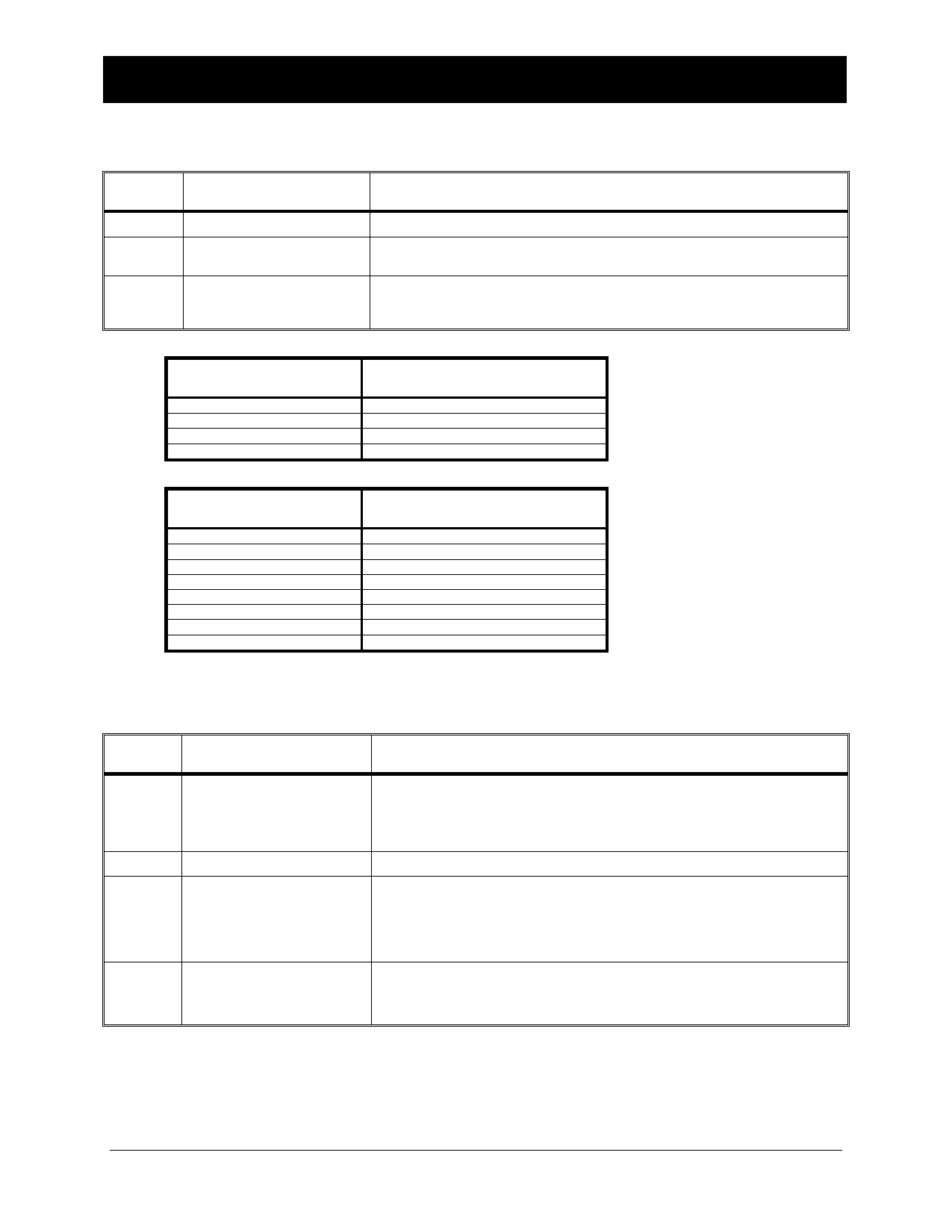

Receiver Control (Write/Read) – Register 4 (Default = 0x0030)

Bit No.

Bit Name

Description

15 - 5

4-3

2-0

(reserved)

WT_LNA_GAIN[1:0]

WT_PGA [2:0]

(reserved)

2-bit LNA Gain Control @ 10 dB/step. Active only when PGA_PARA_OW in register

2 is set. In normal operation, receive gains are controlled by local PGA circuit.

3-bit PGA control for 50 dB VGA (-10/+40 dB) dynamic range @ 2 dB/step. Active

only when PGA_PARA_OW in register 2 is set. In normal operation, receive gain

are controlled by local PGA circuit.

WT_LNA_GAIN [1:0]

00

01

10

11

WT_PGA [2:0]

000

001

010

011

100

101

110

111

LNA Gain (dB)

16

6

-4

Not Defined

PGA Gain (dB)

0

2

4

6

8

10

12

14

RFIC Control (Write/Read) – Register 5 (Default = 0x4D0C)

Bit No.

Bit Name

Description

15 - 11

10 - 9

8

7-0

SYNTH_ON_DELAY_CNT[4:0]

(reserved)

REG_PROTECT

RX_DELAY [7:0]

In the state WAIT DATA SYNC, RF oscillator will be enabled at first. There is time

offset controlled by the counter SYNTH_ON_DELAY_CNT. When the counter

counts to zero and SYNTH_IDLE_OFF = 0, the synthesizer will be enabled.

Each time increment is 1 µS.

(reserved)

The bit is used to protect registers from accidental change.

If REG_PROTECT = 1 (default), only registers 7, 8, 9, and this REG_PROTECT bit,

may be modified.

If REG_PROTECT = 0, all the registers can be modified.

8-bit Receive delays from receiving synthesizer program register to start transmit

BDATA1 to BBIC.

Each time increment is 1 µS.

May, 2003

SGN5210 Data Sheet

www.signiatech.com

Page 11 of 20

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet SGN5210.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SGN5210 | 2.4 GHz RF Transceiver | SIGNIA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |