|

|

PDF CDP6853 Data sheet ( Hoja de datos )

| Número de pieza | CDP6853 | |

| Descripción | CMOS Asynchronous Communications Interface Adapter | |

| Fabricantes | GE | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDP6853 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CMOS Peripherals

CDP6853

fttil 2. YDO

C.O 27 08

CIT 21 ilia

lIfl

ft.c

XTLI

xno

m

•nJ"

. o.2. 07

2. .1

••22 DO

21

20 02

T•• 10

I. AOI

,.1fmt.,! "12

CE

I. ADO

17 mr

Ie 1m!

A'Yso

"TOP Vl!W" tics-non

TERMINAL ASSIGNMENT

Product Preview

CMOS Asynchronous Communications

Interface Adapter (ACIA) with MOTEL Bus

F••tur••:

• Compatible with q-bit microprocessors

• Multiplexed Address/Data Bus (MOTEL Bus)

• Full duplex operation with buffered receiver

and transmitter

• Data set/modem control functions

• Internal baud rate generator with 15

programmable baud rates (50 to 19,200)

• Operates at baud ra-tes up to 250,000 via

proper crystal or clock selection

The RCA-CDP6853 Asynchronous Communications Inter-

face Adapter (ACIA) provides an easily implemented,

program controlled interface between 8-bit microprocessor-

based systems and serial communication data sets and

modems.

The CDP6853 has an Internal baud rate generator. This

feature eliminates the need for multiple component support

circuits, a crystal being the only other part required. The

Transmitter baud rate can be selected under program

control to be either 1 of 15 different rates from 50 to 19,200

baud, or at 1/16 times an external clock rate. The Receiver

baud rate may be selected under program control to be

either the Transmitter rate, or at 1/16 times an external

clock rate. The CDP6853 has programmable word lengths

of 5,6,7, or 8 bits; even, odd, or no parity; 1, 1'h, or 2 stop

bits.

The CDP6853Is designed for maximum programmed control

from the CPU, to simplify hardware implementation. Three

separate registers permit the CPU to easily select the

CDP6853 operating modes and data checking parameters

and determine operational status.

The Command Register controls parity, receiver echo

mode, transmitter interrupt control, the state of the RTS

line, receiver Interru pt control, and the state of the J5TR Ii ne.

The Control Register controls the number of stop bits, word

length, receiver clock source, and baud rate.

The Status Register indicates the states of the IRO, DSR,

and i5Ci5' lines, Transmitter and Receiver Data Registers,

and Overrun, Framing and Parity Error conditions.

• Program-selectable internally or externally

controlled receiver rate

• Programmable word lengths, number of stop bits,

and parity bit generation and detection

• Programmable interrupt control

• Program reset

• Program-selectable serial echo mode

• Two chip selects

• One chip enable

• Single 3V to 6V power supply

• Full TTL compatibility

• 4-MHz, 2-MHz, or 1-MHz operation

(CDP6853-4, CDP6853-2, CDP6853-1, respectively)

The Transmitter and Receiver Data Registers are used for

temporary data storage by the CDP6853 Transmit and

Receiver circuits.

The MOTEL Bus allows interfacing to 6805 and 8085 type

multiplexed address data bus.

The CDP6853-1, CDP6853-2, and CDP6853-4 are capable

of interfaCing with microprocessors with cycle times of 1-

MHz, 2-MHz, and 4-MHz, respectively.

The CDP6853 Is supplied In 28-lead, hermetic, dual-in-line

side-brazed ceramic (0 suffix) and in 28-lead, dual-in-line

plastic (E suffix) packages.

File Number 1487

612 _________________________________________________________________

1 page

CMOS Peripherals

CDP6853

CDP8853 INTERNAL ORGANIZATION

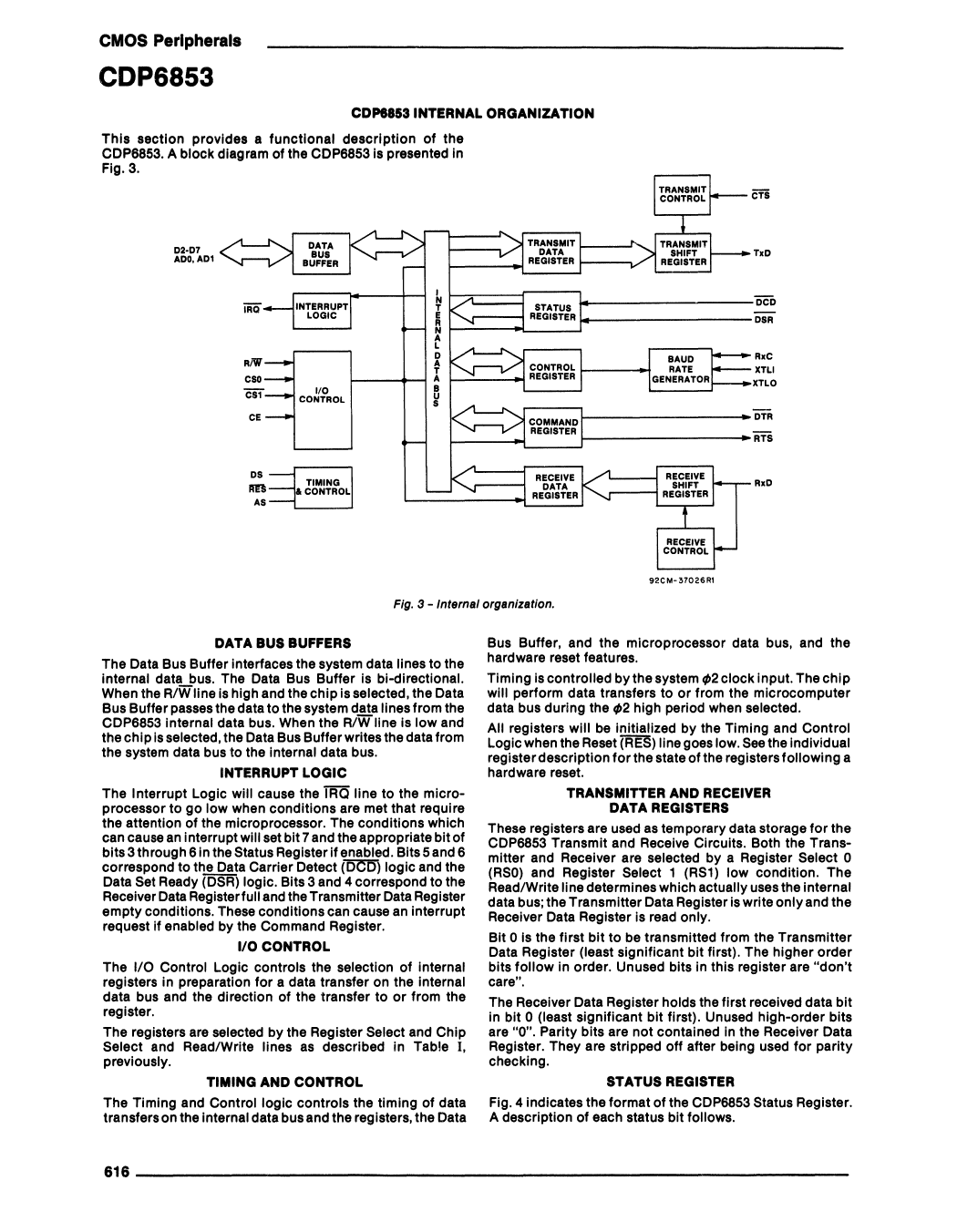

This section provides a functional description of the

CDP6853. A block diagram of the CDP6853 is presented In

Fig. 3.

D2·D7

ADO,AD1

eTS

TxD

oeD

DSR

Rxe

XTLI

XTLO

DTR

iiTs

RxD

Fig. 3 - Internal organization.

92CM-37026Rl

DATA BUS BUFFERS

The Data Bus Buffer interfaces the system data lines to the

internal data bus. The Data Bus Buffer is bi-directional.

When the R/Wline is high and the chip is selected, the Data

Bus Buffer passes the data to the system data lines from the

CDP6853 internal data bus. When the R/W line is low and

the chip is selected, the Data Bus Buffer writes the data from

the system data bus to the internal data bus.

INTERRUPT LOGIC

The Interrupt Logic will cause the IRQ line to the micro-

processor to go low when conditions are met that require

the attention of the microprocessor. The conditions which

can cause an interrupt will set bit 7 and the appropriate bit of

bits 3 through 6 in the Status Register if enabled. Bits 5 and 6

correspond to the Data Carrier Detect (DCDi logic and the

Data Set Ready (DSR) logic. Bits 3 and 4 correspond to the

Receiver Data Registerfull and the Transmitter Data Register

empty conditions. These conditions can cause an interrupt

request if enabled by the Command Register.

I/O CONTROL

The I/O Control Logic controls the selection of internal

registers in preparation for a data transfer on the internal

data bus and the direction of the transfer to or from the

register.

The registers are selected by the Register Select and Chip

Select and Read/Write lines as described in Table I,

previously.

TIMING AND CONTROL

The Timing and Control logic controls the timing of data

transfers on the internal data bus and the registers, the Data

Bus Buffer, and the microprocessor data bus, and the

hardware reset features.

Timing is controlled by the system 1/12 clock input. The chip

will perform data transfers to or from the microcomputer

data bus during the 1/12 high period when selected.

All registers will be initialized by the Timing and Control

Logic when the Reset (RES) line goes low. See the individual

register description for the state of the registers following a

hardware reset.

TRANSMITTER AND RECEIVER

DATA REGISTERS

These registers are used as temporary data storage for the

CDP6853 Transmit and Receive Circuits. Both the Trans-

mitter and Receiver are selected by a Register Select 0

(RSO) and Register Select 1 (RS1) low condition. The

Read/Write line determines which actually uses the internal

data bus; the Transmitter Data Register is write only and the

Receiver Data Register is read only.

Bit 0 is the first bit to be transmitted from the Transmitter

Data Register (least significant bit first). The higher order

bits follow in order. Unused bits in this register are "don't

care".

The Receiver Data Register holds the first received data bit

in bit 0 (least significant bit first). Unused high-order bits

are "0". Parity bits are not contained in the Receiver Data

Register. They are stripped off after being used for parity

checking.

STATUS REGISTER

Fig. 4 indicates the format of the CDP6853 Status Register.

A description of each status bit follows.

616 _________________________________________________________________

5 Page

CMOS Peripherals

CDP6853

CDP8853 OPERATION (Cont'd)

Effect of CTS on Echo Mode Operation (Fig. 14)

See "Effect of CTS on Transmitter" for the effect of CTS on

the Transmitter. Receiver operation is unaffected by CTS,

so, in Echo Mode, the Transmitter is affected in the same

way as "Effect of C'F§ on Transmitter". In this case,

however, the processor interrupts signify that the Receiver

Data Register is full, so the processor has no way of

knowing that the Transmitter has ceased to echo.

--_\/

CHAR#n

I

'j

CHAR#n+1

I

CHAR#n+2

'j I 'J

CHAR#n+3

I

STOP

Jl G"GIHJ SEtHR,O

STOP

STOP

STOP

I [SJBtJ~:GEJ I [%GIOGOEJ I

1- 1- 1-I~

LnIQ JI] LllJ Llll UU......----

Nor·CLEAR-rO·SEND

!

I

ISTOP

STOP

IhO ~L.I~EI ISNI p

Isols,I··11

CTS GOES TO

[ L~ )"FALSE" CONDITION

NORMAL

--~

RECEIVER DATA

REGISTER FULL

INTERRUPTS

92CM-36798

Fig. 14 - Effect of CTS on echo mode,

Overrun In Echo Mode (Fig. 15)

If Overrun occurs in Echo Mode, the Receiver is affected the

same way as described in "Effect of Overrun on Receiver",

For the re-transmitted data, when overrun occurs, the TxD

line goes to the "MARK" condition until the first Start Bit

after the Receiver Data Register is read by the processor,

CHAR#n

~/r--------JI--_~

CHAR #x

CHAR #x + 1

/~_ _ _-LI_ _ _ _~~_ _LI_ _ _

STOP

STOP

A'O1n - - GELIDr;E[EL:] I

I ISTOP [%G[~STOP [%EII~;E

~~

-- LJl]\~--.--_/LJ] !l!---'LllJ

LJ]mr-----

-_-_-_ -_-_-_n 1IAQ ISTOP 1"-'r--r_-~!----''-- ~~--- ~-/+-i

8 3 ~TxO

~H' - - L _.....8._,...

I START

1;-

PROCESSOR FINALLY

IPROCESSOR

~~~E:~g~VER

READS RECEIVER

E:~~ ::~~STER,

Tx D DATA

DATA REGISTER

FULL

I

PROCESSOR

READS

STATUS

REGISTER

OVERRUN OCCURS

T x D GOES TO

"MARK"

CONDITION

CHARACTER (#n)

RESUMES

PROCESSOR

INTERRUPT

FOR CHAR#x

IN RECEIVER

DATA REGISTER

92CM-36788

Fig, 15 - Overrun in echo mode,

622 _______________________________________________________________

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CDP6853.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDP6853 | CMOS Asynchronous Communications Interface Adapter | GE |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |