|

|

PDF ATtiny45 Data sheet ( Hoja de datos )

| Número de pieza | ATtiny45 | |

| Descripción | Atmel 8-bit AVR Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATtiny45 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Atmel 8-bit AVR Microcontroller with 2/4/8K

Bytes In-System Programmable Flash

ATtiny25/V / ATtiny45/V / ATtiny85/V

Features

• High Performance, Low Power AVR® 8-Bit Microcontroller

• Advanced RISC Architecture

– 120 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

• Non-volatile Program and Data Memories

– 2/4/8K Bytes of In-System Programmable Program Memory Flash

• Endurance: 10,000 Write/Erase Cycles

– 128/256/512 Bytes In-System Programmable EEPROM

• Endurance: 100,000 Write/Erase Cycles

– 128/256/512 Bytes Internal SRAM

– Programming Lock for Self-Programming Flash Program and EEPROM Data Security

• Peripheral Features

– 8-bit Timer/Counter with Prescaler and Two PWM Channels

– 8-bit High Speed Timer/Counter with Separate Prescaler

• 2 High Frequency PWM Outputs with Separate Output Compare Registers

• Programmable Dead Time Generator

– USI – Universal Serial Interface with Start Condition Detector

– 10-bit ADC

• 4 Single Ended Channels

• 2 Differential ADC Channel Pairs with Programmable Gain (1x, 20x)

• Temperature Measurement

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– debugWIRE On-chip Debug System

– In-System Programmable via SPI Port

– External and Internal Interrupt Sources

– Low Power Idle, ADC Noise Reduction, and Power-down Modes

– Enhanced Power-on Reset Circuit

– Programmable Brown-out Detection Circuit

– Internal Calibrated Oscillator

• I/O and Packages

– Six Programmable I/O Lines

– 8-pin PDIP, 8-pin SOIC, 20-pad QFN/MLF, and 8-pin TSSOP (only ATtiny45/V)

• Operating Voltage

– 1.8 - 5.5V for ATtiny25V/45V/85V

– 2.7 - 5.5V for ATtiny25/45/85

• Speed Grade

– ATtiny25V/45V/85V: 0 – 4 MHz @ 1.8 - 5.5V, 0 - 10 MHz @ 2.7 - 5.5V

– ATtiny25/45/85: 0 – 10 MHz @ 2.7 - 5.5V, 0 - 20 MHz @ 4.5 - 5.5V

• Industrial Temperature Range

• Low Power Consumption

– Active Mode:

• 1 MHz, 1.8V: 300 µA

– Power-down Mode:

• 0.1 µA at 1.8V

Rev. 2586Q–AVR–08/2013

2586Q–AVR–08/2013

1 page

The ATtiny25/45/85 provides the following features: 2/4/8K bytes of In-System Programmable Flash, 128/256/512

bytes EEPROM, 128/256/256 bytes SRAM, 6 general purpose I/O lines, 32 general purpose working registers, one

8-bit Timer/Counter with compare modes, one 8-bit high speed Timer/Counter, Universal Serial Interface, Internal

and External Interrupts, a 4-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, and

three software selectable power saving modes. Idle mode stops the CPU while allowing the SRAM, Timer/Counter,

ADC, Analog Comparator, and Interrupt system to continue functioning. Power-down mode saves the register con-

tents, disabling all chip functions until the next Interrupt or Hardware Reset. ADC Noise Reduction mode stops the

CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions.

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash

allows the Program memory to be re-programmed In-System through an SPI serial interface, by a conventional

non-volatile memory programmer or by an On-chip boot code running on the AVR core.

The ATtiny25/45/85 AVR is supported with a full suite of program and system development tools including: C Com-

pilers, Macro Assemblers, Program Debugger/Simulators and Evaluation kits.

ATtiny25/45/85 [DATASHEET]

2586Q–AVR–08/2013

5

5 Page

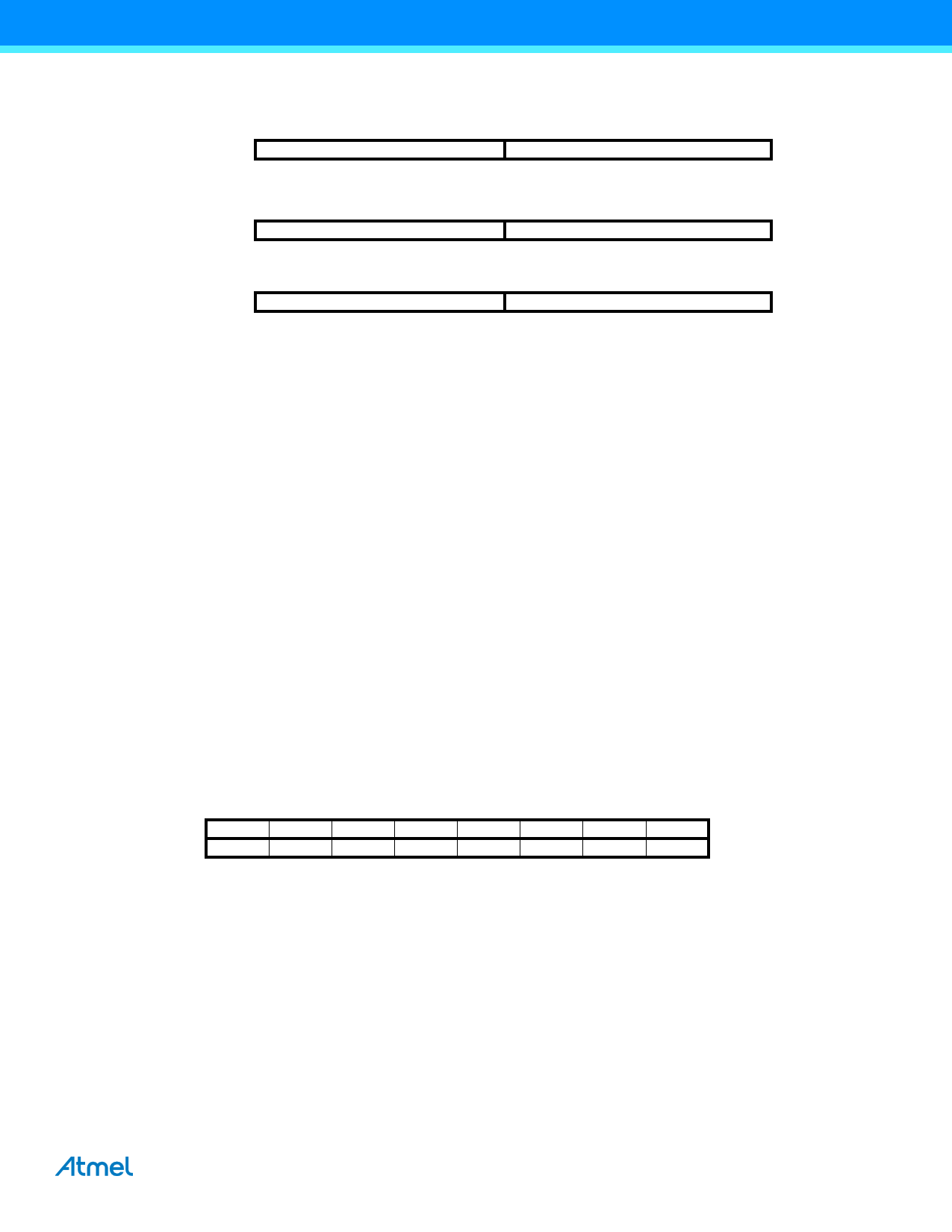

Figure 4-3. The X-, Y-, and Z-registers

X-register

15

7

R27 (0x1B)

XH

Y-register

Z-register

15

7

R29 (0x1D)

15

7

R31 (0x1F)

YH

ZH

0

07

R26 (0x1A)

07

R28 (0x1C)

7

R30 (0x1E)

XL

YL

ZL

0

0

0

0

0

0

In the different addressing modes these address registers have functions as fixed displacement, automatic incre-

ment, and automatic decrement (see the instruction set reference for details).

4.6 Stack Pointer

The Stack is mainly used for storing temporary data, for storing local variables and for storing return addresses

after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the

Stack is implemented as growing from higher memory locations to lower memory locations. This implies that a

Stack PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This

Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or inter-

rupts are enabled. The Stack Pointer must be set to point above 0x60. The Stack Pointer is decremented by one

when data is pushed onto the Stack with the PUSH instruction, and it is decremented by two when the return

address is pushed onto the Stack with subroutine call or interrupt. The Stack Pointer is incremented by one when

data is popped from the Stack with the POP instruction, and it is incremented by two when data is popped from the

Stack with return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is

implementation dependent. Note that the data space in some implementations of the AVR architecture is so small

that only SPL is needed. In this case, the SPH Register will not be present.

4.6.1

SPH and SPL — Stack Pointer Register

Bit

0x3E

0x3D

Read/Write

Read/Write

Initial Value

Initial Value

15

SP15

SP7

7

R/W

R/W

RAMEND

RAMEND

14

SP14

SP6

6

R/W

R/W

RAMEND

RAMEND

13

SP13

SP5

5

R/W

R/W

RAMEND

RAMEND

12

SP12

SP4

4

R/W

R/W

RAMEND

RAMEND

11

SP11

SP3

3

R/W

R/W

RAMEND

RAMEND

10

SP10

SP2

2

R/W

R/W

RAMEND

RAMEND

9

SP9

SP1

1

R/W

R/W

RAMEND

RAMEND

8

SP8

SP0

0

R/W

R/W

RAMEND

RAMEND

SPH

SPL

4.7 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the

CPU clock clkCPU, directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 4-4 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture

and the fast access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with

the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

ATtiny25/45/85 [DATASHEET]

2586Q–AVR–08/2013

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ATtiny45.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATtiny4 | 8-bit AVR Microcontroller | ATMEL Corporation |

| ATtiny40 | 8-bit tinyAVR Microcontroller | ATMEL Corporation |

| ATtiny4313 | 8-bit Microcontroller | ATMEL Corporation |

| ATtiny43U | Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |