|

|

PDF AT84AD004B Data sheet ( Hoja de datos )

| Número de pieza | AT84AD004B | |

| Descripción | Dual 8-bit 500 Msps ADC | |

| Fabricantes | e2v | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT84AD004B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Datasheet

AT84AD004B

Dual 8-bit 500 Msps ADC

1. Features

• Dual ADC with 8-bit Resolution

• 500 Msps Sampling Rate per Channel, 1 Gsps in interleaved Mode

• Single or 1:2 Demultiplexed Output

• LVDS Output Format (100Ω)

• 500 mVpp Analog Input (Differential Only)

• Differential or Single-ended 50Ω PECL/LVDS Compatible Clock Inputs

• Power Supply: 3.3V (Analog), 3.3V (Digital), 2.25V (Output)

• LQFP144 or LQFP-ep 144L Green packages

• Temperature Range:

– 0°C < Tamb < 70° C (Commercial Grade)

– –40°C < Tamb < 85° C (Industrial Grade)

• 3-wire Serial Interface

– 16-bit Data, 3-bit Address

– 1:2 or 1:1 Output Demultiplexer Ratio Selection

– Full or Partial Standby Mode

– Analog Gain (±1.5 dB) Digital Control

– Input Clock Selection

– Analog Input Switch Selection

– Binary or Gray Logical Outputs

– Synchronous Data Ready Reset

– Data Ready Delay Adjustable on Both Channels

– interleaving Functions:

• Offset and Gain (Channel to Channel) Calibration

• Digital Fine SDA (Fine Sampling Delay Adjust) on One Channel

– Internal Static or Dynamic Built-In Test (BIT)

2. Performance

• Low Power Consumption: 0.7W per Channel

• Power Consumption in Standby Mode: 120 mW

• 1 GHz Full Power Input Bandwidth (–3 dB)

• SNR = 45 dB Typ (7.2 ENOB), THD = –53 dBc, SFDR = –56 dBc at Fs = 500 Msps

Fin = 250 MHz

• 2-tone IMD3: –54 dBc (249 MHz, 251 MHz) at 500 Msps

• DNL = 0.25 LSB, INL = 0.5 LSB

• Low Bit Error Rate (10–18) at 500 Msps

e2v semiconductors SAS 2009

Visit our website: www.e2v.com

for the latest version of the datasheet

0818F–BDC–09/09

1 page

AT84AD004B

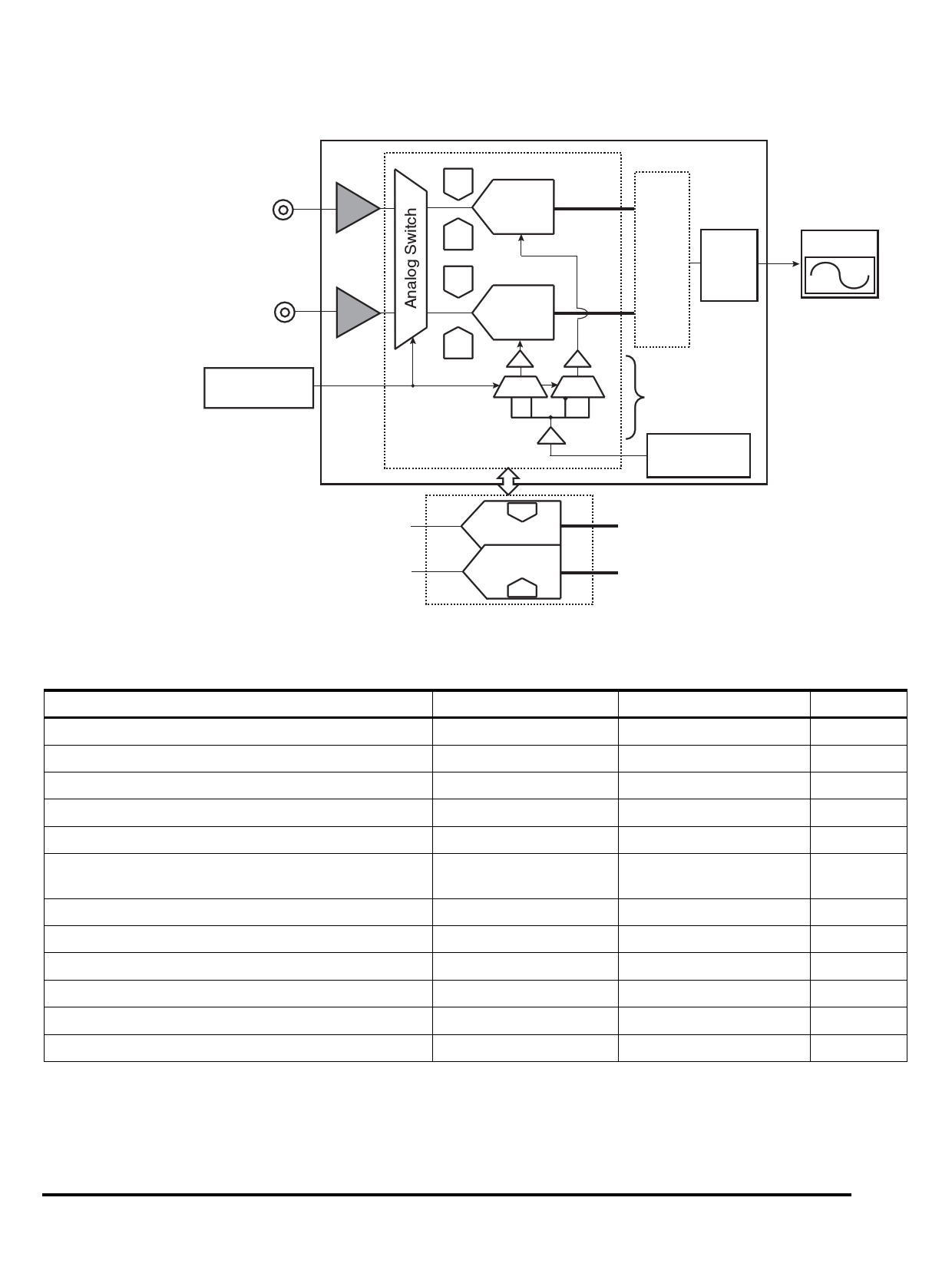

Figure 6-2. Dual Channel Digital Oscilloscope Application

Channel B

A

Channel A

A

Channel Mode

Selection

DAC

Gain

DAC

Offset

ADC B

DAC

Offset

DAC

Gain

ADC A

FISO

RAM

μP

Display

Clock

Selection

Timing

Circuit

DACs

Smart Dual

ADC

DACs

6.1 Absolute Maximum Ratings

Table 6-1. Absolute Maximum Ratings

Parameter

Analog positive supply voltage

Digital positive supply voltage

Output supply voltage

Maximum difference between VCCA and VCCD

Minimum VCCO

Analog input voltage

Digital input voltage

Clock input voltage

Maximum difference between VCLK and VCLKB

Maximum junction temperature

Storage temperature

Lead temperature (soldering 10s)

Symbol

VCCA

VCCD

VCCO

VCCA to VCCD

VCCO

VINI or VINIB

VINQ or VINQB

VD

VCLK or VCLKB

VCLK – VCLKB

TJ

Tstg

Tleads

Value

3.6

3.6

3.6

± 0.8

1.6

1/–1

–0.3 to VCCD + 0.3

–0.3 to VCCD + 0.3

–2 to 2

125

–65 to 150

300

Unit

V

V

V

V

V

V

V

V

V

°C

°C

°C

Note: Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are

within specified operating conditions. Long exposure to maximum ratings may affect device reliability.

e2v semiconductors SAS 2009

0818F–BDC–09/09

5

5 Page

AT84AD004B

Table 7-6. Switching Performances

Parameter

Symbol

Min

Typ

Max

Switching Performance and Characteristics – See “Timing Diagrams” on page 12.

Maximum operating clock frequency

FS 500

Minimum clock frequency (no transparent mode)

Minimum clock frequency (with transparent mode)

FS

10

1

Minimum clock pulse width [high]

(No transparent mode)

TC1 0.4 1 50

Minimum clock pulse width [low]

(No transparent mode)

TC2 0.4 1 50

Aperture delay: nominal mode with ISA & FiSDA

TA

1

Aperture uncertainty

Jitter

0.4

Data output delay between input clock and data

TDO

3.8

Data Ready Output Delay

TDR

3

Data Ready Reset to Data Ready

TRDR

2

Data Output Delay with Data Ready

TD2

1/Fs +

Tdrda

Data Ready (CLKO) Delay Adjust (140 ps steps)

Tdrda range

–560 to 420

Output skew

50 100

Output rise/fall time for DATA (20% – 80%)

TR/TF

300

350

500

Output rise/fall time for DATA READY (20% – 80%)

TR/TF

300

350

500

Data pipeline delay (nominal mode)

Data pipeline delay (nominal mode) in S/H

transparent mode

TPD

3 (port B)

3.5 (port A, 1:1 DMUX mode)

4 (port A, 1:2 DMUX mode)

2.5 (port B)

3 (port A, 1:1 DMUX mode)

3.5 (port A, 1:2 DMUX mode)

DDRB recommended pulse width

1

Unit

Msps

Msps

Ksps

ns

ns

ns

ps (rms)

ns

ns

ns

ps

ps

ps

ps

ps

Clock cycles

ns

e2v semiconductors SAS 2009

0818F–BDC–09/09

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT84AD004B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT84AD004 | DUAL 8-BIT 500 MSPS ADC | ATMEL Corporation |

| AT84AD004B | Dual 8-bit 500 Msps ADC | e2v |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |