|

|

PDF BT8960EPF Data sheet ( Hoja de datos )

| Número de pieza | BT8960EPF | |

| Descripción | Single-Chip 2B1Q Transceiver | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de BT8960EPF (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Bt8960

Single-Chip 2B1Q Transceiver

The Bt8960 is a full-duplex 2B1Q transceiver based on Rockwell’s HDSL technol-

ogy. It supports Nx64 kbps transmission of more than 18,000 feet over 26 AWG

copper telephone wire without repeaters. Small size and low power dissipation

make the Bt8960 ideal for line-powered voice pairgain systems capable of provid-

ing four or six clear 64 kbps channels.

The Bt8960 is a highly integrated device that includes all of the active circuitry

needed for a complete 2B1Q transceiver. In the receive portion of the Bt8960, a

variable gain amplifier optimizes the signal level according to the dynamic range

of the analog-to-digital converter. Once the signal is digitized, sophisticated adap-

tive echo cancellation, equalization, and detection DSP algorithms reproduce the

originally transmitted far-end signal.

In the transmitter, the transmit source and scrambler operation is programma-

ble via the microcomputer interface. A highly linear digital-to-analog converter

with programmable gain, sets the transmission power for optimal performance. A

pulse-shaping filter and a low distortion line driver generate the signal character-

istics needed to drive a large range of subscriber lines at low-bit error rates.

Startup and performance monitoring operations are controlled via the micro-

processor interface. C-language source code supporting these operations is sup-

plied under a no-fee license agreement from Rockwell. The Bt8960 includes a

glueless interface to both Intel and Motorola microprocessors.

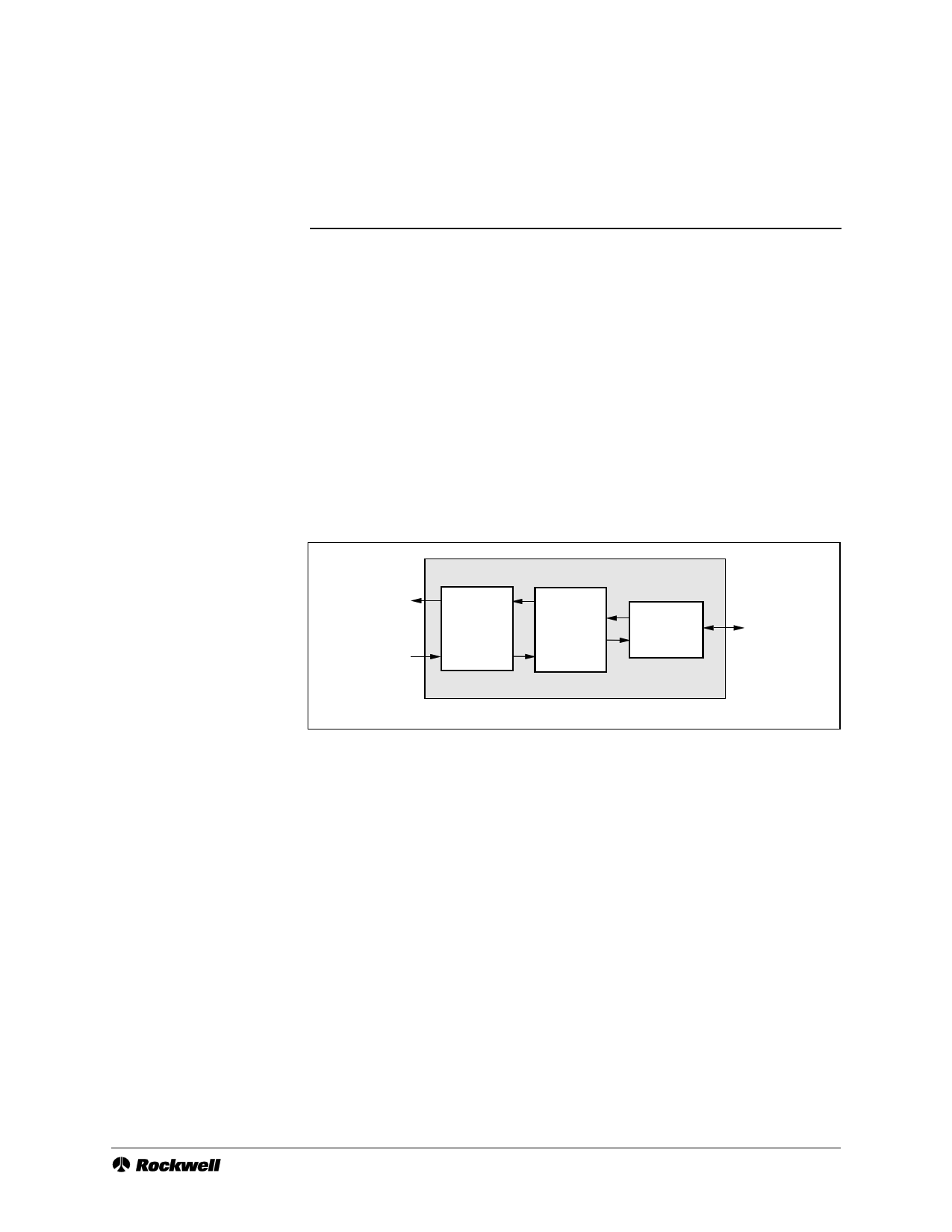

Functional Block Diagram

Analog

Receive

Variable

Gain

Amplifier

Analog-

to-Digital

Converter

Digital

Signal

Processor

MPU

Bus

Analog

Transmit

Microcomputer

Interface

Line

Driver

Pulse-

Shaping

Filter

Program-

mable

Gain

DAC

Recovered

Data and

Clock

Framer/

Channel

Unit

Interface

Transmit

Data

Distinguishing Features

• Single-chip 2B1Q transceiver solution

• All 2B1Q transceiver functions inte-

grated into a single monolithic device

– Receiver gain control and A/D

converter

– DSP functions including echo

cancellation, equalization, timing

recovery, and symbol detection

– Programmable gain transmit DAC,

pulse-shaping filter and line driver

• Supports operation from 160 to 416

kbps

• Capable of transceiving over the ANSI

T1.601 and ETSI ETR 080 ISDN

test loops

• Flexible Monitoring and Control

– Glueless interface to Intel 8051 and

Motorola 68302 processors

– Access to embedded filters, perfor-

mance meters and timers

• Backwards compatible with Bt8952

software API commands

• JTAG/IEEE Std 1149.1-1990

compliant

• Single +5 V power supply

operation

• 600 mW power consumption at 288

kbps (typical)

• 100-pin PQFP package

• –40˚C to +85˚C operation

Applications

• Voice/data pairgain systems

• Internet connectivity

• ISDN basic-rate interface

concentrators

• ISDN H0 transport

• Extended range fractional T1/E1

• Cellular/microcellular base stations

• Personal Communications Systems

(PCS) radio ports and cell switches

1 page

Bt8960

Single-Chip 2B1Q Transceiver

Table of Contents

3.2.10 0x09—Nonlinear Echo Canceller Modes Register (nonlinear_ec_modes) . . . . . . 49

3.2.11 0x0A—Decision Feedback Equalizer Modes Register (dfe_modes) . . . . . . . . . . . 50

3.2.12 0x0B—Transmitter Modes Register (transmitter_modes) . . . . . . . . . . . . . . . . . . 50

3.2.13 0x0C—Timer Restart Register (timer_restart) . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.2.14 0x0D—Timer Enable Register (timer_enable). . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.2.15 0x0E—Timer Continuous Mode Register (timer_continuous) . . . . . . . . . . . . . . . 53

3.2.16 0x0F—Test Register (reserved2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.2.17 0x10, 0x11—Startup Timer 1 Interval Register (sut1_low, sut1_high). . . . . . . . . 53

3.2.18 0x12, 0x13—Startup Timer 2 Interval Register (sut2_low, sut2_high). . . . . . . . . 53

3.2.19 0x14, 0x15—Startup Timer 3 Interval Register (sut3_low, sut3_high). . . . . . . . . 53

3.2.20 0x16, 0x17—Startup Timer 4 Interval Register (sut4_low, sut4_high). . . . . . . . . 53

3.2.21 0x18, 0x19—Meter Timer Interval Register (meter_low, meter_high) . . . . . . . . . 53

3.2.22 0x20—Test Register (reserved9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.2.23 0x1A, 0x1B—SNR Alarm Timer Interval Register

(snr_timer_low, snr_timer_high) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.2.24 0x1C, 0x1D—General Purpose Timer 3 Interval Register (t3_low, t3_high) . . . . . 54

3.2.25 0x1E, 0x1F—General Purpose Timer 4 Interval Register (t4_low, t4_high) . . . . . 54

3.2.26 0x21—ADC Control Register (adc_control) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.2.27 0x22—PLL Modes Register (pll_modes) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.2.28 0x23—Test Register (reserved10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2.29 0x24, 0x25—Timing Recovery PLL Phase Offset Register (pll_phase_offset_low,

pll_phase_offset_high) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2.30 0x26, 0x27—Receiver DC Offset Register (dc_offset_low, dc_offset_high) . . . . . 57

3.2.31 0x28—Transmitter Calibration Register (tx_calibrate) . . . . . . . . . . . . . . . . . . . . . 57

3.2.32 0x29—Transmitter Gain Register (tx_gain) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3.2.33 0x2A, 0x2B—Noise-Level Histogram Threshold Register

(noise_histogram_th_low, noise_histogram_th_high) . . . . . . . . . . . . . . . . . . . 59

3.2.34 0x2C, 0x2D—Error Predictor Pause Threshold Register

(ep_pause_th_low, ep_pause_th_high). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.2.35 0x2E—Scrambler Synchronization Threshold Register (scr_sync_th) . . . . . . . . . 59

3.2.36 0x30, 0x31—Far-End High Alarm Threshold Register

(far_end_high_alarm_th_low, far_end_high_alarm_th_high) . . . . . . . . . . . . . . 59

3.2.37 0x32, 0x33—Far-End Low Alarm Threshold Register

(far_end_low_alarm_th_low, far_end_low_alarm_th_high) . . . . . . . . . . . . . . . 59

3.2.38 0x34, 0x35—SNR Alarm Threshold Register (snr_alarm_th_low,

snr_alarm_th_high). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.2.39 0x36, 0x37—Cursor Level Register (cursor_level_low, cursor_level_high) . . . . . 60

3.2.40 0x38, 0x39—DAGC Target Register (dagc_target_low, dagc_target_high). . . . . . 60

3.2.41 0x3A—Symbol Detector Modes Register (detector_modes) . . . . . . . . . . . . . . . . 61

3.2.42 0x3B—Peak Detector Delay Register (peak_detector_delay) . . . . . . . . . . . . . . . . 62

3.2.43 0x3C—Digital AGC Modes Register (dagc_modes) . . . . . . . . . . . . . . . . . . . . . . . 62

3.2.44 0x3D—Feed Forward Equalizer Modes Register (ffe_modes). . . . . . . . . . . . . . . . 63

3.2.45 0x3E—Error Predictor Modes Register (ep_modes) . . . . . . . . . . . . . . . . . . . . . . 63

3.2.46 0x40, 0x41—Phase Detector Meter Register (pdm_low, pdm_high) . . . . . . . . . . 64

3.2.47 0x42—Overflow Meter Register (overflow_meter) . . . . . . . . . . . . . . . . . . . . . . . . 64

3.2.48 0x44, 0x45—DC Level Meter Register (dc_meter_low, dc_meter_high) . . . . . . . 64

N8960DSB

v

5 Page

1.0 System Overview

1.1 Functional Summary

The Bt8960 2B1Q transceiver is an integral component of Rockwell's telecom-

munications product line. The major building blocks of a 2B1Q terminal are

shown in Figure 1-1.

Figure 1-1. 2B1Q Terminal

Receive

Data

Transmit

Data

Framer/

Channel

Unit

Bt8960

Transceiver

Transformer

and Hybrid

Twisted

Pair

N8960DSB

1

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet BT8960EPF.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BT8960EPF | Single-Chip 2B1Q Transceiver | ETC |

| BT8960EPF | Single-Chip 2B1Q Transceiver | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |