|

|

PDF AT90S2323-10SC Data sheet ( Hoja de datos )

| Número de pieza | AT90S2323-10SC | |

| Descripción | 8-Bit Microcontroller with 2K Bytes of In-System Programmable Flash | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT90S2323-10SC (archivo pdf) en la parte inferior de esta página. Total 64 Páginas | ||

|

No Preview Available !

Features

• Utilizes the AVR® RISC Architecture

• AVR – High-performance and Low-power RISC Architecture

– 118 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General-purpose Working Registers

– Up to 10 MIPS Throughput at 10 MHz

• Data and Nonvolatile Program Memory

– 2K Bytes of In-System Programmable Flash

Endurance: 1,000 Write/Erase Cycles

– 128 Bytes Internal RAM

– 128 Bytes of In-System Programmable EEPROM

Endurance: 100,000 Write/Erase Cycles

– Programming Lock for Flash Program and EEPROM Data Security

• Peripheral Features

www.DataShee–t4UO.ncoem8-bit Timer/Counter with Separate Prescaler

– Programmable Watchdog Timer with On-chip Oscillator

– SPI Serial Interface for In-System Programming

• Special Microcontroller Features

– Low-power Idle and Power-down Modes

– External and Internal Interrupt Sources

– Power-on Reset Circuit

– Selectable On-chip RC Oscillator

• Specifications

– Low-power, High-speed CMOS Process Technology

– Fully Static Operation

• Power Consumption at 4 MHz, 3V, 25°C

– Active: 2.4 mA

– Idle Mode: 0.5 mA

– Power-down Mode: <1 µA

• I/O and Packages

– Three Programmable I/O Lines for AT90S/LS2323

– Five Programmable I/O Lines for AT90S/LS2343

– 8-pin PDIP and SOIC

• Operating Voltages

– 4.0 - 6.0V for AT90S2323/AT90S2343

– 2.7 - 6.0V for AT90LS2323/AT90LS2343

• Speed Grades

– 0 - 10 MHz for AT90S2323/AT90S2343-10

– 0 - 4 MHz for AT90LS2323/AT90LS2343-4

– 0 - 1 MHz for AT90LS2343-1

8-bit

Microcontroller

with 2K Bytes of

In-System

Programmable

Flash

AT90S2323

AT90LS2323

AT90S2343

AT90LS2343

Pin Configuration

PDIP/SOIC

RESET

(CLOCK) PB3

PB4

GND

1

2

3

4

8 VCC

RESET 1

7 PB2 (SCK/T0)

XTAL1 2

6 PB1 (MISO/INT0) XTAL2 3

5 PB0 (MOSI)

GND 4

8 VCC

7 PB2 (SCK/T0)

6 PB1 (MISO/INT0)

5 PB0 (MOSI)

AT90S/LS2343

AT90S/LS2323

Rev. 1004D–09/01

1

1 page

Pin Descriptions

AT90S/LS2343

VCC

GND

Port B (PB4..PB0)

www.DataSheet4U.com

RESET

CLOCK

Clock Options

Crystal Oscillator

AT90S/LS2323/2343

Supply voltage pin.

Ground pin.

Port B is a 5-bit bi-directional I/O port with internal pull-up resistors. The Port B output

buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source

current if the pull-up resistors are activated.

Port B also serves the functions of various special features.

Port pins can provide internal pull-up resistors (selected for each bit). The Port B pins

are tri-stated when a reset condition becomes active.

Reset input. An external reset is generated by a low level on the RESET pin. Reset

pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter

pulses are not guaranteed to generate a reset.

Clock signal input in external clock mode.

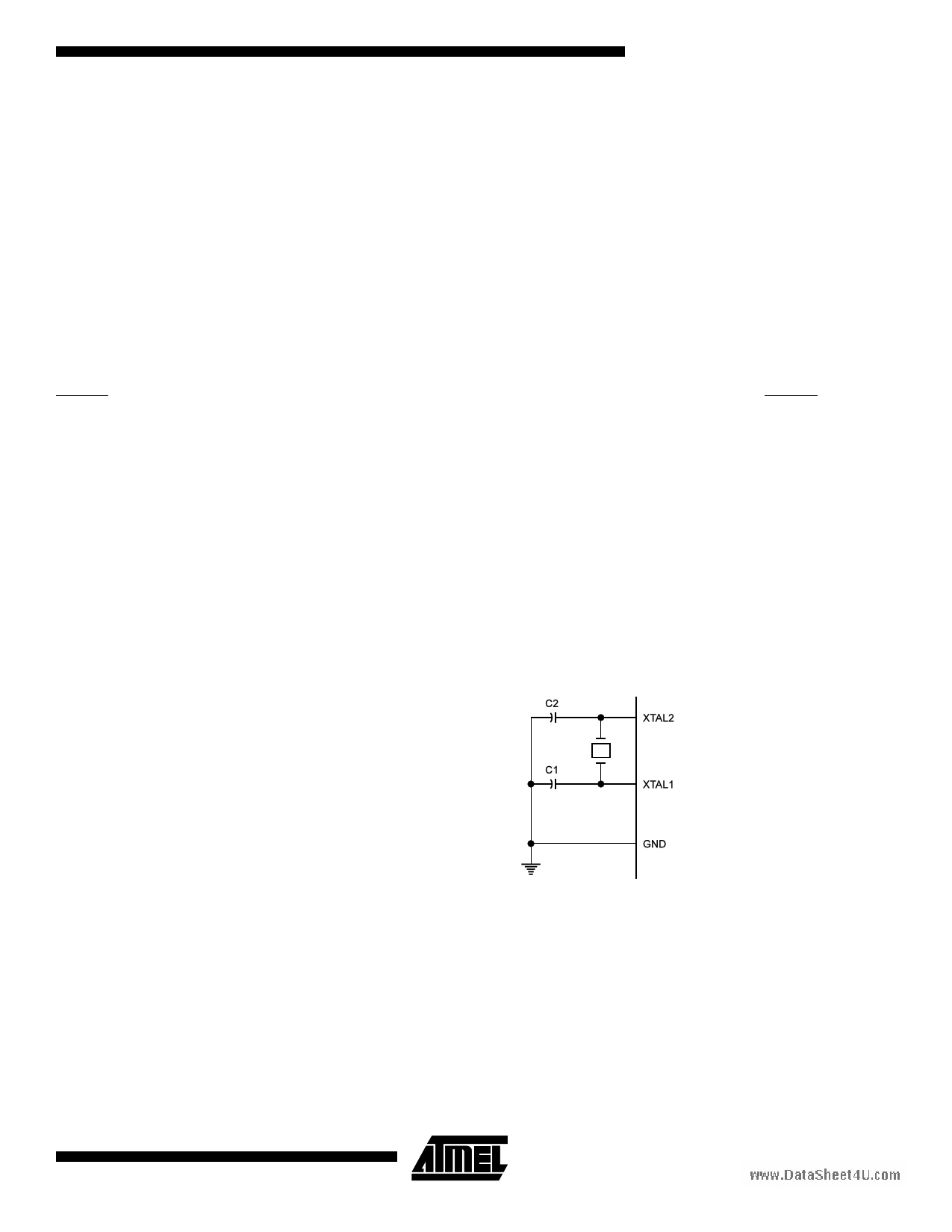

The AT90S/LS2323 contains an inverting amplifier that can be configured for use as an

On-chip oscillator, as shown in Figure 3. XTAL1 and XTAL2 are input and output

respectively. Either a quartz crystal or a ceramic resonator may be used. It is recom-

mended that the AT90S/LS2343 be used if an external clock source is used, since this

gives an extra I/O pin.

Figure 3. Oscillator Connection

External Clock

1004D–09/01

The AT90S/LS2343 can be clocked by an external clock signal, as shown in Figure 4, or

by the On-chip RC oscillator. This RC oscillator runs at a nominal frequency of 1 MHz

(VCC = 5V). A fuse bit (RCEN) in the Flash memory selects the On-chip RC oscillator as

the clock source when programmed (“0”). The AT90S/LS2343 is shipped with this bit

programmed. The AT90S/LS2343 is recommended if an external clock source is used,

because this gives an extra I/O pin.

The AT90S/LS2323 can be clocked by an external clock as well, as shown in Figure 4.

No fuse bit selects the clock source for AT90S/LS2323.

5

5 Page

SRAM Data Memory

www.DataSheet4U.com

AT90S/LS2323/2343

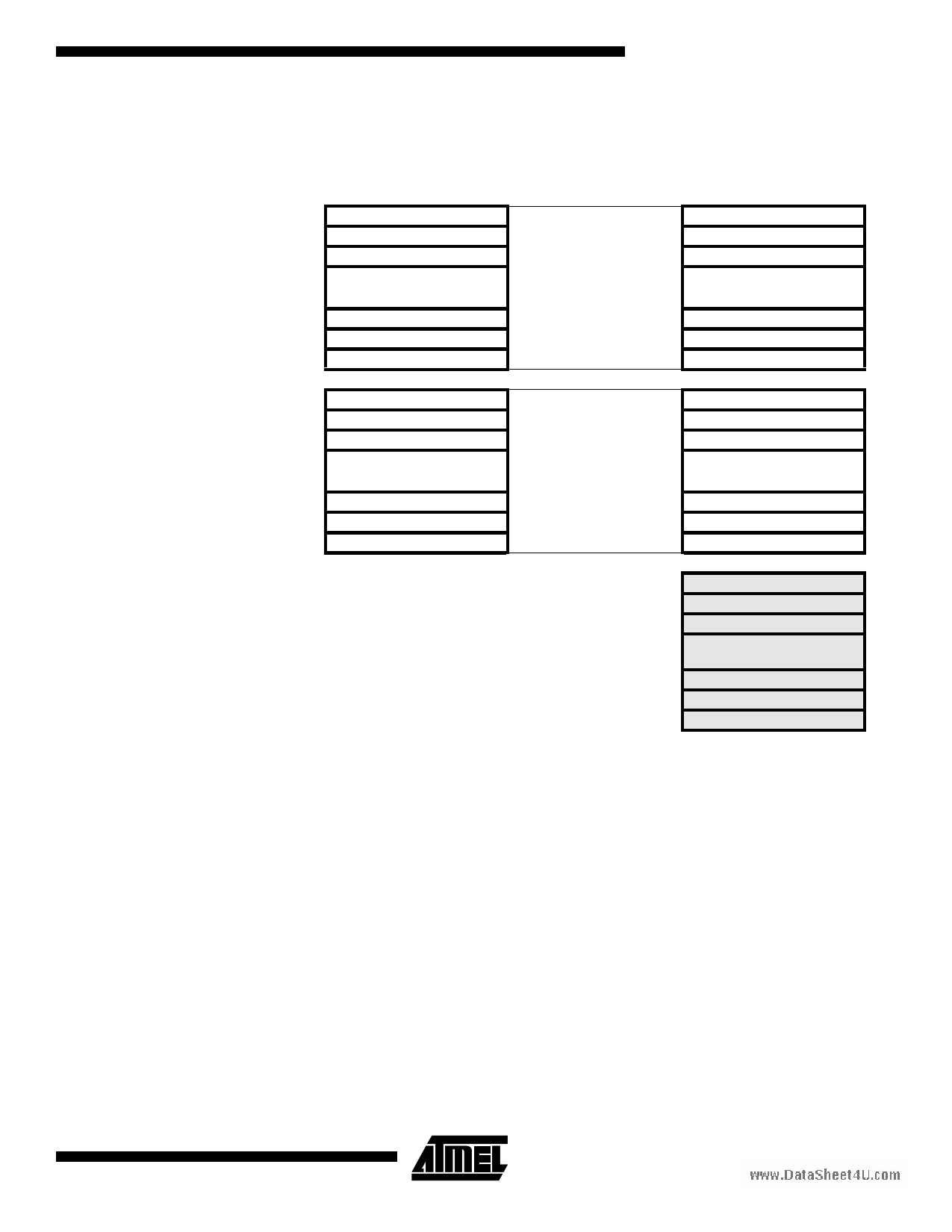

Figure 9 shows how the AT90S2323/2343 Data Memory is organized.

Figure 9. SRAM Organization

Register File

R0

R1

R2

…

Data Address Space

$00

$01

$02

…

R29

R30

R31

I/O Registers

$00

$01

$02

…

$1D

$1E

$1F

$20

$21

$22

…

$3D $5D

$3E $5E

$3F $5F

Internal SRAM

$60

$61

$62

…

$DD

$DE

$DF

The 224 data memory locations address the Register file, I/O memory and the data

SRAM. The first 96 locations address the Register file + I/O memory, and the next 128

locations address the data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Dis-

placement, Indirect, Indirect with Pre-decrement and Indirect with Post-increment. In the

register file, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data address space.

The Indirect with Displacement mode features 63 address locations reached from the

base address given by the Y- and Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-

increment, the address registers X, Y, and Z are used and decremented and

incremented.

The 32 general-purpose working registers, 64 I/O registers and the 128 bytes of data

SRAM in the AT90S2323/2343 are all directly accessible through all these addressing

modes.

1004D–09/01

11

11 Page | ||

| Páginas | Total 64 Páginas | |

| PDF Descargar | [ Datasheet AT90S2323-10SC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT90S2323-10SC | 8-Bit Microcontroller with 2K Bytes of In-System Programmable Flash | ATMEL Corporation |

| AT90S2323-10SI | 8-Bit Microcontroller with 2K Bytes of In-System Programmable Flash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |