|

|

PDF AT91SAM7S64-AI Data sheet ( Hoja de datos )

| Número de pieza | AT91SAM7S64-AI | |

| Descripción | AT91 ARM THUMB-BASED MICROCONTROLLERS | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT91SAM7S64-AI (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Features

• Incorporates the ARM7TDMI® ARM® Thumb® Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

– Leader in MIPS/Watt

– Embedded ICE In-circuit Emulation, Debug Communication Channel Support

• 64 Kbytes of Internal High-speed Flash, Organized in 512 Pages of 128 Bytes

– Single Cycle Access at Up to 30 MHz in Worst Case Conditions,

Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed

– Page Programming Time: 4 ms, Including Page Auto-erase, Full Erase Time: 10 ms

– 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities,

Flash Security Bit

– Fast Flash Programming Interface for High Volume Production

• 16 Kbytes of Internal High-speed SRAM, Single-cycle Access at Maximum Speed

• Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

• Reset Controller (RSTC)

– Based on Power-on Reset and Low-power Factory-calibrated Brownout Detector

– Provides External Reset Signal Shaping and Reset Source Status

• Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

• Power Management Controller (PMC)

– Software Power Optimization Capabilities, Including Slow Clock Mode (Down to

500 Hz) and Idle Mode

– Three Programmable External Clock Signals

• Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt

Protected

• Debug Unit (DBGU)

www.DataSheet4U.com

– 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention

• Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter

• Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signals to the System

– Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

• Real-time Timer (RTT)

– 32-bit Free-running Counter with Alarm

– Runs Off the Internal RC Oscillator

• One Parallel Input/Output Controller (PIOA)

– Thirty-two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up resistor and Synchronous Output

• Eleven Peripheral Data Controller (PDC) Channels

• One USB 2.0 Full Speed (12 Mbits per second) Device Port

– On-chip Transceiver, 328-byte Configurable Integrated FIFOs

• One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

• Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Full Modem Line Support on USART1

• One Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

AT91 ARM®

Thumb®-based

Microcontrollers

AT91SAM7S64

Preliminary

6070A–ATARM–28-Oct-04

1 page

AT91SAM7S64 Preliminary

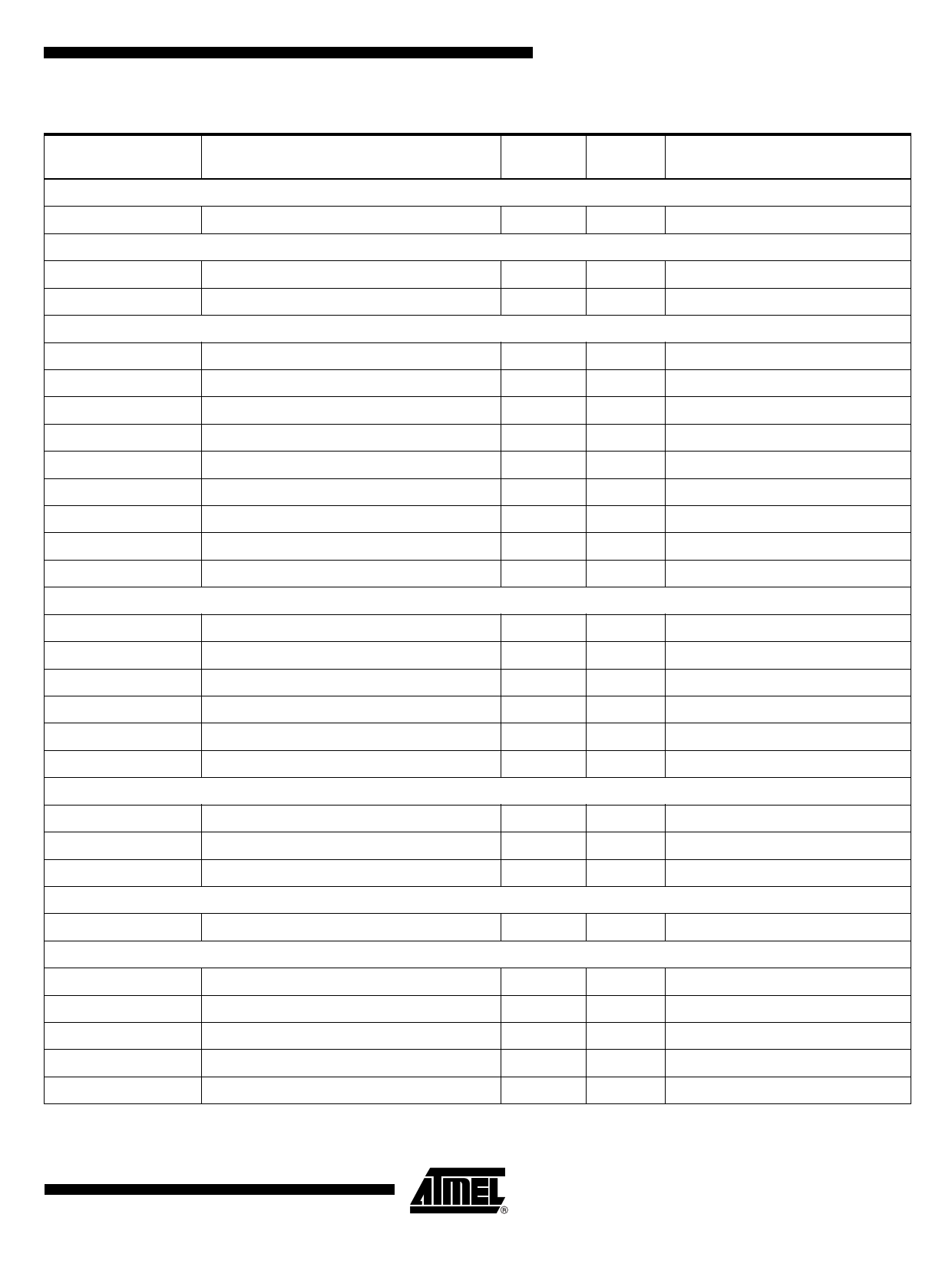

Table 1. Signal Description List (Continued)

Signal Name

PA0 - PA31

DDM

DDP

SCK0 - SCK1

TXD0 - TXD1

RXD0 - RXD1

RTS0 - RTS1

CTS0 - CTS1

DCD1

DTR1

DSR1

RI1

TD

RD

TK

RK

TF

RF

TCLK0 - TCLK2

TIOA0 - TIOA2

TIOB0 - TIOB2

PWM0 - PWM3

MISO

MOSI

SPCK

NPCS0

NPCS1-NPCS3

Function

Type

PIO

Parallel IO Controller A

I/O

USB Device Port

USB Device Port Data -

Analog

USB Device Port Data +

Analog

USART

Serial Clock

I/O

Transmit Data

I/O

Receive Data

Input

Request To Send

Output

Clear To Send

Input

Data Carrier Detect

Input

Data Terminal Ready

Output

Data Set Ready

Input

Ring Indicator

Input

Synchronous Serial Controller

Transmit Data

Output

Receive Data

Input

Transmit Clock

I/O

Receive Clock

I/O

Transmit Frame Sync

I/O

Receive Frame Sync

I/O

Timer/Counter

External Clock Inputs

Input

I/O Line A

I/O

I/O Line B

I/O

PWM Controller

PWM Channels

Output

SPI

Master In Slave Out

I/O

Master Out Slave In

I/O

SPI Serial Clock

I/O

SPI Peripheral Chip Select 0

I/O

SPI Peripheral Chip Select 1 to 3

Output

Active

Level

Low

Low

Comments

Pulled-up input at reset

6070A–ATARM–28-Oct-04

5

5 Page

AT91SAM7S64 Preliminary

Processor and Architecture

ARM7TDMI Processor

• RISC processor based on ARMv4T Von Neumann architecture

– Runs at up to 55 MHz, providing 0.9 MIPS/MHz

• Two instruction sets

– ARM® high-performance 32-bit instruction set

– Thumb® high code density 16-bit instruction set

• Three-stage pipeline architecture

– Instruction Fetch (F)

– Instruction Decode (D)

– Execute (E)

Debug and Test Features •

•

•

Integrated embedded in-circuit emulator

– Two watchpoint units

– Test access port accessible through a JTAG protocol

– Debug communication channel

Debug Unit

– Two-pin UART

– Debug communication channel interrupt handling

– Chip ID Register

IEEE1149.1 JTAG Boundary-scan on all digital pins

Memory Controller

• Bus Arbiter

– Handles requests from the ARM7TDMI and the Peripheral Data Controller

• Address decoder provides selection signals for

– Three internal 1 Mbyte memory areas

– One 256 Mbyte embedded peripheral area

• Abort Status Registers

– Source, Type and all parameters of the access leading to an abort are saved

– Facilitates debug by detection of bad pointers

• Misalignment Detector

– Alignment checking of all data accesses

– Abort generation in case of misalignment

• Remap Command

– Remaps the SRAM in place of the embedded non-volatile memory

– Allows handling of dynamic exception vectors

• Embedded Flash Controller

– Embedded Flash interface, up to three programmable wait states

– Prefetch buffer, bufferizing and anticipating the 16-bit requests, reducing the

required wait states

– Key-protected program, erase and lock/unlock sequencer

– Single command for erasing, programming and locking operations

– Interrupt generation in case of forbidden operation

6070A–ATARM–28-Oct-04

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet AT91SAM7S64-AI.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT91SAM7S64-AI | AT91 ARM THUMB-BASED MICROCONTROLLERS | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |