|

|

PDF AD6623 Data sheet ( Hoja de datos )

| Número de pieza | AD6623 | |

| Descripción | 4-Channel/ 104 MSPS Digital Transmit Signal Processor TSP | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD6623 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

a

4-Channel, 104 MSPS Digital

Transmit Signal Processor (TSP)

AD6623

FEATURES

Pin Compatible to the AD6622

18-Bit Parallel Digital IF Output

Real or Interleaved Complex

18-Bit Bidirectional Parallel Digital IF Input/Output

Allows Cascade of Chips for Additional Channels

Clipped or Wrapped Over Range

Two’s Complement or Offset Binary Output

Four Independent Digital Transmitters in Single Package

RAM Coefficient Filter (RCF)

Programmable IF and Modulation for Each Channel

Programmable Interpolating RAM Coefficient Filter

p/4-DQPSK Differential Phase Encoder

3p/8-PSK Linear Encoder

8-PSK Linear Encoder

Programmable GMSK Look-Up Table

Programmable QPSK Look-Up Table

All-Pass Phase Equalizer

Programmable Fine Scaler

Programmable Power Ramp Unit

High Speed CIC Interpolating Filter

Digital Resampling for Noninteger Interpolation Rates

NCO Frequency Translation

Spurious Performance Better than –100 dBc

Separate 3-Wire Serial Data Input for Each Channel

Bidirectional Serial Clocks and Frames

Microprocessor Control

2.5 V CMOS Core, 3.3 V Outputs, 5 V Inputs

JTAG Boundary Scan

APPLICATIONS

Cellular/PCS Base Stations

Micro/Pico Cell Base Stations

Wireless Local Loop Base Stations

Multicarrier, Multimode Digital Transmit

GSM, EDGE, IS136, PHS, IS95, TDS CDMA, UMTS,

CDMA2000

Phased Array Beam Forming Antennas

Software Defined Radio

Tuning Resolution Better than 0.025 Hz

Real or Complex Outputs

FUNCTIONAL BLOCK DIAGRAM

SDINA

SDFIA

SDFOA

SCLKA

SDINB

SDFIB

SDFOB

SCLKB

SDINC

SDFIC

SDFOC

SCLKC

SDIND

SDFID

SDFOD

SCLKD

NCO = NUMERICALLY CONTROLLED

OSCILLATOR/TUNER

SPORT

DATA

RAM

I

COEFFICIENT Q

FILTER

SCALER I

AND Q

POWER

RAMP

I

CIC5

FILTER

Q

I

RCIC2

FILTER

Q

CHAN A

NCO

QIN

IN

[17–0]

SPORT

DATA

RAM

I

COEFFICIENT Q

FILTER

SCALER I

AND Q

POWER

RAMP

I

CIC5

FILTER

Q

I

RCIC2

FILTER

Q

SPORT

DATA

RAM

I

COEFFICIENT Q

FILTER

SCALER I

AND Q

POWER

RAMP

I

CIC5

FILTER

Q

I

RCIC2

FILTER

Q

SPORT

DATA

RAM

I

COEFFICIENT Q

FILTER

SCALER I

AND Q

POWER

RAMP

I

CIC5

FILTER

Q

I

RCIC2

FILTER

Q

CHAN B

NCO

SUMMATION

CHAN C

NCO

SYNC

4

CHAN D

NCO

OEN

QOUT

OUT

[17:0]

JTAG

MICROPORT

REV. 0

TDL TDO TMS TCK TRST

D[7:0] DS DTACK RW MODE A[2:0] CS

CLK RESET

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

1 page

GENERAL TIMING CHARACTERISTICS1, 2

Parameter (Conditions)

Temp

Test

Level

AD6623AS

Min Typ Max

CLK Timing Requirements:

tCLK

tCLKL

tCLKH

CLK Period

CLK Width Low

CLK Width High

RESET Timing Requirement:

tRESL

RESET Width Low

Full I

Full IV

Full IV

Full I

9.6

3

3

30.0

0.5 × tCLK

Input Data Timing Requirements:

tSI INOUT[17:0], QIN to ↑CLK Setup Time Full IV

tHI INOUT[17:0], QIN to ↑CLK Hold Time Full IV

Output Data Timing Characteristics:

tDO ↑CLK to OUT[17:0], INOUT[17:0],

QOUT Output Delay Time

tDZO OEN HIGH to OUT[17:0] Active

Full IV

Full IV

1

2

2

3

6

7.5

SYNC Timing Requirements:

tSS SYNC(0, 1, 2, 3) to ↑CLK Setup Time

tHS SYNC(0, 1, 2, 3) to ↑CLK Hold Time

Full IV

Full IV

1

2

Master Mode Serial Port Timing Requirements (SCS = 0):

Switching Characteristics3

tDSCLK1

tDSCLKH

tDSCLKL

↑CLK to ↑SCLK Delay (divide by 1)

↑CLK to ↑SCLK Delay (for any other divisor)

↑CLK to ↓SCLK Delay

(divide by 2 or even number)

tDSCLKLL

↓CLK to ↓SCLK Delay

(divide by 3 or odd number)

Channel is Self-Framing

tSSDI0

tHSDI0

tDSFO0A

SDIN to ↑SCLK Setup Time

SDIN to ↑SCLK Hold Time

↑SCLK to SDFO Delay

Channel is External-Framing

tSSFI0

tHSFI0

tSSDI0

tHSDI0

tDSFO0B

SDFI to ↑SCLK Setup Time

SDFI to ↑SCLK Hold Time

SDIN to ↑SCLK Setup Time

SDIN to ↑SCLK Hold Time

↑SCLK to SDFO Delay

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

IV

IV

IV

IV

IV

IV

4

5

3.5

4

1.7

0

0.5

2

0

2

0

0.5

Slave Mode Serial Port Timing Requirements (SCS = 1):

Switching Characteristics3

tSCLK

tSCLKL

tSCLKH

SCLK Period

SCLK Low Time

SCLK High Time

Channel is Self-Framing

Full IV

Full IV

Full IV

3.5

3.5

tSSDH

tHSDH

tDSFO1

SDIN to ↑SCLK Setup Time

SDIN to ↑SCLK Hold Time

↑SCLK to SDFO Delay

Channel is External-Framing

Full IV

Full IV

Full IV

1

2.5

4

tSSFI1

tHSFI1

tSSDI1

tHSDI1

tDSFO1

SDFI to ↑ SCLK Setup Time

SDFI to ↑SCLK Hold Time

SDIN to ↑SCLK Setup Time

SDIN to ↑SCLK Hold Time

↓SCLK to SDFO Delay

Full IV

Full IV

Full IV

Full IV

Full IV

2

1

1

2.5

10

NOTES

1All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2CLOAD = 40 pF on all outputs (unless otherwise specified).

3The timing parameters for SCLK, SDIN, SDFI, SDFO, and SYNC apply to all four channels (A, B, C, and D).

Specifications subject to change without notice.

10.5

13

9

10

3.5

3

2 ؋ tCLK

10

AD6623

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

REV. 0

–5–

5 Page

GND 103

VDD 104

SDFIA 105

TMS 106

TDO 107

TDI 108

SCLKA 109

VDDIO 110

SDFOA 111

SDINA 112

SCLKB 113

SDFOB 114

SDFIB 115

GND 116

SDFIC 117

SDINB 118

SCLKC 119

SDFOC 120

SDINC 121

VDDIO 122

SCLKD 123

SDFOD 124

SDIND 125

SDFID 126

VDD 127

GND 128

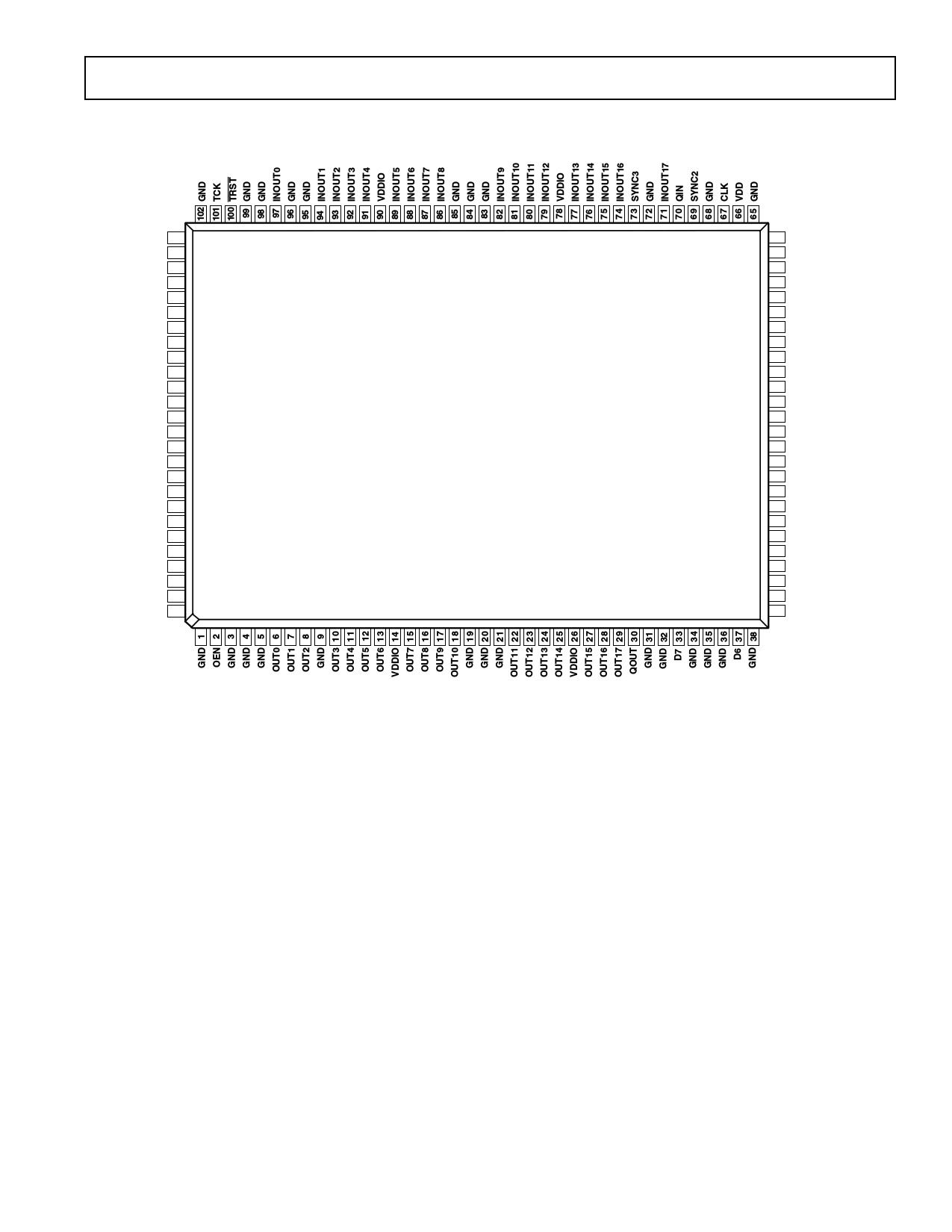

PIN CONFIGURATION

128-Lead MQFP

AD6623

TOP VIEW

(Not to Scale)

AD6623

64 GND

63 SYNC1

62 SYNC0

61 RESET

60 CS

59 VDD

58 A0

57 A1

56 A2

55 MODE

54 GND

53 GND

52 GND

51 RW(WR)

50 DTACK(RDY)

49 DS(RD)

48 D0

47 VDD

46 D1

45 D2

44 D3

43 D4

42 GND

41 VDDIO

40 D5

39 GND

REV. 0

–11–

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD6623.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD6620 | 65 MSPS Digital Receive Signal Processor | Analog Devices |

| AD6622 | Four-Channel/ 75 MSPS Digital Transmit Signal Processor TSP | Analog Devices |

| AD6623 | 4-Channel/ 104 MSPS Digital Transmit Signal Processor TSP | Analog Devices |

| AD6624 | 80 MSPS Digital Receive Signal Processor | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |