|

|

PDF AT27BV1024-15JI Data sheet ( Hoja de datos )

| Número de pieza | AT27BV1024-15JI | |

| Descripción | 1 Megabit 64K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT27BV1024-15JI (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

AT27BV1024

Features

Fast Read Access Time - 90 ns

•• Dual Voltage Range Operation

Unregulated Battery Power Supply Range, 2.7V to 3.6V

or Standard 5V ± 10% Supply Range

Pin Compatible with JEDEC Standard AT27C1024

•• Low Power CMOS Operation

20 µA max. (less than 1 µA typical) Standby for VCC = 3.6V

29 mW max. Active at 5 MHz for VCC = 3.6V

• JEDEC Standard Surface Mount Packages

44-Lead PLCC

40-Lead TSOP (10 x 14mm)

• High Reliability CMOS Technology

2,000V ESD Protection

200 mA Latchup Immunity

• Rapid™ Programming Algorithm - 100 µs/word (typical)

• CMOS and TTL Compatible Inputs and Outputs

JEDEC Standard for LVTTL and LVBO

Integrated Product Identification Code

•• Commercial and Industrial Temperature Ranges

Description

The AT27BV1024 is a high performance, low power, low voltage 1,048,576 bit one-

time programmable read only memory (OTP EPROM) organized as 64K by 16 bits.

It requires only one supply in the range of 2.7V to 3.6V in normal read mode opera-

tion. The by-16 organization makes this part ideal for portable and handheld 16 and

32 bit microprocessor based systems using either regulated or unregulated battery

power.

(continued)

Pin Configurations

Pin Name Function

A0 - A15 Addresses

O0 - O15 Outputs

CE Chip Enable

OE Output Enable

PGM

Program Strobe

NC No Connect

Note: Both GND pins must be

connected.

PLCC Top View

1 Megabit

(64K x 16)

Unregulated

Battery-Voltage™

High Speed

OTP

CMOS EPROM

AT27BV1024

TSOP Top View

Type 1

Note: PLCC Package Pins 1 and

23 are DON’T CONNECT.

0631A

3-33

1 page

AT27BV1024

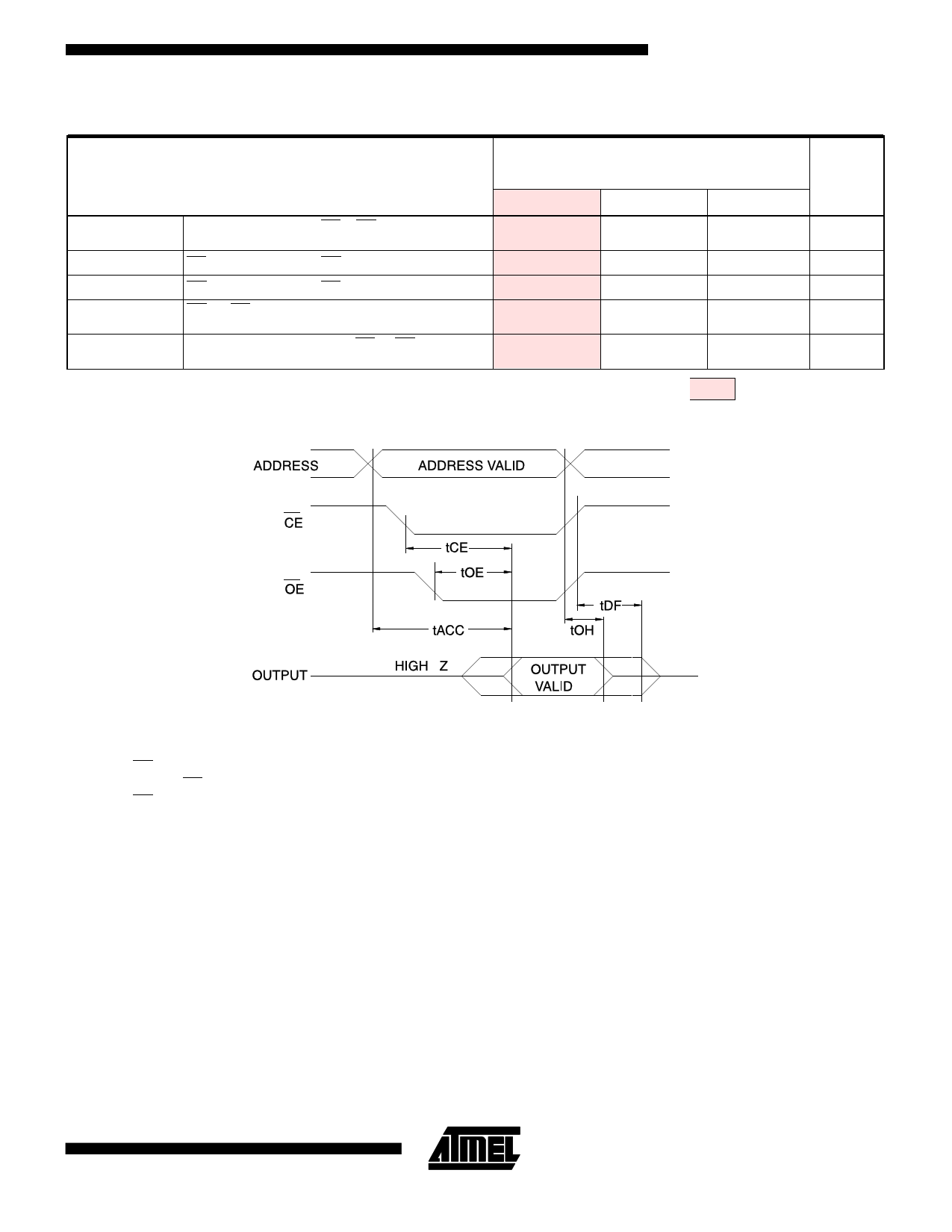

AC Characteristics for Read Operation (VCC = 2.7V to 3.6V and 4.5V to 5.5V)

AT27BV1024

-90 -12 -15

Symbol

Parameter

Condition

tACC (3)

tCE (2)

tOE (2, 3)

tDF (4, 5)

tOH

Address to

Output Delay

CE = OE

= VIL

CE to Output Delay OE = VIL

OE to Output Delay CE = VIL

OE or CE High to Output Float,

whichever occurred first

Output Hold from Address, CE or OE,

whichever occurred first

Notes: 2, 3, 4, 5. - see AC Waveforms for Read Operation.

Min Max Min Max Min Max

Units

90 120 150 ns

90 120 150 ns

30 35 50 ns

30 30 40 ns

000

ns

= Preliminary Information

AC Waveforms for Read Operation (1)

Notes: 1. Timing measurement references are 0.8V and 2.0V.

Input AC drive levels are 0.45V and 2.4V, unless oth-

erwise specified.

2. OE may be delayed up to tCE - tOE after the falling

edge of CE without impact on tCE.

3. OE may be delayed up to tACC - tOE after the address

is valid without impact on tACC.

4. This parameter is only sampled and is not 100% tested.

5. Output float is defined as the point when data is no longer

driven.

6. When reading a 27BV1024, a 0.1 µF capacitor is required

across VCC and ground to supress spurious voltage tran-

sients.

3-37

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet AT27BV1024-15JI.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT27BV1024-15JC | 1 Megabit 64K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | ATMEL Corporation |

| AT27BV1024-15JI | 1 Megabit 64K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |