|

|

PDF AT27BV4096-15JC Data sheet ( Hoja de datos )

| Número de pieza | AT27BV4096-15JC | |

| Descripción | 4 Megabit 256K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT27BV4096-15JC (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

AT27BV4096

Features

Fast Read Access Time - 120 ns

•• Dual Voltage Range Operation

Unregulated Battery Power Supply Range, 2.7V to 3.6V

or Standard 5V ± 10% Supply Range

Pin Compatible with JEDEC Standard AT27C4096

•• Low Power CMOS Operation

20 µA max. (less than 1 µA typical) Standby for VCC = 3.6V

29 mW max. Active at 5 MHz for VCC = 3.6V

• JEDEC Standard Surface Mount Packages

44-Lead PLCC

40-Lead TSOP (10 x 14mm)

• High Reliability CMOS Technology

2,000V ESD Protection

200 mA Latchup Immunity

• Rapid™ Programming algorithm - 100 µs/word (typical)

• CMOS and TTL Compatible Inputs and Outputs

JEDEC Standard for LVTTL and LVBO

Integrated Product Identification Code

•• Commercial and Industrial Temperature Ranges

Description

The AT27BV4096 is a high performance, low power, low voltage 4,194,304 bit one-

time programmable read only memory (OTP EPROM) organized as 256K by 16 bits.

It requires only one supply in the range of 2.7V to 3.6V in normal read mode opera-

tion. The by-16 organization makes this part ideal for portable and handheld 16 and

32 bit microprocessor based systems using either regulated or unregulated battery

power.

(continued)

4 Megabit

(256K x 16)

Unregulated

Battery-Voltage™

High Speed

OTP

CMOS EPROM

Pin Configurations

Pin Name Function

A0 - A17 Addresses

O0 - O15 Outputs

CE Chip Enable

OE Output Enable

NC No Connect

Note: Both GND pins must be

connected.

AT27BV4096

PLCC Top View

TSOP Top View

Type 1

Note: 1. PLCC package pins 1 and 23

are DON’T CONNECT.

0640A

3-63

1 page

AT27BV4096

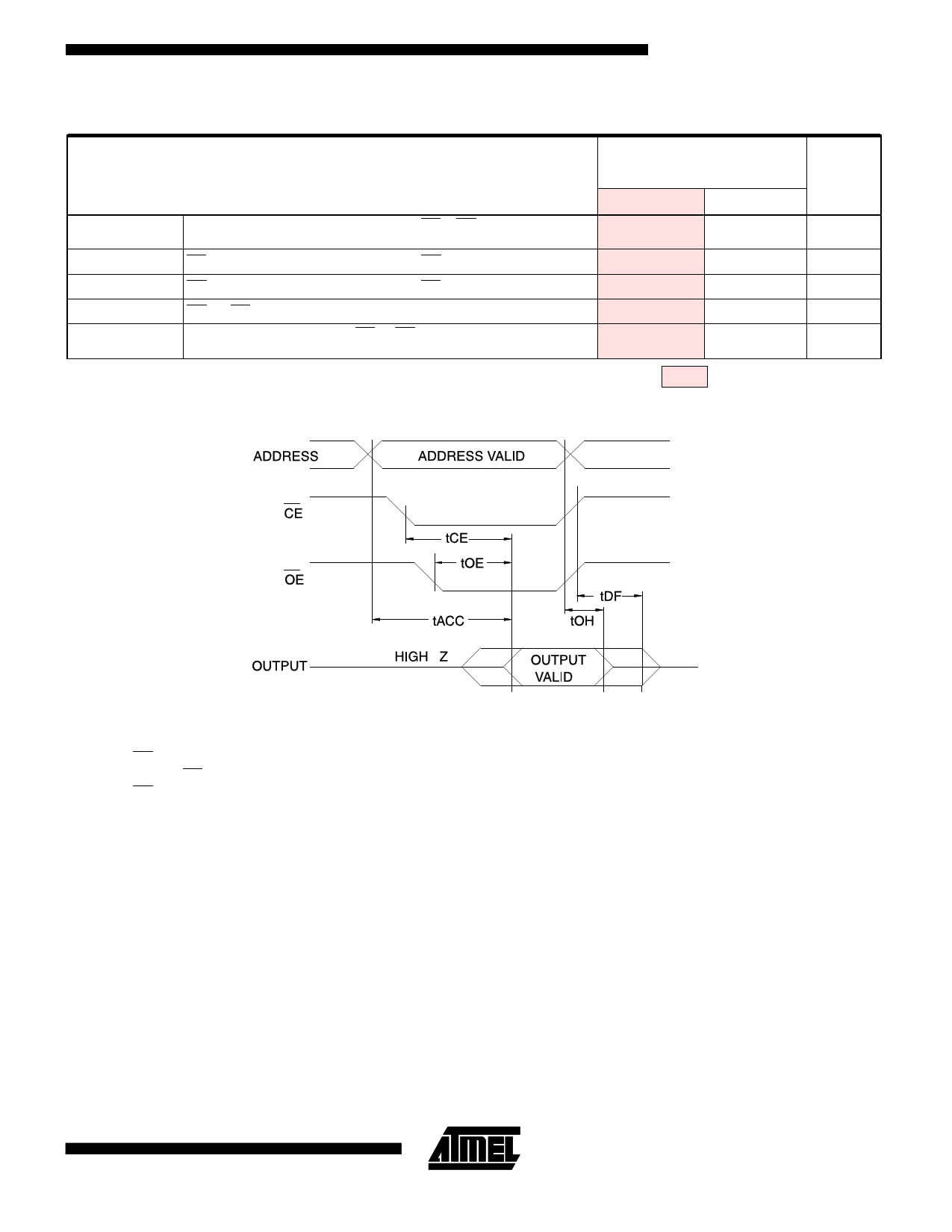

AC Characteristics for Read Operation (VCC = 2.7V to 3.6V and 4.5V to 5.5V)

Symbol

tACC (3)

tCE (2)

tOE (2, 3)

tDF (4, 5)

tOH

Parameter

Condition

Address to

Output Delay

CE = OE

= VIL

CE to Output Delay

OE = VIL

OE to Output Delay

CE = VIL

OE or CE High to Output Float, whichever occurred first

Output Hold from Address, CE or OE,

whichever occurred first

Notes: 2, 3, 4, 5. - see AC Waveforms for Read Operation.

AT27BV4096

-12 -15

Min Max Min Max

120 150

120 150

35 50

30 40

00

Units

ns

ns

ns

ns

ns

= Preliminary Information

AC Waveforms for Read Operation (1)

Notes: 1. Timing measurement references are 0.8V and 2.0V.

Input AC drive levels are 0.45V and 2.4V, unless oth-

erwise specified.

2. OE may be delayed up to tCE - tOE after the falling

edge of CE without impact on tCE.

3. OE may be delayed up to tACC - tOE after the address

is valid without impact on tACC.

4. This parameter is only sampled and is not 100% tested.

5. Output float is defined as the point when data is no longer

driven.

6. When reading a 27BV4096, a 0.1 µF capacitor is required

across VCC and ground to supress spurious voltage tran-

sients.

3-67

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet AT27BV4096-15JC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT27BV4096-15JC | 4 Megabit 256K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | ATMEL Corporation |

| AT27BV4096-15JI | 4 Megabit 256K x 16 Unregulated Battery-Voltage High Speed OTP CMOS EPROM | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |