|

|

PDF AZ100LVEL16VR Data sheet ( Hoja de datos )

| Número de pieza | AZ100LVEL16VR | |

| Descripción | ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AZ100LVEL16VR (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

ARIZONA MICROTEK, INC.

AZ100LVEL16VR

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable

FEATURES

• High Bandwidth for ≥1GHz

• Similar Operation as AZ100EL16VO

• Operating Range of 3.0V to 5.5V

• Minimizes External Components

• Selectable Enable Polarity and Threshold

(CMOS/TTL or PECL)

• Available in a 3x3mm MLP Package

DESCRIPTION

PACKAGE AVAILABILITY

PACKAGE

MLP 16

MLP 16 T&R

MLP 16 T&R

DIE

PART NO.

AZ100LVEL16VRL

AZ100LVEL16VRLR1

AZ100LVEL16VRLR2

AZ100LVEL16VRX

MARKING

AZM16R

AZM16R

AZM16R

N/A

The AZ100LVEL16VR is a specialized oscillator gain stage with high gain output buffer including an enable.

The QHG/Q¯ HG outputs have a voltage gain several times greater than the Q/Q¯ outputs.

The AZ100LVEL16VR provides a selectable enable that allows continuous oscillator operation. See truth table

below for enable function. If Enable pull-up is desired in the CMOS mode, an external ≤20kΩ resistor connecting

EN to VCC will override the on-chip pull-down resistor. The AZ100LVEL16VR also provides a VBB and 470Ω

internal bias resistors from D to VBB and D¯ to VBB. The VBB pin can support 1.5mA sink/source current. Bypassing

VBB to ground with a 0.01 µF capacitor is recommended.

Outputs Q/Q¯ each have a selectable on-chip pull-down current source. See truth table below for current source

functions. External resistors may also be used to increase pull-down current to a maximum total of 25mA.

Outputs QHG/Q¯ HG each have an optional on-chip pull-down current source of 10mA. When pad/pin VEEP is left

open (NC), the output current sources are disabled and the QHG /Q¯ HG operate as standard PECL/ECL. When VEEP is

connected to VEE , the current sources are activated. The QHG /Q¯ HG pull-down current can be decreased, by using a

resistor to connect from VEEP to VEE.

NOTE: Specifications in the ECL/PECL tables are valid when thermal equilibrium is established.

1630 S. STAPLEY DR., SUITE 125 • MESA, ARIZONA 85204 • USA • (480) 962-5881 • FAX (480) 890-2541

www.azmicrotek.com

1 page

AZ100LVEL16VR

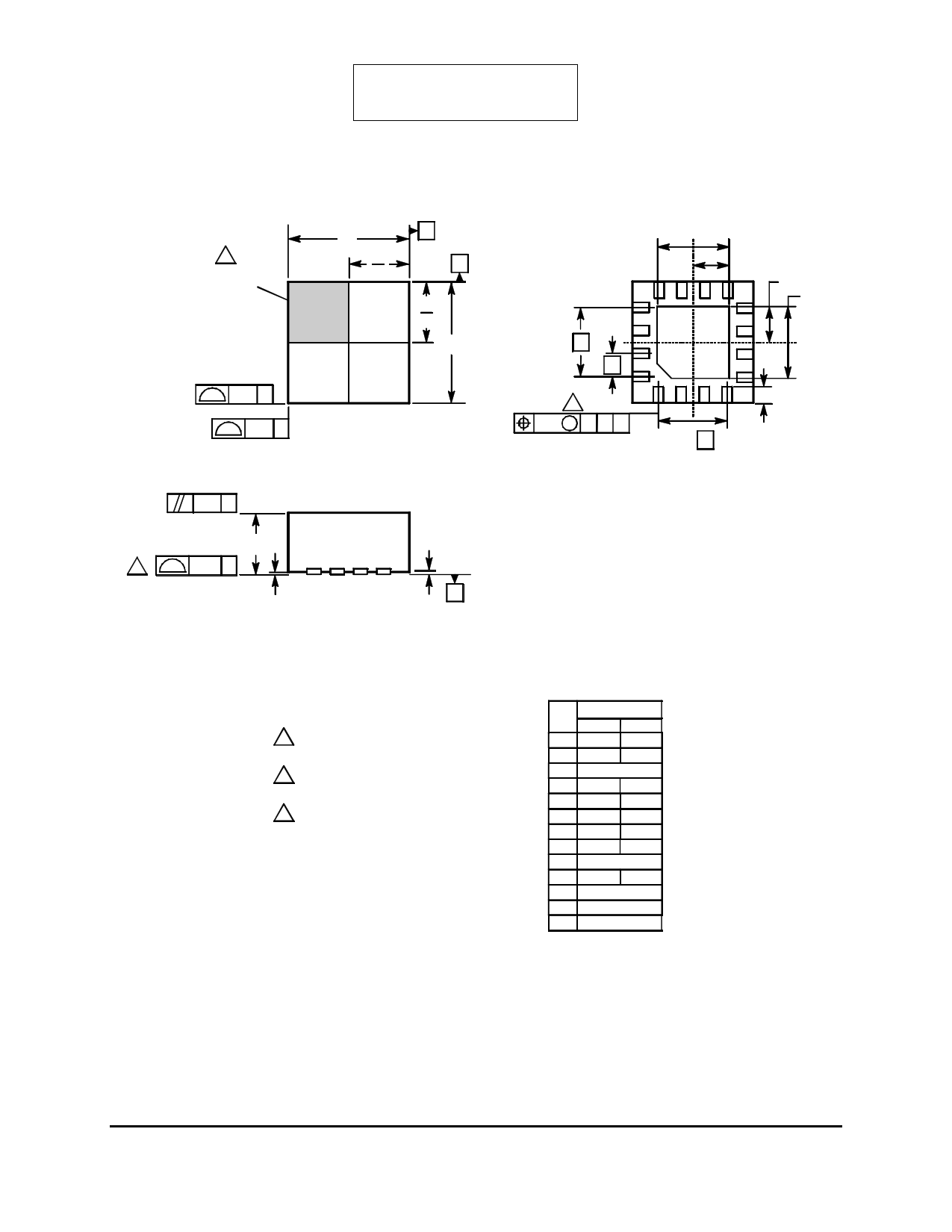

PACKAGE DIAGRAM

MLP 16

2.

INDEX AREA

(D/2 x E/2)

2x

2x

aaa C

aaa C

ccc C

A

4. 0.08 C

A1

D

D

2

TOP VIEW

SIDE VIEW

A

B

E

2

E

D2

D2/2

E2/2

E2

3x e 2

e

16 x b 3.

1

bbb M C A B

3x e

BOTTOM VIEW

L

A3

SEATING

C PLANE

NOTES:

1. DIMENSIONING AND TOLERANCING

CONFORM TO ASME T14-1994.

2. THE TERMINAL #1 AND PAD

NUMBERING CONVENTION SHALL

CONFORM TO JESD 95-1 SPP-012.

3. DIMENSION b APPLIES TO METALLIZED

PAD AND IS MEASURED BETWEEN 0.25

AND 0.30mm FROM THE PAD TIP.

4. COPLANARITY APPLIES TO THE

EXPOSED PAD AS WELL AS THE

TERMINALS

DIM

A

A1

A3

b

D

D2

E

E2

e

L

aaa

bbb

ccc

MILLIMETERS

MIN MAX

0.80 1.00

0.00 0.05

0.25 REF

0.18 0.30

2.90 3.10

0.25 1.95

2.90 3.10

0.25 1.95

0.50 BSC

0.30 0.50

0.25

0.10

0.10

July 2002 * REV - 1

www.azmicrotek.com

5

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet AZ100LVEL16VR.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AZ100LVEL16VR | ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable | ETC |

| AZ100LVEL16VRL | ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable | ETC |

| AZ100LVEL16VRLR1 | ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable | ETC |

| AZ100LVEL16VRLR2 | ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |