|

|

PDF 74ALVC16721MTD Data sheet ( Hoja de datos )

| Número de pieza | 74ALVC16721MTD | |

| Descripción | Low Voltage 20-Bit D-Type Flip-Flops with 3.6V Tolerant Inputs and Outputs | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74ALVC16721MTD (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

October 2001

Revised October 2001

74ALVC16721

Low Voltage 20-Bit D-Type Flip-Flops

with 3.6V Tolerant Inputs and Outputs

General Description

The ALVC16721 contains twenty non-inverting D-type

flip-flops with 3-STATE outputs and is intended for bus ori-

ented applications.

The 74ALVC16721 is designed for low voltage (1.65V to

3.6V) VCC applications with I/O compatibility up to 3.6V.

The 74ALVC16721 is fabricated with an advanced CMOS

technology to achieve high speed operation while maintain-

ing low CMOS power dissipation.

Features

s 1.8V–3.6V VCC supply operation

s 3.6V tolerant inputs and outputs

s tPD (CLK to On)

4.0 ns max for 3.0V to 3.6V VCC

4.9 ns max for 2.3V to 2.7V VCC

8.8 ns max for 1.65V to 1.95V VCC

s Power-off high impedance inputs and outputs

s Supports live insertion and withdrawal (Note 1)

s Uses patented noise/EMI reduction circuitry

s Latchup conforms to JEDEC JED78

s ESD performance:

Human body model > 2000V

Machine model > 200V

Note 1: To ensure the high-impedance state during power up or power

down, OE should be tied to VCC through a pull-up resistor; the minimum

value of the resistor is determined by the current-sourcing capability of the

driver.

Ordering Code:

Order Number Package Number

Package Description

74ALVC16721MTD

MTD56

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

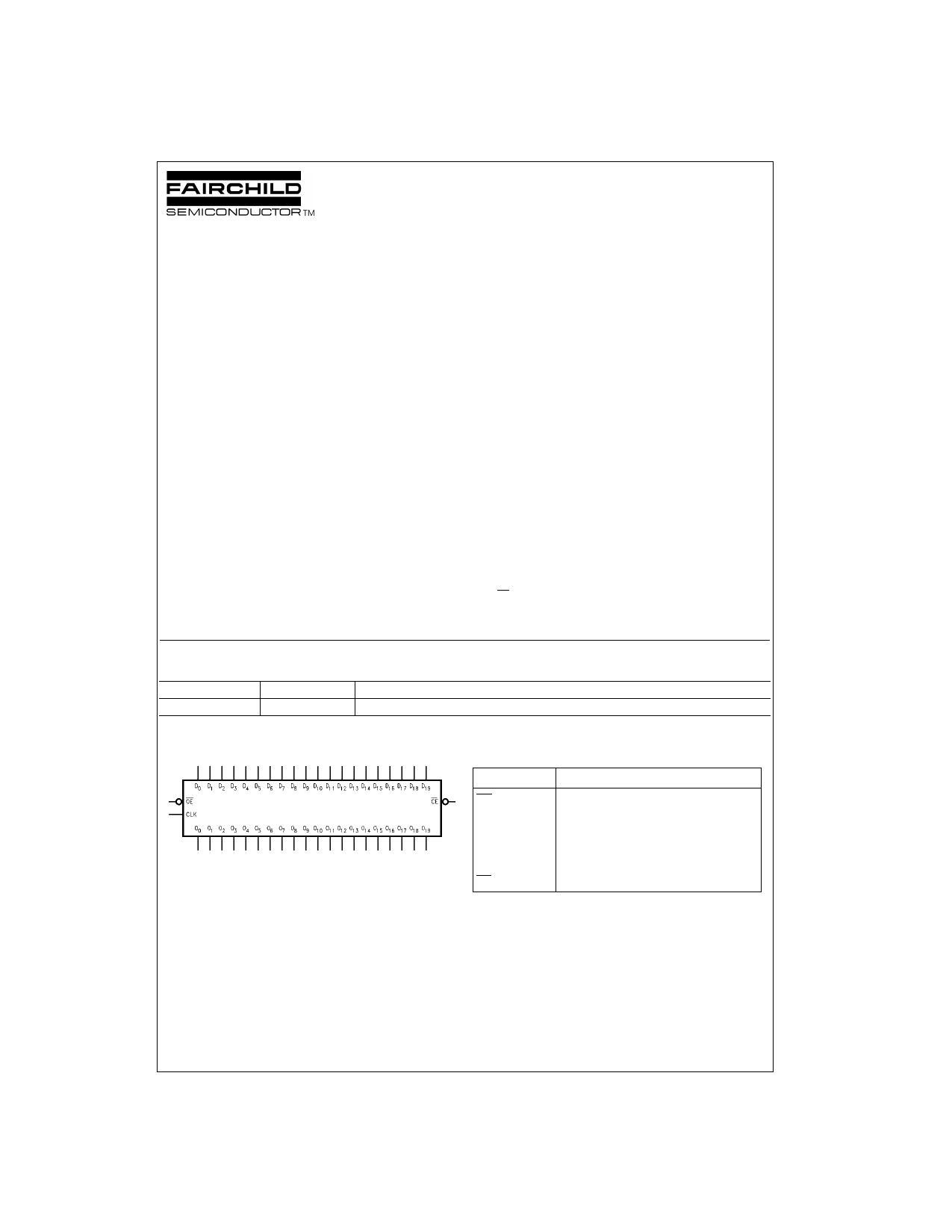

Logic Symbol

Pin Descriptions

Pin Names

OE

CLK

D0–D19

O0–O19

CE

Description

Output Enable Input (Active LOW)

Clock Input

Inputs

Outputs

Clock Enable Input (Active LOW)

© 2001 Fairchild Semiconductor Corporation DS500691

www.fairchildsemi.com

1 page

AC Loading and Waveforms

TABLE 1. Values for Figure 1

TEST

tPLH, tPHL

tPZL, tPLZ

tPZH, tPHZ

SWITCH

Open

VL

GND

FIGURE 1. AC Test Circuit

TABLE 2. Variable Matrix

(Input Characteristics: f = 1MHz; tr = tf = 2ns; Z0 = 50Ω)

Symbol

Vmi

Vmo

VX

VY

VL

3.3V ± 0.3V

1.5V

1.5V

VOL + 0.3V

VOH − 0.3V

6V

VCC

2.7V

2.5V ± 0.2V

1.5V

1.5V

VOL + 0.3V

VOH − 0.3V

6V

VCC/2

VCC/2

VOL + 0.15V

VOH − 0.15V

VCC*2

1.8V ± 0.15V

VCC/2

VCC/2

VOL + 0.15V

VOH − 0.15V

VCC*2

FIGURE 2. Waveform for Inverting

and Non-inverting Functions

FIGURE 3. 3-STATE Output Low Enable

and Disable Times for Low Voltage Logic

FIGURE 4. 3-STATE Output High Enable

and Disable Times for Low Voltage Logic

FIGURE 5. Propagation Delay, Pulse Width

and trec Waveforms

FIGURE 6. Setup Time, Hold Time and Recovery Time

for Low Voltage Logic

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet 74ALVC16721MTD.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74ALVC16721MTD | Low Voltage 20-Bit D-Type Flip-Flops with 3.6V Tolerant Inputs and Outputs | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |