|

|

PDF UPA103B-E1 Data sheet ( Hoja de datos )

| Número de pieza | UPA103B-E1 | |

| Descripción | HIGH FREQUENCY NPN TRANSISTOR ARRAY | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPA103B-E1 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

DATA SHEET

COMPOUND TRANSISTOR

µPA103

HIGH FREQUENCY NPN TRANSISTOR ARRAY

FEATURES

• FIVE MONOLITHIC 9 GHz fT TRANSISTORS:

Two of these use a common emitter pin and can be used as differential amplifiers

• OUTSTANDING hFE LINEARITY

• TWO PACKAGE OPTIONS:

µPA103B: Superior thermal dissipation due to studded ceramic package

µPA103G: Reduced circuit size due to 14-pin plastic SOP package for surface mounting

DESCRIPTION AND APPLICATIONS

The µPA103 is a user configurable Silicon bipolar transistor array consisting of a common emitter pair and three

individual bipolar transistors. It is available in a surface mount 14-pin plastic SOP package and a 14-pin ceramic package.

Typical applications include: differential amplifiers and oscillators, high speed comparators, advanced cellular phone

systems, electro-optic and other signal processing up to 1.5 gigabits/second.

ORDERING INFORMATION

PART NUMBER

PACKAGE

µPA103B-E1

14-pin ceramic package

µPA103G-E1

14-pin plastic SOP (225 mil)

ABSOLUTE MAXIMUM RATINGS (TA = +25 °C)

SYMBOLS

PARAMETERS

UNITS RATINGS

VCBO*

Collector to Base Voltage V

15

VCEO*

Collector to Emitter Voltage

V

6

VEBO*

Emitter to Base Voltage

V

2.5

IC* Collector Current

mA 40

PT Power Dissipation

µPA103B mW

µPA103G mW

650

350

TJ Junction Temperature

µPA103B °C

µPA103G °C

200

125

TSTG

Storage Temperature

µPA103B °C –55 to +200

µPA103G °C –55 to +125

* Absolute maximum ratings for each transistor.

Caution electro-static sensitive devices

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

Document No. P10708EJ2V0DS00 (2nd edition)

Date Published October 1999 N CP(K)

Printed in Japan

The mark shows major revised points.

©

1995, 1999

1 page

µPA103

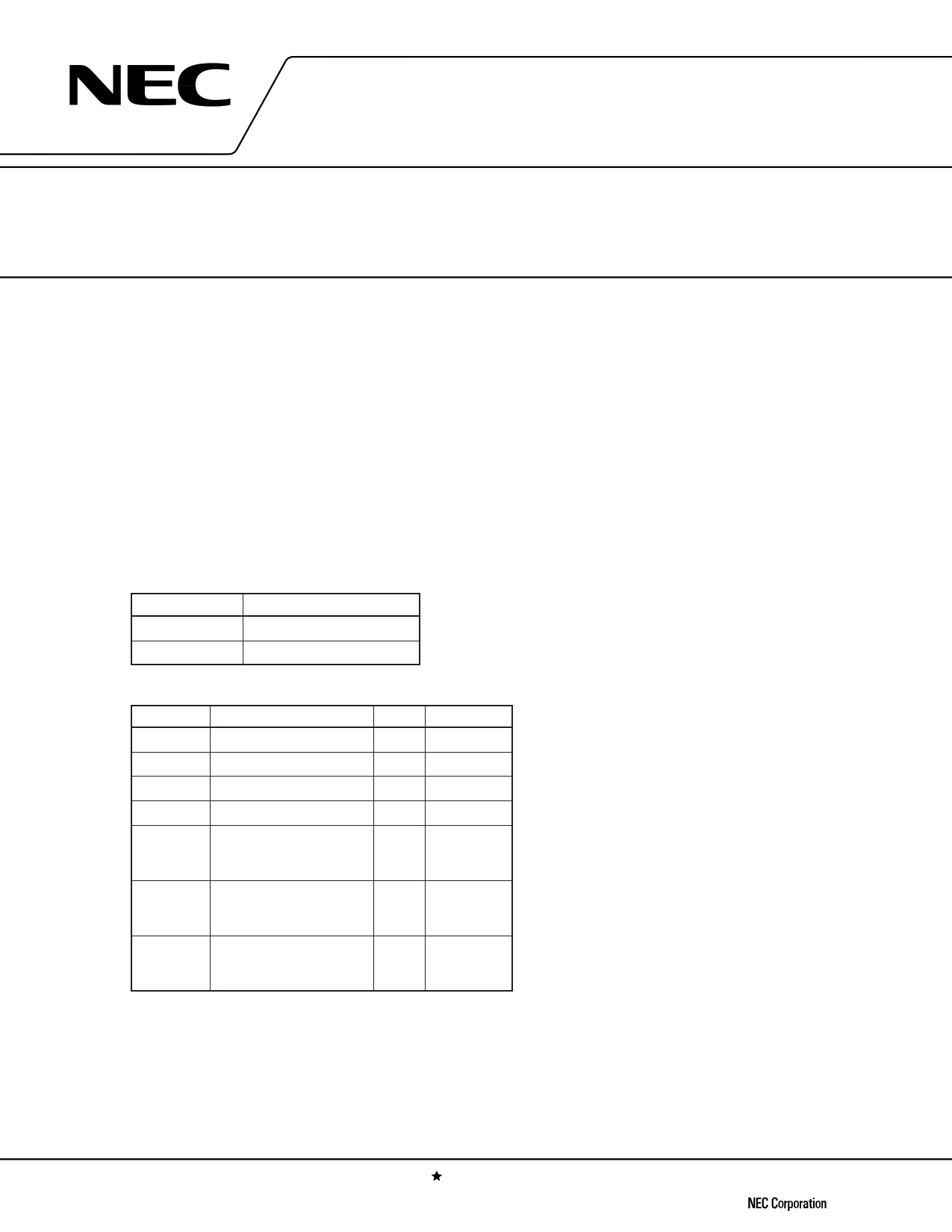

TYPICAL HIGH SPEED COMPARATOR

ANALOG INPUT Q1

R1 R2

R3 R4

R5 R6

REFERENCE

Q2

Q3 Q4

Q7 Q8

Q5

Q9 Q10

µµ

LATCH

LATCH

µ

Q11 Q12

µµ

Q6

OUTPUT

FEATURES:

1. High Sensitivity

µ 2. Low Positive Feedback time

3. Optimized latch recovery time

TYPICAL DIFFERENTIAL OSCILLATOR

VCC

VOUT

RFC

Q2

VCC

Q1

C1

R2

C2

4

BIAS

AC

SHORT

BENEFITS:

1. Ease of Integration

2. Very Low Distortion

3. Automatic Gain Control

4. Minimum Loading on Tank Circuit

5. Very Low 1/f Noise

TYPICAL COMMON MODE DIFFERENTIAL AMP

IN

VBB1 (5 V)

VBB2

100 Ω 100 pF

VCC (10 V)

OUT

1 KΩ

1 KΩ

1 KΩ

160 Ω 1000 pF

FEATURES:

1. High Gain

2. Stable

3. Auto Gain Control

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

Data Sheet P10708EJ2V0DS00

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet UPA103B-E1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPA103B-E1 | HIGH FREQUENCY NPN TRANSISTOR ARRAY | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |