|

|

PDF ID82C50A Data sheet ( Hoja de datos )

| Número de pieza | ID82C50A | |

| Descripción | CMOS Asynchronous Communications Element | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ID82C50A (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

82C50A

March 1997

CMOS Asynchronous

Communications Element

Features

• Single Chip UART/BRG

• DC to 625K Baud (DC to 10MHz Clock)

• Crystal or External Clock Input

• On Chip Baud Rate Generator 1 to 65535 Divisor

Generates 16X Clock

• Prioritized Interrupt Mode

• Fully TTL/CMOS Compatible

• Microprocessor Bus Oriented Interface

• 80C86/80C88 Compatible

• Scaled SAJI IV CMOS Process

• Low Power - 1mA/MHz Typical

• Modem Interface

• Line Break Generation and Detection

• Loopback and Echo Modes

• Doubled Buffered Transmitter and Receiver

• Single 5V Supply

Ordering Information

PACKAGE

PDIP

PLCC

CERDIP

TEMPERATURE

RANGE (oC)

0 to +70

-40 to +85

0 to +70

-40 to +85

0 to +70

-40 to +85

-55 to +125

625K BAUD

CP82C50A-5

IP82C50A-5

CS82C50A-5

IS82C50A-5

CD82C50A-5

ID82C50A-5

MD82C50A-5/B

PKG.

NO.

E40.6

E40.6

N44.65

N44.65

F40.6

F40.6

F40.6

Description

The 82C50A Asynchronous Communication Element (ACE)

is a high performance programmable Universal Asynchro-

nous Receiver/Transmitter (UART) and Baud Rate Genera-

tor (BRG) on a single chip. Using Intersil’s advanced Scaled

SAJI IV CMOS Process, the ACE will support data rates

from DC to 625K baud (0-10MHz clock).

The ACE’s receiver circuitry converts start, data, stop, and

parity bits into a parallel data word. The transmitter circuitry

converts a parallel data word into serial form and appends

the start, parity, and stop bits. The word length is program-

mable to 5, 6, 7, or 8 data bits. Stop bit selection provides a

choice of 1,1.5, or 2 stop bits.

The Baud Rate Generator divides the clock by a divisor

programmable from 1 to 216-1 to provide standard RS-232C

baud rates when using any one of three industry standard

baud rate crystals (1.8432MHz, 2.4576MHz, or 3.072MHz).

A programmable buffered clock output (BAUDOUT) provides

either a buffered oscillator or 16X (16 times the data rate)

baud rate clock for general purpose system use.

To meet the system requirements of a CPU interfacing to an

asynchronous channel, the modem control signals RTS,

CTS, DSR, DTR, RI, DCD are provided. Inputs and outputs

have been designed with full TTL/CMOS compatibility in

order to facilitate mixed TTL/NMOS/CMOS system design.

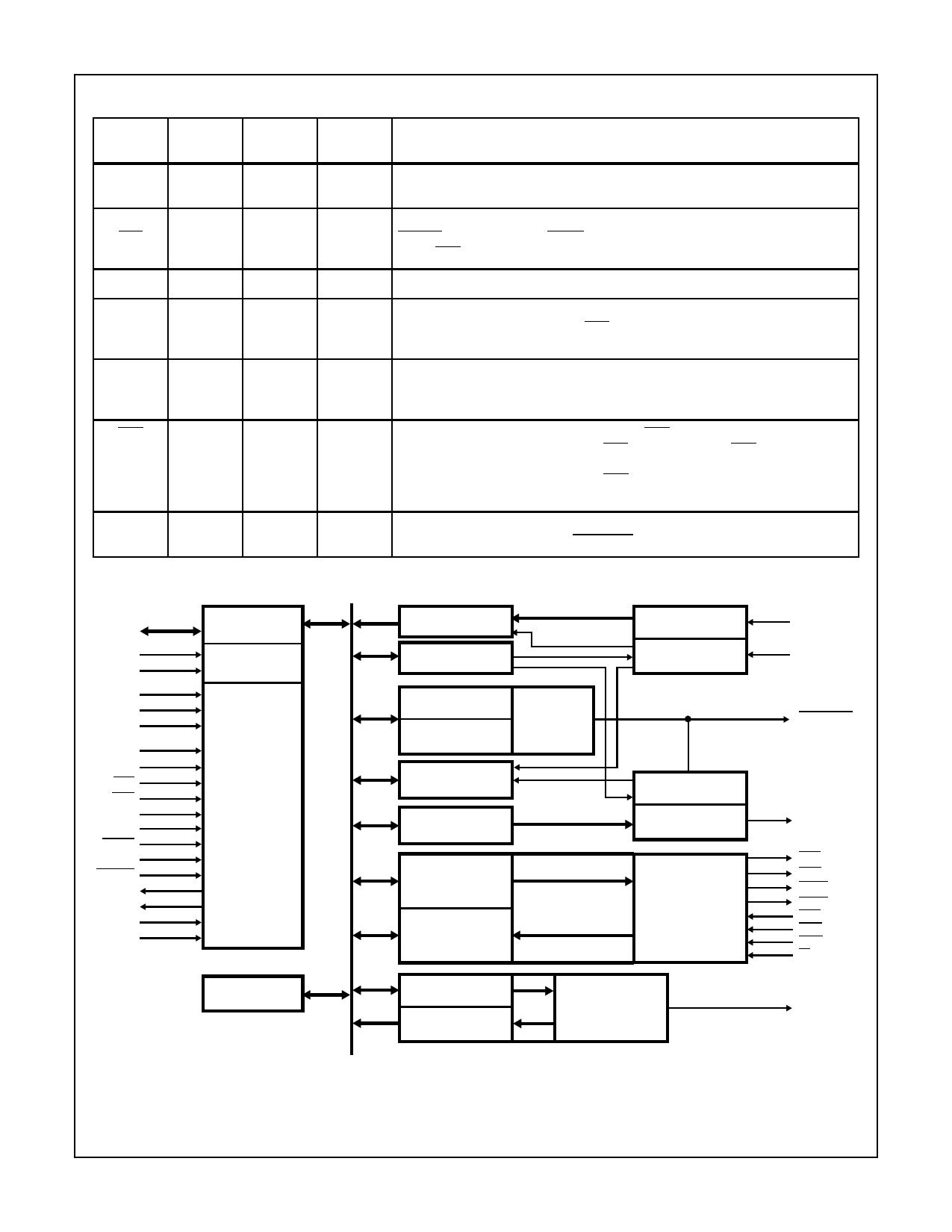

Functional Diagram

CSO

CS1

CS2

12

13

14

ADS 25

A0 28

A1 27

A2 26

MR 35

DISTR 22

DISTR 21

DOSTR 19

DOSTR 18

D0 1

D1 2

D2 3

D3 4

D4 5

D5 6

D6 7

D7 8

MICROPROCESSOR INTERFACE

24 CSOUT

23 DDIS

INTERRUPT 30 INTRPT

ENABLE,

ID, & CONTROL

UART

RECEIVER

LINE STATUS DIVISOR LATCH

AND CONTROL AND BAUD RATE

GENERATOR

TRANSMITTER

MODEM

MODEM CONTROL

MODEM STATUS

10 SIN

9 RCLK

15 BAUDOUT

16 XTAL1

17 XTAL2

11 SOUT

32 RTS

33 DTR

34 OUT1

31 OUT2

36 CTS

37 DSR

38 DCD

39 RI

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

1

File Number 2958.1

1 page

82C50A

Pin Description (Continued)

PIN

SYMBOL NUMBER

TYPE

VCC

40

CS0, CS1,

CS2

12,13,

14

I

I

NC

CSOUT

29

24

O

DDIS

23

O

ADS

25

I

RCLK

9

I

ACTIVE

LEVEL

H

H, H,

L

H

H

L

DESCRIPTION

VCC: +5V positive power supply pin. A 0.1µA decoupling capacitor from VCC (pin

40) to GND (pin 20) is recommended.

CHIP SELECT: The Chip Select inputs act as enable signals for the write (DOSTR,

DOSTR) and read (DlSTR, DlSTR) input signals. The Chip Select inputs are latched

by the ADS input.

Do Not Connect

CHIP SELECT OUT: When ACTIVE (high), this pin indicates that the chip has been

selected by active CS0, CS1, and CS2 inputs. No data transfer can be initiated until

CSOUT is a logic 1, ACTIVE (high).

DRIVER DISABLE: This output is INACTIVE (low) when the CPU is reading data

from the 82C50A. An ACTIVE (high) Dells output can be used to disable an external

transceiver when the CPU is reading data.

ADDRESS STROBE: When ACTIVE (low), ADS latches the Register Select (A0,

A1, A2) and Chip Select (CS0, CS1, CS2) inputs. An active ADS is required when

the Register Select pins are not stable for the duration of the read or write operation,

multiplexed mode. If not required, the ADS input should be tied low, non-multiplexed

mode.

This input is the 16X Baud Rate Clock for the receiver section of the 82C50A. This

input may be provided from the BAUDOUT output or an external clock.

Block Diagram

D7 - D0

+5V

GND

A0

A1

A2

CS0

CS1

CS2

ADS

MR

DISTR

DISTR

DOSTR

DOSTR

DDIS

CSOUT

XTAL1

XTAL2

(1 - 8)

(40)

(20)

(28)

(27)

(26)

(12)

(13)

(14)

(25)

(35)

(22)

(21)

(19)

(18)

(23)

(24)

(16)

(17)

DATA BUS

BUFFER

POWER

SUPPLY

SELECT

&

CONTROL

LOGIC

SCRATCH

REGISTER

RECEIVER BUFFER

REGISTER

LINE CONTROL

REGISTER

RECEIVER SHIFT

RECEIVER

RECEIVER TIMING

& CONTROL

(10)

(9)

SIN

RCLK

DIVISOR

LATCH (LS)

DIVISOR

LATCH (MS)

BAUD RATE

GENERATOR

(15)

BAUDOUT

LINE STATUS

REGISTER

TRANSMITTER

HOLDING REGISTER

MODEM CONTROL

REGISTER

MODEM STATUS

REGISTER

INTERRUPT ENABLE

REGISTER

INTERRUPT IO

REGISTER

TRANSMITTER

TIMING & CONTROL

TRANSMITTER (11)

SHIFT REGISTER

MODEM

CONTROL

LOGIC

(32)

(33)

(34)

(31)

(36)

(37)

(38)

(39)

SOUT

RTS

DTR

OUT1

OUT2

CTS

DSR

DCD

RI

INTERRUPT

CONTROL

LOGIC

(30) INTRPT

5

5 Page

82C50A

TRANSMITTER HOLDING REGISTER (THR)

The Transmitter Holding Register (THR) holds parallel data

from the data bus (D0-D7) until the Transmitter Shift Register

is empty and ready to accept a new character for transmis-

sion. The transmitter and receiver word length and number

of stop bits are the same. If the character is less than eight

bits, unused bits at the microprocessor data bus are ignored

by the transmitter.

Data Bit 0 (THR(0)) is the first serial data bit transmitted. The

THRE flag (LSR(5)) reflect the status of the THR. The TEMT

flag (LSR(6)) indicates if both the THR and TSR are empty.

THR Bits 0 thru 7

THR (0)

THR (1)

THR (2)

THR (3)

THR (4)

THR (5)

THR (6)

THR (7)

Data Bit 0

Data Bit 1

Data Bit 2

Data Bit 3

Data Bit 4

Data Bit 5

Data Bit 6

Data Bit 7

SCRATCHPAD REGISTER (SCR)

This 8-bit Read/Write register has no effect on the 82C50A.

It is intended as a scratchpad register to be used by the pro-

grammer to hold data temporarily.

SCR Bits 0 thru 7

SCR (0)

SCR (1)

SCR (2)

SCR (3)

SOR (4)

SCR (5)

SOR (6)

SCR (7)

Data Bit 0

Data Bit 1

Data Bit 2

Data Bit 3

Data Bit 4

Data Bit 5

Data Bit 6

Data Bit 7

Interrupt Structure

INTERRUPT IDENTIFICATION REGISTER (IIR)

The 82C50A has interrupt capability for interfacing to current

microprocessors. In order to minimize software overhead

during data character transfers, the 82C50A prioritizes

interrupts into four levels. The four levels of interrupt condi-

tions are as follows:

1. Receiver Line Status (Priority 1)

2. Received Data Ready (Priority 2)

3. Transmitter Holding Register Empty (Priority 3)

4. Modem Status (Priority 4).

Information indicating that a prioritized interrupt is pending

and the type of interrupt is stored in the Interrupt Identifica-

tion Register (IIR). When addressed during chip select time,

the lIR indicates the highest priority interrupt pending. No

other interrupts are acknowledged until the interrupt is ser-

viced by the CPU. The contents of the lIR are indicated in

Table 2 and are described below.

IIR(0): IIR(0) can be used in either a hardwired prioritized or

polled environment to indicate whether an interrupt is pend-

ing. When IIR(0) is low, an interrupt is pending, and the lIR

contents may be used as a pointer to the appropriate inter-

rupt service routine. When lIR(0) is high, no interrupt is

pending.

IlR(1) and IIR(2): llR(1) and IlR(2) are used to identify the

highest priority interrupt pending as indicated in Table 2.

lIR(3) - IIR(7): These five bits of the lIR are logic 0.

TABLE 2. INTERRUPT IDENTIFICATION REGISTER

BIT 2

X

1

1

0

INTERRUPT IDENTIFICATION

BIT 1

X

1

BIT 0

1

0

PRIORITY

LEVEL

First

0 0 Second

1 0 Third

000

NOTE: X = Not Defined, May Be 0 or 1

Fourth

INTERRUPT SET AND RESET FUNCTIONS

INTERRUPT

FLAG

INTERRUPT

SOURCE

INTERRUPT

RESET CONTROL

None

None

Receiver Line

Status

OE, PE, FE, or

BI

LSR Read

Received Data

Available

Receiver Data

Available

RBR Read

THRE

THRE

IIR Read if THRE is the

Interrupt Source or

THR Write

Modem Status

CTS, DSR, RI,

DCD

MSR Read

INTERRUPT ENABLE REGISTER (IER)

The Interrupt Enable Register (IER) is a Write register used

to independently enable the four 82C50A interrupts which

activate the interrupt (lNTRPT) output. All interrupts are dis-

abled by resetting IER(0) - IER(3) of the Interrupt Enable

Register. Interrupts are enabled by setting the appropriate

bits of the IER high. Disabling the interrupt system inhibits

the Interrupt Identification Register and the active (high)

INTRPT output. All other system functions operate in their

normal manner, including the setting of the Line Status and

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet ID82C50A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ID82C50A | CMOS Asynchronous Communications Element | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |