|

|

PDF AT89S4051 Data sheet ( Hoja de datos )

| Número de pieza | AT89S4051 | |

| Descripción | 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT89S4051 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

• Compatible with MCS®51 Products

• 2K/4K Bytes of In-System Programmable (ISP) Flash Program Memory

– Serial Interface for Program Downloading

– Endurance: 10,000 Write/Erase Cycles

• 2.7V to 5.5V Operating Range

• Fully Static Operation: 0 Hz to 24 MHz (x1 and x2 Modes)

• Two-level Program Memory Lock

• 256 x 8-bit Internal RAM

• 15 Programmable I/O Lines

• Two 16-bit Timer/Counters

• Six Interrupt Sources

• Programmable Serial UART Channel

• Direct LED Drive Outputs

• On-chip Analog Comparator with Selectable Interrupt

• 8-bit PWM (Pulse-width Modulation)

• Low Power Idle and Power-down Modes

• Brownout Reset

• Enhanced UART Serial Port with Framing Error Detection and Automatic

Address Recognition

• Internal Power-on Reset

• Interrupt Recovery from Power-down Mode

• Programmable and Fuseable x2 Clock Option

• Four-level Enhanced Interrupt Controller

• Power-off Flag

• Flexible Programming (Byte and Page Modes)

– Page Mode: 32 Bytes/Page

• User Serviceable Signature Page (32 Bytes)

8-bit

Microcontroller

with 2K/4K

Bytes Flash

AT89S2051

AT89S4051

1. Description

The AT89S2051/S4051 is a low-voltage, high-performance CMOS 8-bit microcon-

troller with 2K/4K bytes of In-System Programmable (ISP) Flash program memory.

The device is manufactured using Atmel’s high-density nonvolatile memory technol-

ogy and is compatible with the industry-standard MCS-51 instruction set. By

combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel

AT89S2051/S4051 is a powerful microcontroller which provides a highly-flexible and

cost-effective solution to many embedded control applications. Moreover, the

AT89S2051/S4051 is designed to be function compatible with the AT89C2051/C4051

devices, respectively.

The AT89S2051/S4051 provides the following standard features: 2K/4K bytes of

Flash, 256 bytes of RAM, 15 I/O lines, two 16-bit timer/counters, a six-vector, four-

level interrupt architecture, a full duplex enhanced serial port, a precision analog

comparator, on-chip and clock circuitry. Hardware support for PWM with 8-bit resolu-

tion and 8-bit prescaler is available by reconfiguring the two on-chip timer/counters. In

addition, the AT89S2051/S4051 is designed with static logic for operation down to

zero frequency and supports two software-selectable power saving modes. The Idle

Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt

system to continue functioning. The power-down mode saves the RAM contents

but freezes the disabling all other chip functions until the next external interrupt or

hardware reset.

3390E–MICRO–6/08

1 page

AT89S2051/S4051

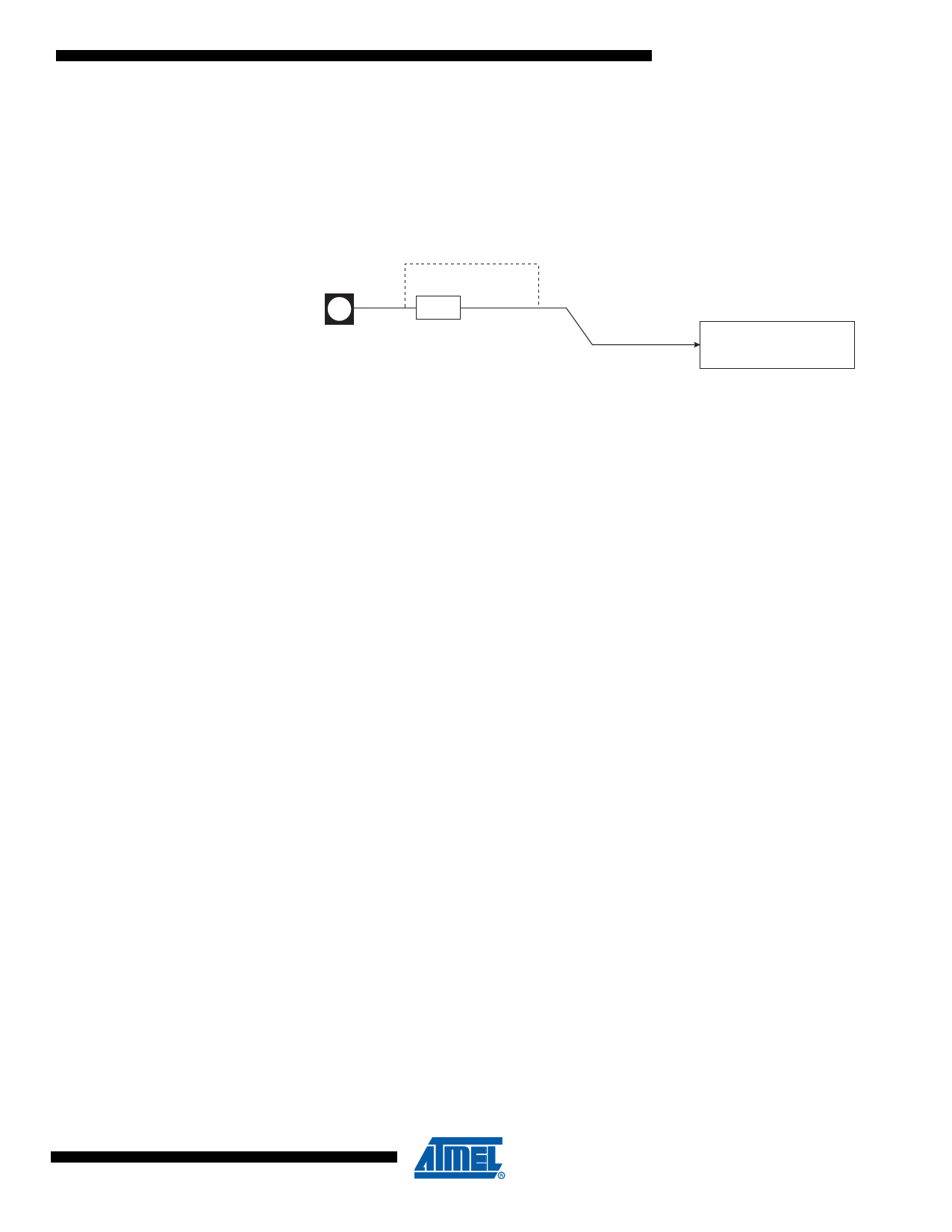

6. X2 Mode Description

The clock for the entire circuit and peripherals is normally divided by 2 before being used by the

CPU core and peripherals. This allows any cyclic ratio (duty cycle) to be accepted on XTAL1

input. In X2 mode this divider is bypassed. Figure 6-1 shows the clock generation block diagram.

Figure 6-1. Clock Generation Block Diagram

X2 Mode

XTAL1

FXTAL

÷ 2 (XTAL1)/2

FOSC

State Machine: 6 Clock Cycles

CPU Control

7. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in

Table 7-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be imple-

mented on the chip. Read accesses to these addresses will in general return random data, and

write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future

products to invoke new features. In that case, the reset or inactive values of the new bits will

always be 0.

3390E–MICRO–6/08

5

5 Page

AT89S2051/S4051

12.4

Reset Recovery from Power-down

Wakeup from Power-down through an external reset is similar to the interrupt with PWDEX = 0.

At the rising edge of RST, Power-down is exited, the is restarted, and an internal timer begins

counting. The internal clock will not be allowed to propagate to the CPU until after the timer has

counted for nominally 2 ms. The RST pin must be held high for longer than the timeout period to

ensure that the device is reset properly. The device will begin executing once RST is brought

low.

It should be noted that when idle is terminated by a hardware reset, the device normally

resumes program execution, from where it left off, up to two machine cycles before the internal

reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but

access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a

port pin when Idle is terminated by reset, the instruction following the one that invokes Idle

should not be one that writes to a port pin or to external memory.

P1.0 and P1.1 should be set to “0” if no external pull-ups are used, or set to “1” if external pull-

ups are used.

.

Table 12-1. PCON – Power Control Register

PCON = 87H

Reset Value = 000X 0000B

Not Bit Addressable

SMOD1

SMOD0

PWMEN

POF

GF1

GF0

PD

IDL

Bit 7 6 5 4 3 2 1 0

Symbol

SMOD1

SMOD0

PWMEN

POF

GF1, GF0

PD

IDL

Function

Double Baud Rate bit. Doubles the baud rate of the UART in modes 1, 2, or 3.

Frame Error Select. When SMOD0 = 0, SCON.7 is SM0. When SMOD0 = 1, SCON.7 is FE. Note that FE will be set after

a frame error regardless of the state of SMOD0.

Pulse Width Modulation Enable. When PWMEN = 1, Timer 0 and Timer 1 are configured as an 8-bit PWM counter with

8-bit auto-reload prescaler. The PWM outputs on T1 (P3.5).

Power Off Flag. POF is set to “1” during power up (i.e. cold reset). It can be set or reset under software control and is not

affected by RST or BOD (i.e. warm resets).

General-purpose Flags

Power Down bit. Setting this bit activates power down operation.

Idle Mode bit. Setting this bit activates idle mode operation

3390E–MICRO–6/08

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT89S4051.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT89S4051 | 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |