|

|

PDF AT49LD3200B Data sheet ( Hoja de datos )

| Número de pieza | AT49LD3200B | |

| Descripción | 32M High Speed Synchronous Flash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT49LD3200B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

.comFeatures

U• 3.0V to 3.6V Read/Write

t4• Burst Read Performance

e– <100 MHz (RAS Latency = 2, CAS Latency = 6), 10 ns Cycle Time

etSAC = 7 ns

h– <75 MHz (RAS Latency = 2, CAS Latency = 5), 13 ns Cycle Time

StSAC = 8 ns

ta– <50 MHz (RAS Latency = 1, CAS Latency = 4), 20 ns Cycle Time

atSAC = 9 ns

• MRS Cycle with Address Key Programs

.D– RAS Latency (1 and 2)

w 32-megabit– CAS Latency (2 ~ 8)

w– Burst Length: 4, 8

(1M x 32 or– Burst Type: Sequential and Interleaved

w• Word Selectable Organization

2M xm16)– 16 (Word Mode)/x 32 (Double Word Mode)

• Sector Erase Architecture

Higoh-speed– Eight 256K Word or 128K Double Word (4-Mbit) Sectors

.Sc• Independent Asynchronous Boot Block

ynchronous– 8K x 16 Bits with Hardware Lockout

• Fast Program Time

– 3-volt, 100 µs per Word/Double Word Typical

U Flash Memory– 12-volt, 30 µs per Word/Double Word Typical

t4• Fast Sector Erase Time

– 2.5 Seconds at 3 Volts

– 1.6 Seconds at 12 Volts

e AT49LD3200• Low-power Operation

– ICC Read = 75 mA Typical

e AT49LD3200B• Input and Output Pin Continuity Test Mode Optimizes Off-board Programming

• Package:

h SFlash– 86-pin TSOP Type II with Off-center Parting Line (OCPL) for Improved Reliability

• LVTTL-compatible Inputs and Outputs

taSDescription

The AT49LD3200 or AT49LD3200B SFlash™ is a synchronous, high-bandwidth Flash

amemory fabricated with Atmel’s high-performance CMOS process technology and is

organized either as 2,097,152 x 16 bits (word mode) or as 1,048,576 x 32 bits (double

.Dword mode), depending on the polarity of the WORD pin (see Pin Function Descrip-

tion Table). Synchronous design allows precise cycle control. I/O transactions are

possible on every clock cycle. All operations are synchronized to the rising edge of the

wsystem clock. The range of operating frequencies, programmable burst length and

programmable latencies allow the same device to be useful for a variety of high-band-

wwidth, high-performance memory system applications.

mThe AT49LD3200B will automatically activate the Asynchronous Boot Block after

w opower-up, whereas with the AT49LD3200, the Asynchronous Boot Block can be acti-

.cvated through Mode Register Set.

UThe synchronous DRAM interface allows designers to maximize system performance

t4while eliminating the need to shadow slow asynchronous Flash memory into high-

espeed RAM.

eThe 32-megabit SFlash device is designed to sit on the synchronous memory bus and

www.DataShoperate alongside SDRAM.

™

Rev. 1940B–11/01

1

1 page

AT49LD3200(B)

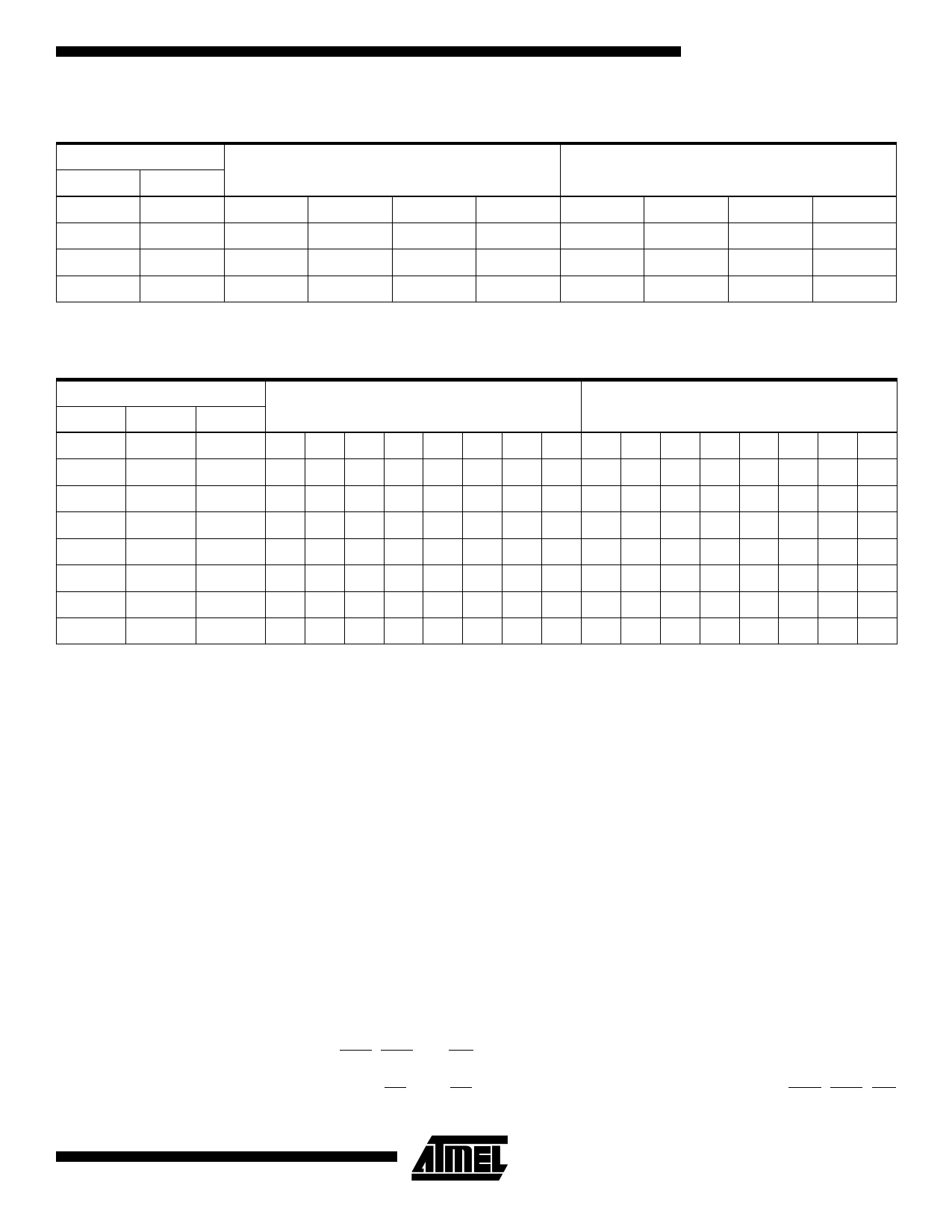

DC and AC Operating Range

Operating Temperature

(Case)

VCC, VCCQ Power Supply

Commercial

Industrial

AT49LD3200(B)-10

0°C - 70°C

-40°C - 85°C

3.0V to 3.6V

AT49LD3200(B)-13

0°C - 70°C

-40°C - 85°C

3.0V to 3.6V

AT49LD3200(B)-20

0°C - 70°C

-40°C - 85°C

3.0V to 3.6V

DC Characteristics

Symbol

Parameter

Condition

Min Max

ISB1 VCC Standby Current CMOS

ISB2 VCC Standby Current TTL

ISB3 VCC Active Standby Current

ICC VCC Active Current

IIL Input Leakage Current

CKE = 0, tCC = Min

CKE ≤=VIL (Max), tCC = Min

CS ≥ VIH (Min), tCC = Min

tCC = Min, All Outputs Open

0V ≤ VIN ≤ VDD + 0.3V

Pins not under test = 0V

20

20

50

150

-10 10

IOL

VIH

VIL

VOH

VOL

Notes:

Output Leakage Current (IOOUT

Disabled)

Input High Voltage, All Inputs

Input Low Voltage, All Inputs

(0V ≤ VOUT ≤ VDD Max)

All Outputs in High-Z

Note(1)

Note(2)

-10 10

2.0 VDD + 0.3

-0.3 0.8

Output High Voltage Level (Logic 1)

IOH = -2 mA

2.4

Output Low Voltage Level (Logic 0)

IOL = 2 mA

0.4

1. VIH (max) = 4.6V for pulse width <10 ns acceptable, pulse width measured at 50% of pulse amplitude.

2. VIL (min) = -1.5V for pulse width <10 ns acceptable, pulse width measured at 50% of pulse amplitude.

Units

mA

mA

mA

mA

µA

µA

V

V

V

V

AC Operating Test Conditions

TA = 0 to 70°C, VCC = 3.3V ± 0.3V, unless otherwise noted.

Parameter(1)

Value

Timing Reference Levels of Input/Output Signals

1.4V

Input Signal Levels

VIH/VIL = 2.4V/0.4V

Transition Time (Rise & Fall) of Input Signals

tr/tf = 1 ns/1 ns

Output Load

LVTTL

Note: 1. If CLK transition time is longer than 1 ns, timing parameters should be compensated. Add [(tr + tf)/2-1] ns for transition time

longer than 1 ns. Transition time is measured between VIL (max) and VIH (min).

1940B–11/01

5

5 Page

AT49LD3200(B)

Burst Sequence (Burst Length = 4)

Initial Address

A1 A0

Sequential

Interleave

0001230123

0112301032

1023012301

1130123210

Burst Sequence (Burst Length = 8)

Initial Address

A2 A1 A0

000

001

010

011

100

101

110

111

Sequential

Interleave

0123456701234567

1234567010325476

2345670123016745

3456701232107654

4567012345670123

5670123454761032

6701234567452301

7012345676543210

Device Operations

Clock (CLK)

Clock Enable (CKE)

NOP and Device

Deselect

A square wave signal (CLK) must be applied externally at cycle time tCC. All operations

are synchronized to the rising edge of the clock. The clock transitions must be mono-

tonic between VIL and VIH. During operation with CKE high, all inputs are assumed to be

in valid state (low or high) for the duration of setup and hold time around the positive

edge of the clock for proper functionality and ICC specifications.

The clock enable (CKE) gates the clock into the AT49LD3200(B) and is asserted high

during all cycles, except for power-down, standby and clock suspend mode. If CKE goes

low synchronously with clock (setup and hold time same as other inputs), the internal

clock is suspended from the next clock cycle and the state of output and burst address

is frozen for as long as the CKE remains low. All other inputs are ignored from the next

clock cycle after CKE goes low. The AT49LD3200(B) remains in the power-down mode,

ignoring other inputs for as long as CKE remains low. The power-down exit is synchro-

nous as the internal clock is suspended. When CKE goes high at least “1 CLK + tSS”

before the rising edge of the clock, then the AT49LD3200 becomes active from the

same clock edge accepting all the input commands.

When RAS, CAS and MR are high, the AT49LD3200(B) performs no operation (NOP).

NOP does not initiate any new operation. Device deselect is also a NOP and is entered

by asserting CS high. CS high disables the command decoder so that RAS, CAS, MR

1940B–11/01

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT49LD3200B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT49LD3200 | 32M High Speed Synchronous Flash Memory | ATMEL Corporation |

| AT49LD3200B | 32M High Speed Synchronous Flash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |