|

|

PDF AT91SAM7A3 Data sheet ( Hoja de datos )

| Número de pieza | AT91SAM7A3 | |

| Descripción | AT91 ARM Thumb-based Microcontrollers | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT91SAM7A3 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• Incorporates the ARM7TDMI ® ARM® Thumb® Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

– Leader in MIPS/Watt

• Embedded ICE In-circuit Emulation, Debug Communication Channel Support

• 256 Kbytes of Internal High-speed Flash, Organized in 1024 Pages of 256 Bytes

– Single Cycle Access at Up to 30 MHz in Worst Case Conditions

– Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed

– Page Programming Time: 4 ms, Including Page Auto-erase, Full Erase Time: 10 ms

– 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities

• 32K Bytes of Internal High-speed SRAM, Single-cycle Access at Maximum Speed

• Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

– Memory Protection Unit

• Reset Controller (RSTC)

– Based on Three Power-on Reset Cells

– Provides External Reset Signal Shaping and Reset Sources Status

• Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and One PLL

• Power Management Controller (PMC)

– Power Optimization Capabilities, including Slow Clock Mode (Down to 500 Hz), Idle

Mode, Standby Mode and Backup Mode

– Four Programmable External Clock Signals

• Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Four External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt

Protected

• Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention

• Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter

• Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signal to the System

– Counter May Be Stopped While the Processor is in Debug Mode or in Idle State

• Real-time Timer (RTT)

– 32-bit Free-running Counter with Alarm

– Runs Off the Internal RC Oscillator

• Two Parallel Input/Output Controllers (PIO)

– Sixty-two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up resistor and Synchronous Output

• Shutdown Controller (SHDWC)

– Programmable Shutdown Pin and Wake-up Circuitry

• Four 32-bit Battery Backup Registers for a Total of 16 Bytes

• One 8-channel 20-bit PWM Controller (PMWC)

• One USB 2.0 Full Speed (12 Mbits per Second) Device Port

– On-chip Transceiver, 2-Kbyte Configurable Integrated FIFOs

• Nineteen Peripheral Data Controller (PDC) Channels

• Two CAN 2.0B Active Controllers, Supporting 11-bit Standard and 29-bit Extended

Identifiers

– 16 Fully Programmable Message Object Mailboxes, 16-bit Time Stamp Counter

• Two 8-channel 10-bit Analog-to-Digital Converter

AT91 ARM®

Thumb®-based

Microcontrollers

AT91SAM7A3

Summary

Preliminary

6042AS–ATARM–23-Dec-04

Note: This is a summary document. A complete document

is available on our Web site at www.atmel.com.

1 page

AT91SAM7A3 Preliminary

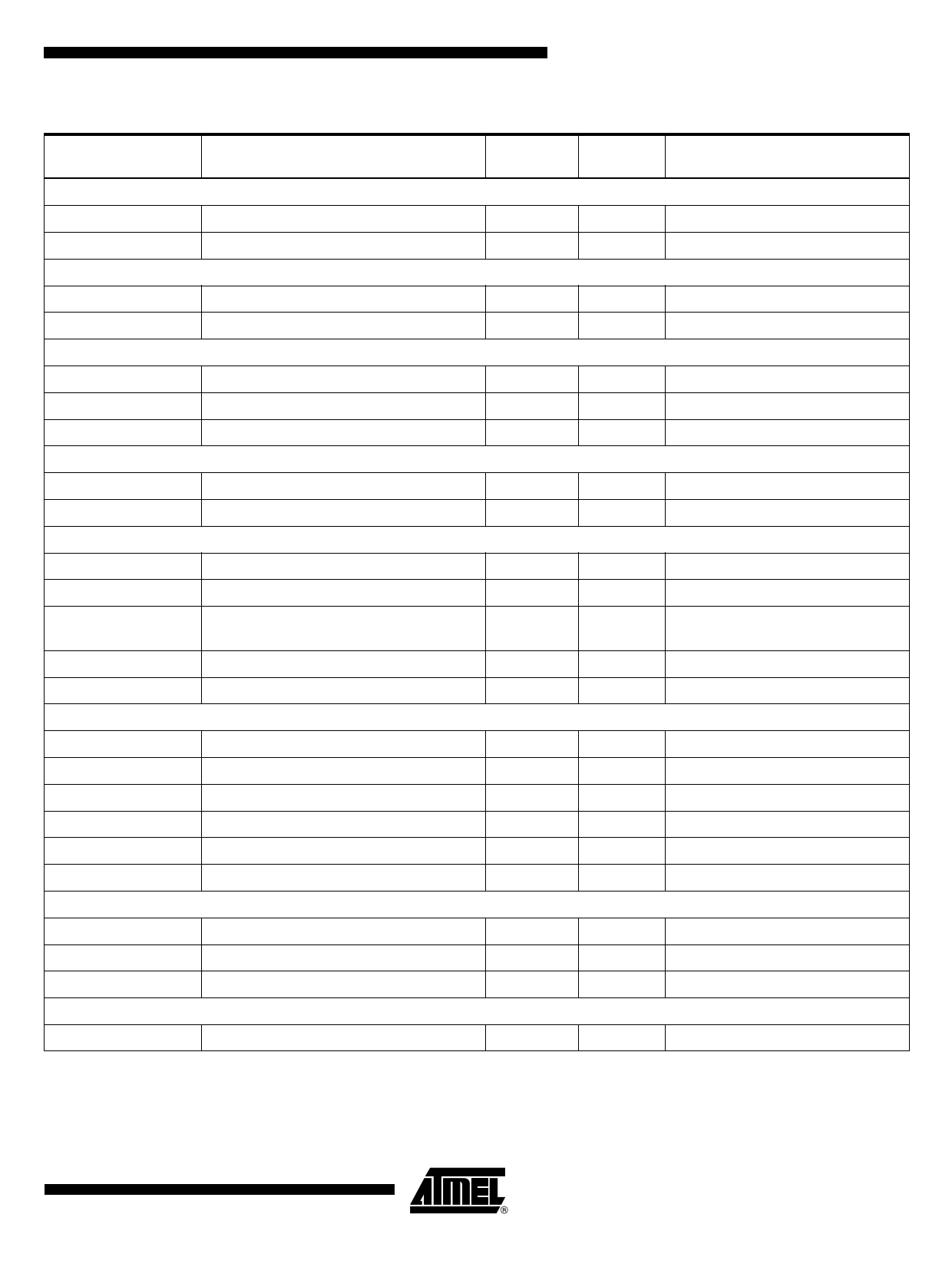

Table 1. Signal Description (Continued)

Signal Name

Function

Type

Active

Level

AIC

IRQ0 - IRQ3

External Interrupt Inputs

Input

FIQ Fast Interrupt Input

Input

PIO

PA0 - PA31

Parallel IO Controller A

I/O

PB0 - PB29

Parallel IO Controller B

I/O

Multimedia Card Interface

MCCK

Multimedia Card Clock

Output

MCCDA

Multimedia Card A Command

I/O

MCDA0 - MCDA3

Multimedia Card A Data

I/O

USB Device Port

DDM

USB Device Port Data -

Analog

DDP

USB Device Port Data +

Analog

USART

SCK0 - SCK1 - SCK2 Serial Clock

I/O

TXD0 - TXD1 - TXD2 Transmit Data

I/O

RXD0 - RXD1 -

RXD2

Receive Data

Input

RTS0 - RTS1 - RTS2 Request To Send

Output

CTS0 - CTS1 - CTS2 Clear To Send

Input

Synchronous Serial Controller

TD0 - TD1

Transmit Data

Output

RD0 - RD1

Receive Data

Input

TK0 - TK1

Transmit Clock

I/O

RK0 - RK1

Receive Clock

I/O

TF0 - TF1

Transmit Frame Sync

I/O

RF0 - RF1

Receive Frame Sync

I/O

Timer/Counter

TCLK0 - TCLK8

External Clock Input

Input

TIOA0 - TIOA8

I/O Line A

I/O

TIOB0 - TIOB8

I/O Line B

I/O

PWM Controller

PWM0 - PWM7

PWM Channels

Output

Comments

Pulled-up input at reset

Pulled-up input at reset

6042AS–ATARM–23-Dec-04

Preliminary

5

5 Page

AT91SAM7A3 Preliminary

Processor and Architecture

ARM7TDMI Processor

• RISC Processor Based on ARMv4T Von Neumann Architecture

– Runs at up to 60 MHz, providing 0.9 MIPS/MHz

• Two instruction sets

– ARM high-performance 32-bit Instruction Set

– Thumb high code density 16-bit Instruction Set

• Three-stage pipeline architecture

– Instruction Fetch (F)

– Instruction Decode (D)

– Execute (E)

Debug and Test Features •

•

•

Integrated embedded in-circuit emulator

– Two watchpoint units

– Test access port accessible through a JTAG protocol

– Debug communication channel

Debug Unit

– Two-pin UART

– Debug communication channel interrupt handling

– Chip ID Register

IEEE1149.1 JTAG Boundary-scan on all digital pins

Memory Controller

• Bus Arbiter

– Handles requests from the ARM7TDMI and the Peripheral Data Controller

• Address Decoder Provides Selection Signals for

– Three internal 1Mbyte memory areas

– One 256 Mbyte embedded peripheral area

• Abort Status Registers

– Source, Type and all parameters of the access leading to an abort are saved

– Facilitates debug by detection of bad pointers

• Misalignment Detector

– Alignment checking of all data accesses

– Abort generation in case of misalignment

• Remap Command

– Remaps the Internal SRAM in place of the embedded non-volatile memory

– Allows handling of dynamic exception vectors

• 16-area Memory Protection Unit

– Individually programmable size between 1K Bytes and 1M Bytes

– Individually programmable protection against write and/or user access

– Peripheral protection against write and/or user access

• Embedded Flash Controller

– Embedded Flash interface, up to three programmable wait states

6042AS–ATARM–23-Dec-04

Preliminary

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT91SAM7A3.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT91SAM7A1 | ARM7TDMI BASED MICROCONTROLLER | ATMEL Corporation |

| AT91SAM7A1-AI | ARM7TDMI BASED MICROCONTROLLER | ATMEL Corporation |

| AT91SAM7A2 | ARM Thumb - based Microcontrollers | ATMEL Corporation |

| AT91SAM7A2-AI | ARM Thumb - based Microcontrollers | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |