|

|

PDF C9835 Data sheet ( Hoja de datos )

| Número de pieza | C9835 | |

| Descripción | Low-EMI Clock Generator | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de C9835 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

C9835

Low-EMI Clock Generator for Intel®

Mobile 133-MHz/3 SO-DIMM Chipset Systems

Features

• Meets Intel’s Mobile 133.3MHz Chipset

• Three CPU Clocks (66.6/100/133.3 MHz, 2.5V)

• Six SDRAM Clocks, 1-DCLK (100/133.3 MHz, 3.3V)

• Seven PCI Clocks (33MHz, 3.3V), one free running

• Two IOAPIC clocks, synchronous to CPU clock (33.3

MHz, 2.5V)

• One REF Clock

• Two 48-MHz fixed non-SSCG clocks (USB and DOT)

• Three 3V66 clocks (66.6 MHz, 3.3V) ICH, HUBLINK, and

AGP memory

• One selectable frequency for VCH video channel clock

(48-MHz non-SSCG, 66.6-MHz CPU-SSCG, 3.3V)

• Power management using power-down, CPU stop, and

PCI stop pins

• Three function select pins (include test-mode select)

• Cypress Spread Spectrum for best electromagnetic

interference (EMI) reduction

• SMBUS support with readback

• 56-pin SSOP and TSSOP packages

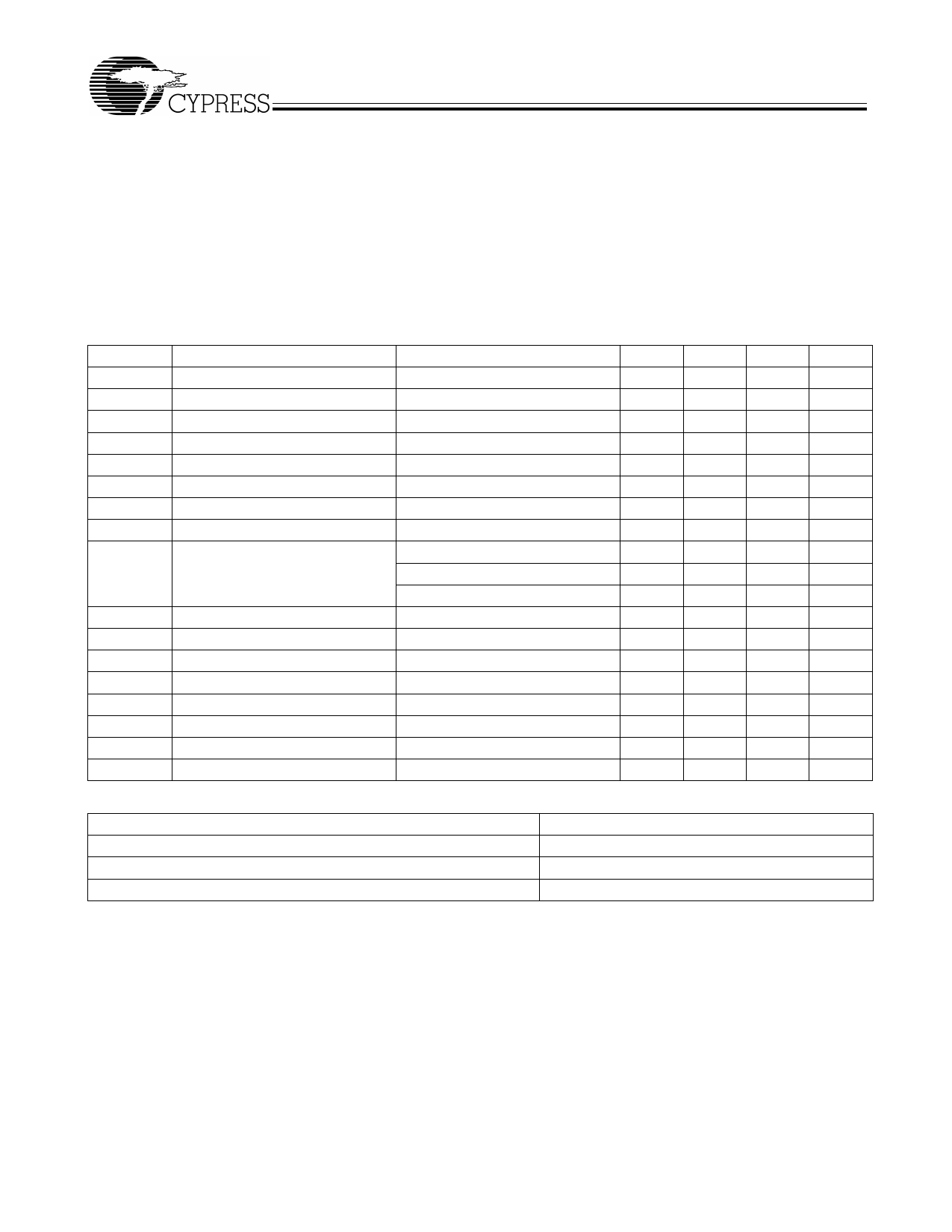

Table 1. Function Table[1]

TEST#

0

0

1

1

1

1

SEL1

X

X

0

0

1

1

SEL0

0

1

0

1

0

1

CPU(0:2)

Hi-Z

TCLK/2

66.6

100.0

133.3

133.3

SDRAM(0:5)

DCLK

Hi-Z

TCLK/2

100.0[2]

100.0[2]

133.3

100.0[2]

3V66(0:2)

Hi-Z

TCLK/3

66.6

66.6

66.6

66.6

PCIF(1:6) 48M(0:1) REF IOAPIC(0:10)

Hi-Z

TCLK/6

33.3

33.3

33.3

33.3

Hi-Z

TCLK/2

48

48

48

48

Hi-Z

TCLK

14.318

14.318

14.318

14.318

Hi-Z

TCLK/6

33.3

33.3

33.3

33.3

Note:

1. These are the frequencies that are selectable after power up using the SEL1 and SEL0 hardware pins. Other frequencies may be chosen using the devices

SMBUS interface. See the expanded frequency for a complete listing of all of the availible frequencies.

2. Will be set to 133MHz, when SMBUS Byte3, Bit 0 is set to logic 1.

Block Diagram

Pin Configuration

X IN

XO U T

TEST#

S E L 0 ,1

P C I_ S T P #

C P U _S T P #

PD#

S C LK

SDATA

36pF

36pF

IO A P IC

CPU

R in

tris ta te

s0

PD#

SDRAM

3V66

i2 c -c lk

i2 c -d a ta

PLL1

R in

48

PD#

i2 c -c lk

i2 c -d a ta

PLL2

PCI

VDD

1

VDD

1

VDDI

REF

VC H _C LK

2 IO A P IC (0 ,1 )

VDDC

3 C P U (0:2 )

VDDS

6

VDD

3

VDDP

S D R A M (0 :5 )

3 V 6 6 (0 :2 )

P C I_ F

VDDP

6 P C I(1 :6 )

VDD

2 4 8 M (0 ,1 )

VDDS

1 D C LK

REF

VDD

XIN

XOUT

VSS

VSS

3V66_0

3V66_1

3 V 66 _2(A G P )

VDD

P C I_S T P #

PCI_F

PCI1

VSS

PCI2

PCI3

VDDP

PCI4

PCI5

PCI6

VSS

AVDD

AVSS

VSS

4 8M 0(U S B )

48 M 1(D O T )

VDD

SEL0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56 VSS

55 IOAPIC0

54 IOAPIC1

53 VDDI

52 CPU0

51 VDDC

50 CPU1

49 CPU2

48 VSS

47 VSS

C

46

45

SDRAM0

SDRAM1

9 44 VDDS

8 43 SDRAM2

3

42

41

SDRAM3

VSS

5 40 SDRAM4

39 SDRAM5

38 DCLK

37 VDDS

36 VCH_CLK

35 VDD

34 CPU_STP#

33 TEST#

32 PD#

31 SCLK

30 SDATA

29 SEL1

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-07303 Rev. **

Revised April 5, 2002

1 page

CPU(1,2)

PCI_F

CPU_STP#

CPU0

PCI_STP#

(High)

PWR_DWN#

(High)

Tsu

Tsu

PCI_F

PCI_STP#

Figure 2. CPU_STP Timing Diagram

Tsu Tsu

PCI(1:6)

CPU_STP#

PD#

(High)

(High)

Figure 3. PCI_STP# Timing Diagram[[10,11,12,13,14]

Note:

10. All the internal timing is referenced to the CPU clock

11. PCI_STP# signal is an input signal that must be made synchronous to PCI_F output.

12. All other clocks continue to run undisturbed.

13. PD# is understood to in a high state.

14. Diagrams shown with respect to 133 MHz. Similar operation when CPU is 100 MHz

C9835

Document #: 38-07303 Rev. **

Page 5 of 18

5 Page

C9835

Maximum Ratings

Maximum Input Voltage Relative to VSS: ............ VSS – 0.3V

Maximum Input Voltage Relative to VDD:............. VDD + 0.3V

Storage Temperature: ................................–65°C to + 150°C

Operating Temperature: .................................... 0°C to +85°C

Maximum ESD Protection.............................................. 2 KV

Maximum Power Supply: ................................................5.5V

This device contains circuitry that protects the inputs against

damage due to high static voltages or electric field; however,

precautions should be taken to avoid application of any

voltage higher than the maximum rated voltages to this circuit.

For proper operation, VIN and VOUT should be constrained to

the range:

VSS < (VIN or VOUT) < VDD.

Unused inputs must always be tied to an appropriate logic

voltage level (either VSS or VDD).

DC Parameters VDD = VDDS = 3.3V ± 5%, VDDC = VDDI = 2.5V ± 5%, TA = 0°C to +70°C[20]

Parameter

Description

Conditions

Min. Typ. Max. Units

VIL1

Input Low Voltage

Note 21

1.0 V

VIH1

Input High Voltage

2.0 V

VIL2

Input Low Voltage

Note 22

1.0 V

VIH2

IIL1

IIH1

Ioz

Input High Voltage

Input Low Current (@VIL = VSS)

Input High Current (@VIH =VDD)

Three-state leakage Current

For internal pull-up resistors[23]

2.2

V

–20 µA

20 µA

10 µA

Idd3.3V

Dynamic Supply Current

295 mA

Idd2.5V

CPU @ 66 MHz

60 mA

Dynamic Supply Current

CPU @ 100 MHz

75 mA

CPU @ 133 MHz

90 mA

Ipd3.3V

Power Down Supply Current

PD# = “0”

1 mA

Ipd2.5V

Power Down Supply Current

PD# = “0”

1 mA

Cin Input pin capacitance

5 pF

Cout

Output pin capacitance

6 pF

Lpin

Cxtal

Pin inductance

Crystal pin capacitance

7 nH

Measured from Pin to Ground[24]

34

36

38

pF

VBIAS

Txs

Crystal DC Bias Voltage

Crystal Startup time

0.3VDD VDD/2 0.7VDD

From stable 3.3V power supply.

40

V

µs

Table 7. Maximum Output Load

Clock Name

CPU(0:2), IOAPIC(0:1), REF, 48M0 (USB), VCH_CLK

PCI(0:6), SDRAM(0:5), DCLK, 3V66(0:2)

48M1 (DOT)

Max Load (in pF)

20

30

15

Notes:

20. All outputs loaded per Table 7.

21. Applicable to input signals : SEL(0:1), PD# (pull-up).

22. Applicable to SDATA and SCLK.

23. Internal pull-up and pull-down resistors affect this current.

24. See Applications data that is presented later in this datasheet on crystal interfacing.

Document #: 38-07303 Rev. **

Page 11 of 18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet C9835.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| C9835 | Low-EMI Clock Generator | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |