|

|

PDF AT90C8534 Data sheet ( Hoja de datos )

| Número de pieza | AT90C8534 | |

| Descripción | Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT90C8534 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• Utilizes the AVR® RISC Architecture

• AVR – High-performance and Low-power RISC Architecture

– 118 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General-purpose Working Registers

– Up to 1.5 MIPS Throughput at 1.5 MHz

• Data and Nonvolatile Program Memory

– 8K Bytes Flash Program Memory

Endurance: 1,000 Write/Erase Cycles

– 256 Bytes Internal SRAM

– 512 Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– Programming Lock for Flash Program and EEPROM Data Security

• Peripheral Features

– One 8-bit Timer/Counter with Separate Prescaler

– One 16-bit Timer/Counter with Separate Prescaler

• Special Microcontroller Features

– Low-power Idle and Power-down Modes

– External and Internal Interrupt Sources

– 6-channel, 10-bit ADC

• Specifications

– Low-power, High-speed CMOS Process Technology

– Fully Static Operation

• Power Consumption at 1.5 MHz, 3.6V, 25°C

– Active: 1.2 mA

– Idle Mode: 0.2 mA

– Power-down Mode: <10 µA

• I/O and Packages

– Seven General Output Lines

– Two External Interrupt Lines

– 48-lead LQFP/VQFP Package

• Operating Voltage

– 3.3 - 6.0V

• Speed Grade

– 0 - 1.5 MHz

8-bit

Microcontroller

with 8K Bytes

Programmable

Flash

AT90C8534

Preliminary

Description

The AT90C8534 is a low-power CMOS 8-bit microcontroller based on the AVR RISC

architecture. By executing powerful instructions in a single clock cycle, the

Pin Configuration

(continued)

ADIN0

NC

NC

NC

NC

NC

NC

NC

NC

NC

AGND

NC

1

2

3

4

5

6

7

8

9

10

11

12

36 NC

35 INT0

34 INT1

33 PA6

32 NC

31 GND

30 NC

29 NC

28 NC

27 NC

26 NC

25 NC

Rev. 1229B–11/00

1

1 page

AT90C8534

The I/O memory space contains 64 addresses for CPU peripheral functions such as Control Registers, Timer/Counters,

A/D converters and other I/O functions. The I/O memory can be accessed directly or as the Data Space locations

following those of the register file, $20 - $5F.

The AVR uses a Harvard architecture concept – with separate memories and buses for program and data. The program

memory is executed with a single-level pipelining. While one instruction is being executed, the next instruction is

pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program

memory is programmable Flash memory.

With the relative jump and call instructions, the whole 4K word (8K bytes) address space is directly accessed. Most AVR

instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is effec-

tively allocated in the general data SRAM and, consequently, the stack size is only limited by the total SRAM size and the

usage of the SRAM. All user programs must initialize the stack pointer (SP) in the reset routine (before subroutines or

interrupts are executed). The 9-bit stack pointer is read/write accessible in the I/O space.

The 256 bytes data SRAM can be easily accessed through the five different addressing modes supported in the AVR

architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

Figure 4. The AT90C8534 AVR RISC Architecture

AVR AT90C8534 Architecture

Data Bus 8-bit

4K X 16

Program

Memory

Instruction

Register

Instruction

Decoder

Control Lines

Program

Counter

32 x 8

General

Purpose

Registrers

ALU

256 x 8

Data

SRAM

512 x 8

EEPROM

Interrupt

Unit

Status

and Control

8-bit

Timer/Counter

16-bit

Timer/Counter

Analog to Digital

Converter

7

Output Lines

5

5 Page

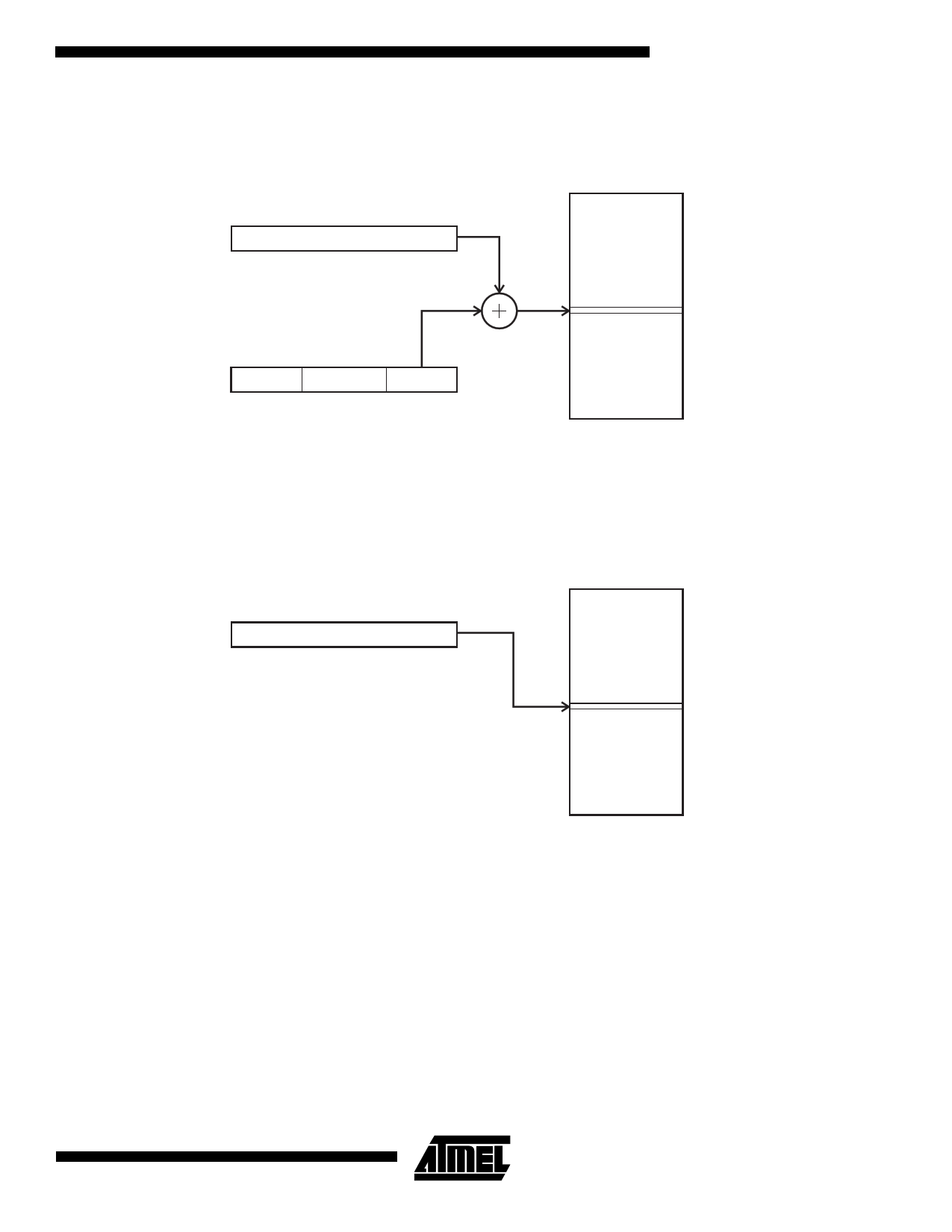

Data Indirect with Displacement

Figure 13. Data Indirect with Displacement

15

Y OR Z - REGISTER

0

AT90C8534

Data Space

$0000

15

OP

10

n

65 0

a

$015F

Operand address is the result of the Y- or Z-register contents added to the address contained in six bits of the instruction

word.

Data Indirect

Figure 14. Data Indirect Addressing

15 0

X, Y OR Z - REGISTER

Data Space

$0000

Operand address is the contents of the X-, Y- or the Z-register.

$015F

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT90C8534.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT90C8534 | Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |