|

|

PDF STE10A Data sheet ( Hoja de datos )

| Número de pieza | STE10A | |

| Descripción | PCI 10/100 Ethernet controller | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de STE10A (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

STE10/100A

PCI 10/100 Ethernet controller with integrated PHY (3.3V)

Features

■ IEEE802.3u 100BASE-TX and IEEE802.3

10BASE-T compliant

■ Support for IEEE802.3x flow control

■ IEEE802.3u auto-negotiation support for

10BASE-T and 100BASE-TX

■ PCI bus interface rev. 2.2 compliant

■ ACPI and PCI power management standard

compliant

■ Support for PC99 wake on LAN

■ Provides 32-bit PCI bus master data transfer at

PCI clocks of 20-33 MHz

■ Provides writable EEPROM/Boot rom interface

■ Provides independent transmission and

receiving FIFOs, each 2k bytes long

■ Supports big endian or little endian byte

ordering

■ ACPI and PCI compliant power management

functions offer significant power-savings

performance

■ Provides general purpose timers

■ 128-pin QFP package

PQFP128 (14mm x 20mm x 2.7mm)

Description

The STE10/100A is a high performing PCI fast

ethernet controller with integrated physical layer

interface for 10BASE-T and 100BASE-TX

applications.

It was designed with advanced CMOS technology

to provide glueless 32-bit bus master interface for

PCI bus, boot ROM interface, CSMA/CD protocol

for fast ethernet, as well as the physical media

interface for 100BASE-TX of IEEE802.3u and

10BASE-T of IEEE802.3. The auto-negotiation

function is also supported for speed and duplex

detection.

The STE10/100A provides both half-duplex and

full-duplex operation, as well as support for full-

duplex flow control. It provides long FIFO buffers

for transmission and receiving, and early interrupt

mechanism to enhance performance. The

STE10/100A also supports ACPI and PCI

compliant power management function

February 2007

Rev 8

1/82

www.st.com

82

1 page

STE10/100A

Overview

1.2 Detailed features

FIFO

● Provides independent transmission and receiving FIFOs, each 2k bytes long

● Pre-fetches up to two transmit packets to minimize inter frame gap (IFG) to 0.96us

● Retransmits collided packet without reload from host memory within 64 bytes.

● Automatically retransmits FIFO under-run packet with maximum drain threshold until

3rd time retry failure threshold of next packet.

PCI interface

● Provides 32-bit PCI bus master data transfer

● Supports PCI clock with frequency from 0Hz to 33MHz

● Supports network operation with PCI system clock from 20MHz to 33MHz

● Provides performance meter and PCI bus master latency timer for tuning the threshold

to enhance the performance

● Provides burst transmit packet interrupt and transmit/receive early interrupt to reduce

host CPU utilization

● As bus master, supports memory-read, memory-read-line, memory-read-multiple,

memory-write, memory-write-and-invalidate command

● Supports big or little endian byte ordering

EEPROM/Boot ROM interface

● Provides writable flash ROM and EPROM as boot ROM, up to 128Kbit

● Provides PCI to access boot ROM by byte, word, or double word

● Re-writes flash boot ROM through I/O port by programming register

● Provides serial interface for read/write 93C46 EEPROM

● Automatically loads device ID, vendor ID, subsystem ID, subsystem vendor ID,

maximum-latency, and minimum-grand from the 64 byte contents of 93C46 after PCI

reset de-asserted

MAC/physical

● Integrates the complete set of physical layer 100BASE-TX and 10BASE-T functions

● Provides full-duplex operation in both 100Mbps and 10Mbps modes

● Provides auto-negotiation (NWAY) function of full/half duplex operation for both 10 and

100 Mbps

● Provides MLT-3 transceiver with DC restoration for base-line wander compensation

● Provides transmit wave-shaper, receive filters, and adaptive equalizer

● Provides MAC and transceiver (TXCVR) loop-back modes for diagnostic

● Built-in stream cipher scrambler/ de-scrambler and 4B/5B encoder/decoder

● Supports external transmit and receive transformer with 1:1 turn ratio

5/82

5 Page

STE10/100A

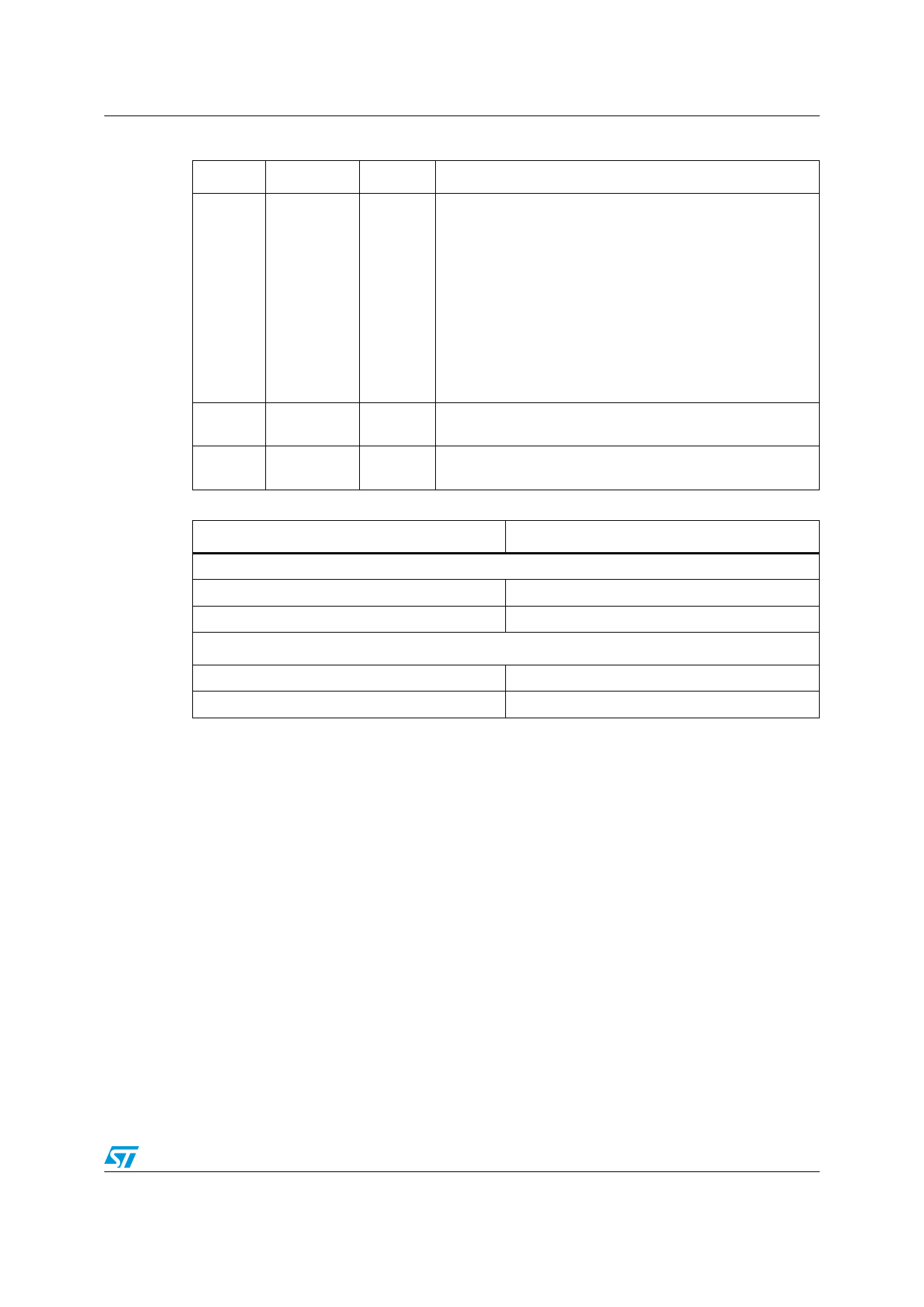

Pin description

Table 1.

Pin no.

91

89

88

Pin description (continued)

Name

Type

Description

LED M1-

Fd/Col

or

LED M2-

10 link

This pin can be programmed as mode 1 or mode 2:

For mode 1:

LED display for full duplex or collision status. This pin will be

driven on continually when a full duplex configuration is

detected. This pin will be driven at a 20 Hz blinking frequency

O when a collision status is detected in the half duplex

configuration.

For mode 2:

LED display for 10Ms/s link status. This pin will be driven on

continually when 10Mb/s network operating speed is

detected.

Vaux-detect

Vcc-detect

I

When this pin is asserted, it indicates an auxiliary power

source is supported from the system.

I

When this pin is asserted, it indicates a PCI power source is

supported.

Pin no.

Digital power pins

5,11,19,31,36,39,45,51,55,75,93,112,115,125

8,14,27,38,40,48,60,85,111,122,128

Analog power pins

94,96,102,106,110

95,99,100,103,108

Vss

Vdd

AVss

AVdd

Name

11/82

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet STE10A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| STE1000-60T4MI | Wet Tantalum Capacitors | Vishay |

| STE10000-10T4MI | Wet Tantalum Capacitors | Vishay |

| STE100A | PCI 10/100 Ethernet controller | ST Microelectronics |

| STE100N20 | N-CHANNEL ENHANCEMENT MODE Power MOS Transistor | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |