|

|

PDF W39F010 Data sheet ( Hoja de datos )

| Número de pieza | W39F010 | |

| Descripción | 128K X 8 CMOS FLASH MEMORY | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W39F010 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

W39F010

www.DataSheet4U.com

128K × 8 CMOS FLASH MEMORY

Table of Contents-

1. GENERAL DESCRIPTION ......................................................................................................... 3

2. FEATURES ................................................................................................................................. 3

3. PIN CONFIGURATIONS ............................................................................................................ 4

4. BLOCK DIAGRAM ...................................................................................................................... 5

5. PIN DESCRIPTION..................................................................................................................... 6

6. FUNCTIONAL DESCRIPTION ................................................................................................... 7

6.1 Device Bus Operation..................................................................................................... 7

6.1.1

Read Mode ...............................................................................................................7

6.1.2

Write Mode ...............................................................................................................7

6.1.3

Standby Mode ..........................................................................................................7

6.1.4

Output Disable Mode ................................................................................................7

6.2 Data Protection ............................................................................................................... 7

6.3 Boot Block Operation...................................................................................................... 8

6.3.1

Low VDD Inhibit ........................................................................................................8

6.3.2

Write Pulse "Glitch" Protection .................................................................................8

6.3.3

Logical Inhibit............................................................................................................8

6.3.4

Power-up Write Inhibit ..............................................................................................8

6.4 Command Definitions ..................................................................................................... 8

6.4.1

Read Command .......................................................................................................9

6.4.2

Auto-select Command ..............................................................................................9

6.4.3

Byte Program Command ..........................................................................................9

6.4.4

Chip Erase Command ............................................................................................10

6.4.5

Page Erase Command ...........................................................................................10

6.5 Write Operation Status ................................................................................................. 10

6.5.1

DQ7: Data Polling...................................................................................................10

6.5.2

DQ6: Toggle Bit ......................................................................................................11

7. TABLE OF OPERATING MODES ............................................................................................ 12

7.1 Device Bus Operations ................................................................................................. 12

7.2 Command Definitions ................................................................................................... 12

7.3 Embedded Programming Algorithm ............................................................................. 14

7.4 Embedded Erase Algorithm.......................................................................................... 15

7.5 Embedded #Data Polling Algorithm.............................................................................. 16

7.6 Boot Block Lockout Enable Flow Chart ........................................................................ 17

7.7 Software Product Identification and Boot Block Lockout Detection Flow Chart........... 18

Publication Release Date: December 26, 2005

- 1 - Revision A4

1 page

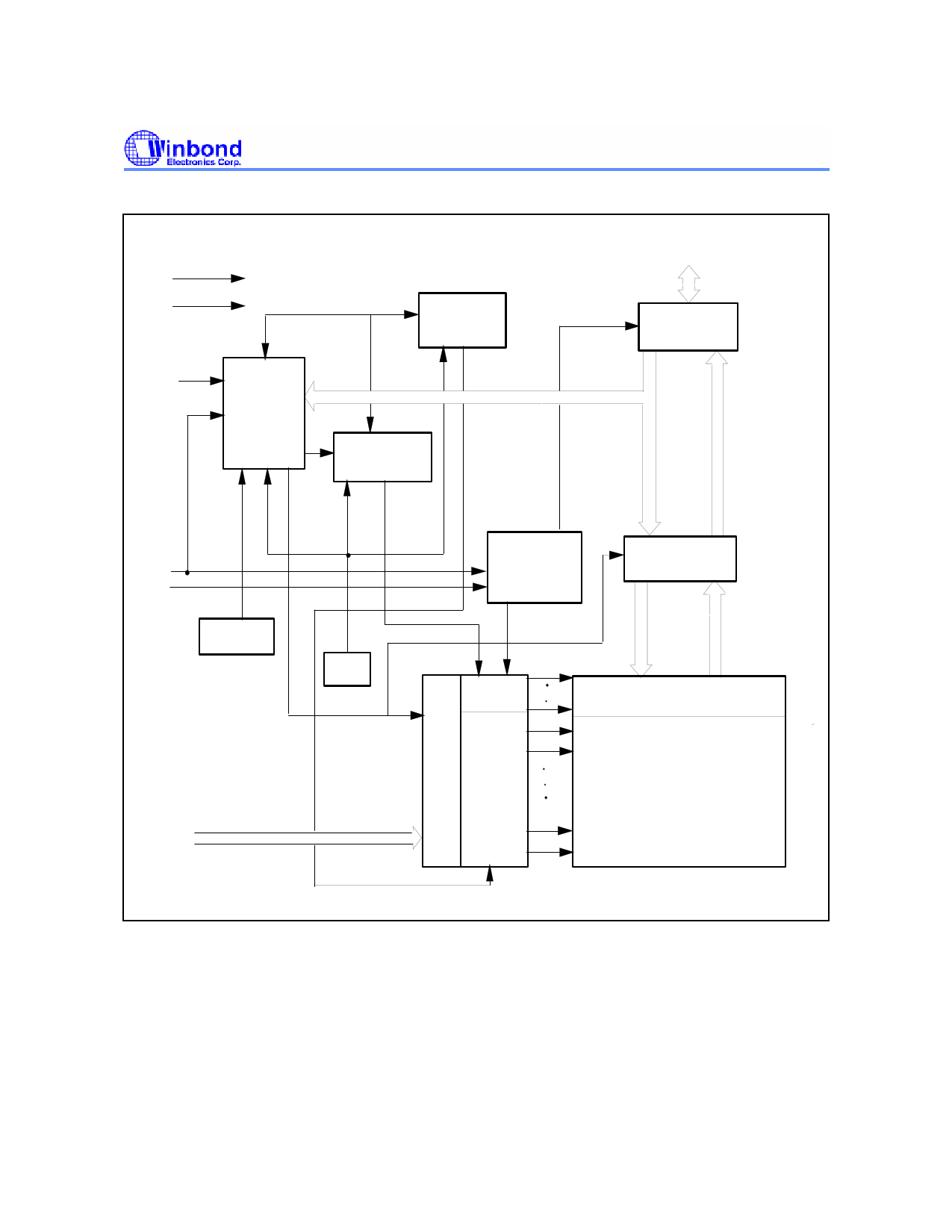

4. BLOCK DIAGRAM

VDD

Vss

#WE

State

Control

Command

Register

Erase Voltage

Generator

Program Voltage

Generator

W39F010

DQ0 - DQ7

Input / output

Buffers

#CE

#OE

VDD Detect

Timer

A0 - A16

Chip Enable

Output Enable

Logic

Data

latch

A

d Y-Decode

d

r

e

s

s X-decode

L

a

t

c

h

Y-MUX / SENSING

ARRAY

Publication Release Date: December 26, 2005

- 5 - Revision A4

5 Page

W39F010

Just prior to the completion of Embedded Algorithm operations DQ7 may change asynchronously

while the output enable (#OE) is asserted low. This means that the device is driving status information

on DQ7 at one instant of time and then that byte′s valid data at the next instant of time. Depending on

when the system samples the DQ7 output, it may read the status or valid data. Even if the device has

completed the Embedded Algorithm operations and DQ7 has a valid data, the data outputs on DQ0–

DQ6 may be still invalid. The valid data on DQ0 − DQ7 will be read on the successive read attempts.

The Data Polling feature is only active during the Embedded Programming Algorithm, Embedded

Erase Algorithm, or page erase time-out (see "Command Definitions").

6.5.2 DQ6: Toggle Bit

The W39F010 also features the "Toggle Bit" as a method to indicate to the host system that the

embedded algorithms are in progress or completed.

During an Embedded Program or Erase Algorithm cycle, successive attempts to read (#OE toggling)

data from the device at any address will result in DQ6 toggling between one and zero. Once the

Embedded Program or Erase Algorithm cycle is completed, DQ6 will stop toggling and valid data will

be read on the next successive attempt. During programming, the Toggle Bit is valid after the rising

edge of the fourth #WE pulse in the four write pulse sequence. For chip erase, the Toggle Bit is valid

after the rising edge of the sixth #WE pulse in the six write pulse sequence. For page erase, the

Toggle Bit is valid after the last rising edge of the page erase #WE pulse. The Toggle Bit is active

during the page erase time-out.

Either #CE or #OE toggling will cause DQ6 to toggle.

Publication Release Date: December 26, 2005

- 11 -

Revision A4

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet W39F010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W39F010 | 128K X 8 CMOS FLASH MEMORY | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |