|

|

PDF AT83SND2CDVX Data sheet ( Hoja de datos )

| Número de pieza | AT83SND2CDVX | |

| Descripción | (AT83SND2CDVX / AT83SND2CMP3) Single-Chip MP3 Decoder | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT83SND2CDVX (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

• MPEG I/II-Layer 3 Hardwired Decoder

– Stand-alone MP3 Decoder

– 48, 44.1, 32, 24, 22.05, 16 kHz Sampling Frequency

– Separated Digital Volume Control on Left and Right Channels (Software Control

using 31 Steps)

– Bass, Medium, and Treble Control (31 Steps)

– Bass Boost Sound Effect

– Ancillary Data Extraction

– CRC Error and MPEG Frame Synchronization Indicators

• 20-bit Stereo Audio DAC

– 93 dB SNR Playback Stereo Channel

– 32 Ohm/ 20 mW Stereo Headset Drivers

– Stereo Line Level Input, Differential Mono Auxiliary Input

• Programmable Audio Output for Interfacing with External Audio System

– I2S Format Compatible

• Mono Audio Power Amplifier

– 440mW on 8 Ohms Load

• USB Rev 1.1 Controller

– Full Speed Data Transmission

• Built-in PLL

– MP3 Audio Clocks

– USB Clock

• MultiMediaCard® Interface, Secure Digital Card Interface

• Standard Full Duplex UART with Baud Rate Generator

• Power Management

– Power-on Reset

– Idle Mode, Power-down Mode

• Operating Conditions:

– 2.7www.DataSheet4U.com to 3V, ±10%, 25 mA Typical Operating at 25°C

– 37 mA Typical Operating at 25°C Playing Music on Earphone

– Temperature Range: -40°C to +85°C

– Power Amplifier Supply 3.2V to 5.5V

• Packages

– CTBGA 100-pin

Typical

Applications

• MP3-Player

• PDA, Camera, Mobile Phone MP3

• Car Audio/Multimedia MP3

• Home Audio/Multimedia MP3

• Toys

• Industrial Background Music / Ads

Single-Chip MP3

Decoder with

Full Audio

Interface

AT83SND2CMP3

AT83SND2CDVX

Preliminary

Rev. 7524B–MP3–05/06

1 page

Signals

AT83SND2CMP3

All the AT83SND2CMP3 signals are detailed by functionality in following tables.

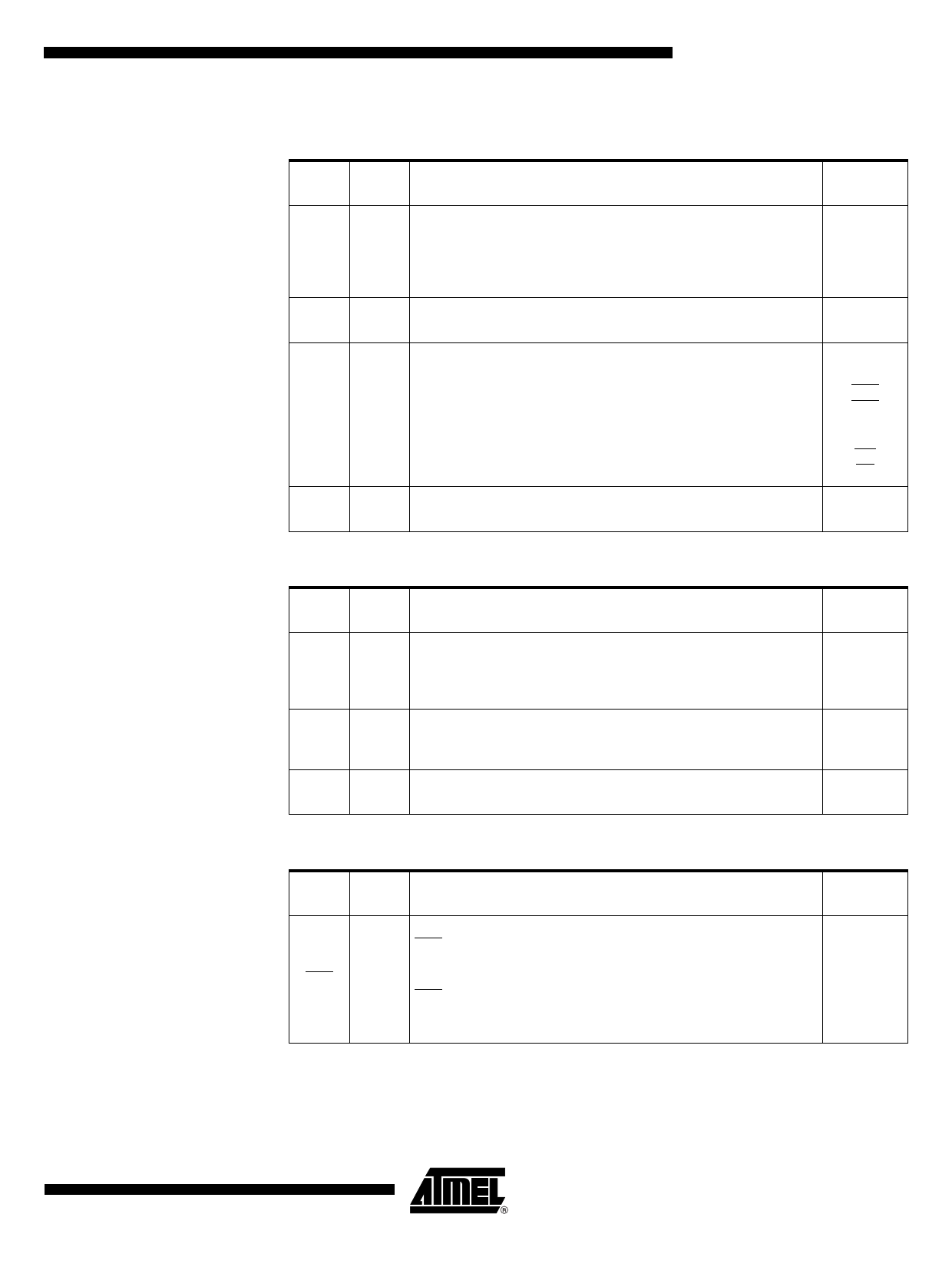

Table 1. Ports Signal Description

Signal

Name

P0.7:0

P2.7:0

P3.7:0

P4.3:0

Type Description

Port 0

P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s

I/O written to them float and can be used as high impedance inputs. To

avoid any parasitic current consumption, floating P0 inputs must be

polarized to VDD or VSS.

I/O

Port 2

P2 is an 8-bit bidirectional I/O port with internal pull-ups.

I/O

Port 3

P3 is an 8-bit bidirectional I/O port with internal pull-ups.

I/O

Port 4

P4 is an 8-bit bidirectional I/O port with internal pull-ups.

Alternate

Function

AD7:0

A15:8

RXD

TXD

INT0

INT1

T0

T1

WR

RD

Table 2. Clock Signal Description

Signal

Name

Type Description

Input to the on-chip inverting oscillator amplifier

X1

I

To use the internal oscillator, a crystal/resonator circuit is connected to

this pin. If an external oscillator is used, its output is connected to this

pin. X1 is the clock source for internal timing.

X2

FILT

Output of the on-chip inverting oscillator amplifier

O To use the internal oscillator, a crystal/resonator circuit is connected to

this pin. If an external oscillator is used, leave X2 unconnected.

I

PLL Low Pass Filter input

FILT receives the RC network of the PLL low pass filter.

Alternate

Function

-

-

-

Table 3. Timer 0 and Timer 1 Signal Description

Signal

Name

Type Description

Alternate

Function

INT0

Timer 0 Gate Input

INT0 serves as external run control for timer 0, when selected by

GATE0 bit in TCON register.

I External Interrupt 0

INT0 input sets IE0 in the TCON register. If bit IT0 in this register is set,

bit IE0 is set by a falling edge on INT0#. If bit IT0 is cleared, bit IE0 is

set by a low level on INT0#.

P3.2

7524B–MP3–05/06

5

5 Page

PLL Programming

AT83SND2CMP3

Figure 7). Value of the filter components are detailed in the Section “DC

Characteristics”.

The VCO block is the Voltage Controlled Oscillator controlled by the voltage Vref pro-

duced by the charge pump. It generates a square wave signal: the PLL clock.

Figure 6. PLL Block Diagram and Symbol

PLLCON.1

PLLEN

OSC

CLOCK

N divider

N6:0

PFLD

Up

Down

PFILT

CHP

Vref

VCO

PLL

Clock

PLOCK

PLLCON.0

R divider

R9:0

PLLclk = -O-----S----C----c----l--k----×-----(--R------+-----1----)

N+1

PLL

CLOCK

PLL Clock Symbol

Figure 7. PLL Filter Connection

FILT

R

C1

VSS

C2

VSS

The PLL is programmed using the flow shown in Figure 8. The PLL clock frequency will

depend on MP3 decoder clock and audio interface clock frequencies.

Figure 8. PLL Programming Flow

PLL

Programming

Configure Dividers

N6:0 = xxxxxxb

R9:0 = xxxxxxxxxxb

Enable PLL

PLLRES = 0

PLLEN = 1

PLL Locked?

PLOCK = 1?

7524B–MP3–05/06

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT83SND2CDVX.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT83SND2CDVX | (AT83SND2CDVX / AT83SND2CMP3) Single-Chip MP3 Decoder | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |