|

|

PDF QG80331M667 Data sheet ( Hoja de datos )

| Número de pieza | QG80331M667 | |

| Descripción | I/O Processor | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de QG80331M667 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Intel® 80331 I/O Processor

Specification Update

April 2006

The Intel® 80331 I/O Processor may contain design defects or errors known as errata that may

cause the product to deviate from published specifications. Current characterized errata are doc-

umented in this specification update.

Order Number: 273930-021US

1 page

Revision History

Date

www.DataSheet4U.com April 2006

February 2006

January 2006

December 2005

October 2005

August 2005

June 2005

May 2005

April 2005

March 2005

Version

Description

Added:

• D-1 stepping information to all Summary tables and to Table 1, “Intel® 80331 I/O Processor

Die Details” on page 17 and Table 2, “Intel® 80331 I/O Processor Device ID Registers” on

021 page 18

• Status change of Erratum 62

• Status change of Specification Change 22

• Status change of Specification Clarification 33

Added:

020 • Non-Core Errata 63

• Specification Clarification 33

Added:

019 • Non-Core Errata 62

• Specification Change 22

Added:

018 • Specification Clarification 31 and 32

• Documentation Change 17

Added:

017

• Specification Clarification 29 and 30

Added:

016 • Specification Clarification 27 and 28

• Documentation Change 16.

Added:

015

• Non-Core Errata 61

Added:

• Non-Core Errata 60

014 • Specification Change 21

Updated:

• Specification Change 13, 15, and 16

Added:

013

• Non-Core Errata 58 and 59

Added:

• Specification Change 19 and 20

• Documentation Change 15

• PB-free Markings to Table 1, “Intel® 80331 I/O Processor Die Details” on page 17

012 Updated:

• Non-Core Errata 4

• Updated Non-Core Errata 50

Changed:

• Status of Non-Core Errata 20 to Fixed

Specification Update

5

5 Page

Intel® 80331 I/O Processor

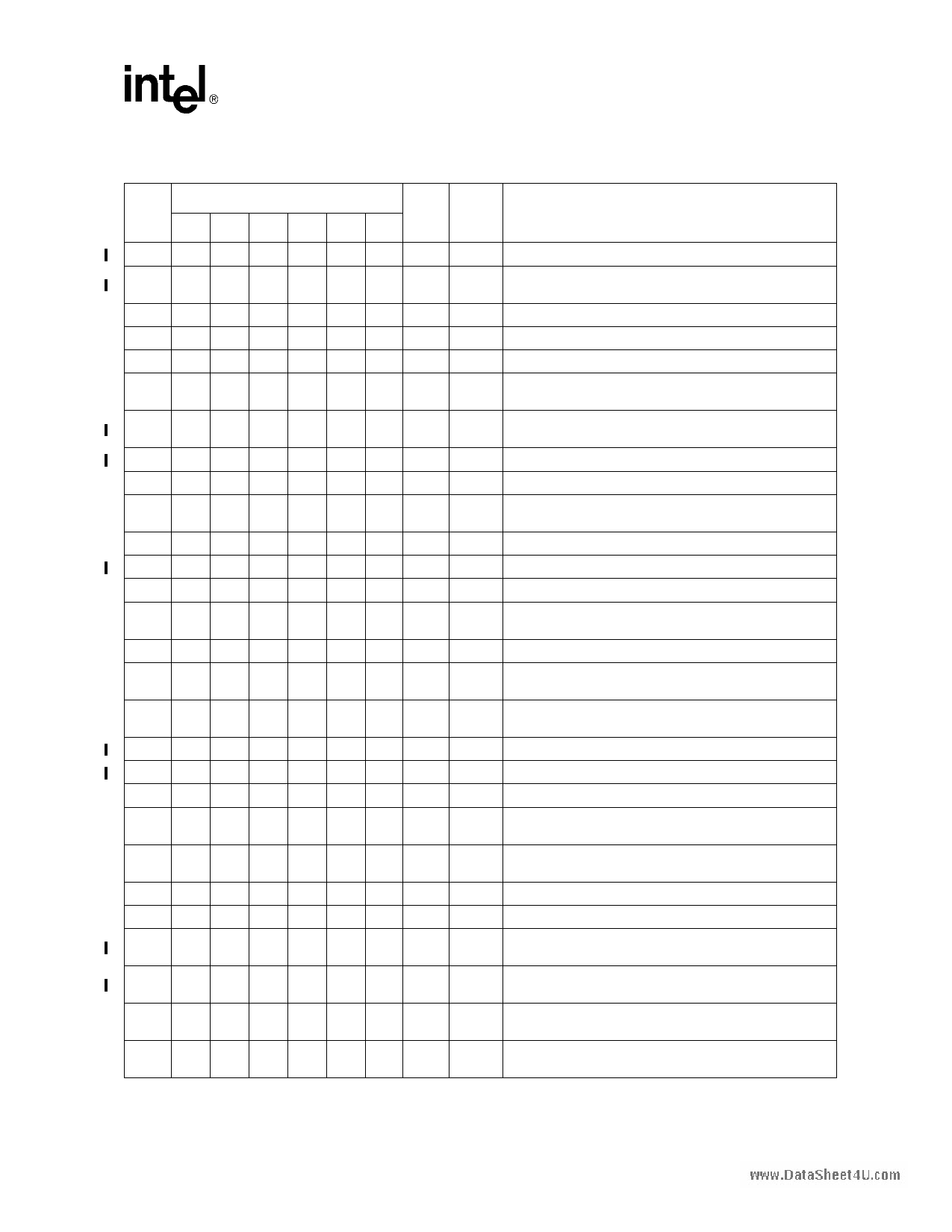

Summary Table of Changes

Non-Core Errata (Sheet 2 of 3)

No.

25

26

27

28

www.DataSheet4U.com 29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Steppings

Page Status

A-1 B-0 C-0 C-1 D-0 D-1

Errata

X X X X X X 25 No Fix Boundary scan multi-chip module implementation

X

X

X

X

X

X

25

No Fix

Auto refresh command also generates a Precharge All

command on DDR bus

X 26 Fixed SERR# set to incorrect voltage

X 26 Fixed M66EN set to incorrect voltage

X 26 Fixed P_INT[D:A]# not operating correctly

X

26

Fixed

Secondary bus may not initialize correctly at 100 MHz

PCI-X or 133 MHz PCI-X

X

X

X

X

X

X

26

No Fix

Coalesced writes to 32-bit memory can cause data

corruption

X X X X X X 27 No Fix ATU passing rules operation in PCI mode

XX

27 Fixed S_INT[D:A]# pull-ups disabled by Internal Bus Reset

XX

XX

27

Fixed

MCU Preemption Control does not properly manage the

byte count

28 Fixed I2C unit hang condition

X X X X X X 28 No Fix VPD Data Register bit 19 is not read/write

XX

29 Fixed Intel XScale® Core lockup condition

XX

30

Fixed

32-bit region write corrupts ECC immediately after 64-bit

Read-Modify-Write

X 30 Fixed Reset straps incorrectly sampled on the secondary reset

XX

31

Fixed

PCI-X to PCI Memory Read double-word near 1MB

boundary may cause the system to hang

XX

31

Fixed

PCI-X to PCI Memory Read Block across 1MB boundary

may cause data corruption

X X X X X X 32 No Fix DMA CRC result is byte reversed

X X X X X X 32 No Fix CRC corruption on PCI-to-local DMA transfers

XXXX

32 Fixed Byte Count Modified bit set to 1

XXXX

33

Fixed

Corrupted byte count and data when crossing 1 MByte

boundary in PCI-X to PCI mode

XXXX

33

Fixed

PCI-X to PCI Memory Read with 4 K byte count and

unaligned starting address

XXX

34 Fixed VCCDDR (VCC25/VCC18) Current Spike

XXXX

35 Fixed Bridge PCI ordering rule violation

X

X

X

X

X

X

35

No Fix

ATU claims PCI commands 8 and 9 when issued as Dual

Address Cycle (DAC)

X

X

X

X

X

X

36

No Fix

Secondary bus PCI RST# pulse prior to the rising edge of

P_RST#

XX

36

Fixed

Slow edge rates observed when 80331 is driving the

primary bus

XXXX

37

Fixed

Enabling the core-to-memory port can cause a stall

condition

Specification Update

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet QG80331M667.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| QG80331M667 | I/O Processor | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |