|

|

PDF UT54ACS74 Data sheet ( Hoja de datos )

| Número de pieza | UT54ACS74 | |

| Descripción | Radiation-Hardened Dual D Flip-Flops | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UT54ACS74 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

UT54ACS74/UT54ACTS74

Radiation-Hardened

Dual D Flip-Flops with Clear & Preset

FEATURES

• radiation-hardened CMOS

- Latchup immune

• High speed

• Low power consumption

www.DataSh•eetS4Uin.cgolem5 volt supply

• Available QML Q or V processes

• Flexible package

- 14-pin DIP

- 14-lead flatpack

DESCRIPTION

The UT54ACS74 and the UT54ACTS74 contain two indepen-

dent D-type positive triggered flip-flops. A low level at the

Preset or Clear inputs sets or resets the outputs regardless of the

levels of the other inputs. When Preset and Clear are inactive

(high), data at the D input meeting the setup time requirement

is transferred to the outputs on the positive-going edge of the

clock pulse. Following the hold time interval, data at the D

input may be changed without affecting the levels at the outputs.

The devices are characterized over full military temperature

range of -55 C to +125 C.

FUNCTION TABLE

PRE

L

H

L

H

H

H

INPUTS

CLR

CLK

HX

LX

LX

H

H

HL

OUTPUT

D QQ

XHL

X LH

X H1 H1

HHL

L LH

X Qo Qo

Note:

1. The output levels in this configuration are not guaranteed to meet the mini-

mum levels for VOH if the lows at preset and clear are near VIL maximum.

In addition, this configuration is nonstable; that is, it will not persist when

either preset or clear returns to its inactive (high) level.

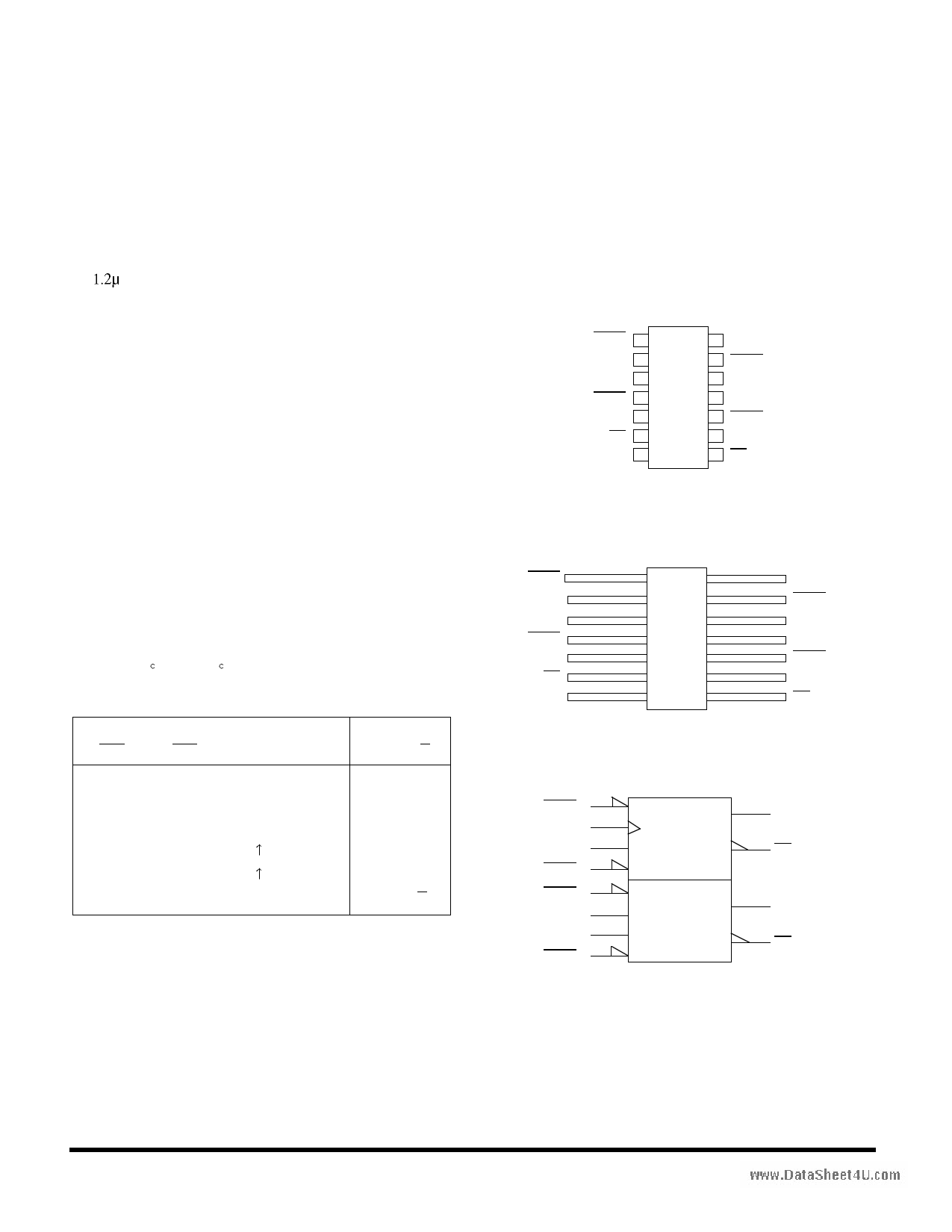

PINOUTS

14-Pin DIP

Top View

CLR1

D1

CLK1

PRE1

Q1

Q1

VSS

1 14

2 13

3 12

4 11

5 10

69

78

VDD

CLR2

D2

CLK2

PRE2

Q2

Q2

14-Lead Flatpack

Top View

CLR1

D1

CLK1

PRE1

Q1

Q1

VSS

1 14

2 13

3 12

4 11

5 10

69

78

VDD

CLR2

D2

CLK2

PRE2

Q2

Q2

LOGIC SYMBOL

(4)

PRE1

(3)

CLK1

(2)

D1

(1)

CLR1

(10)

PRE2

(11)

CLK2

(12)

D2

(13)

CLR2

S

C1

D1

R

(5) Q1

(6) Q1

(9) Q2

(8) Q2

Note:

1. Logic symbol in accordance with ANSI/IEEE standard 91-1984 and IEC

Publication 617-12.

45 RadHard MSI Logic

1 page

UT54ACS74/UT54ACTS74

Notes:

1. Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, - 0%; VIL = VIL(max) + 0%,

- 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but

are guaranteed to VIH(min) and VIL(max).

2. Supplied as a design limit but not guaranteed or tested.

3. Per MIL-PRF-38535, for current density 5.0E5 amps/cm2, the maximum product of load capacitance (per output buffer) times frequency should not exceed

3,765 pF/MHz.

4. Not more than one output may be shorted at a time for maximum duration of one second.

5. Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and VSS

at a frequency of 1MHz and a signal amplitude of 50mV rms maximum.

6. Maximum allowable relative shift equals 50mV.

7. All specifications valid for radiation dose 1E6 rads(Si).

8. Power does not include power contribution of any TTL output sink current.

9. Power dissipation specified per switching output.

10. This value is guaranteed based on characterization data, but not tested.

www.DataSheet4U.com

49 RadHard MSI Logic

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet UT54ACS74.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UT54ACS74 | Radiation-Hardened Dual D Flip-Flops with Clear & Preset | Aeroflex Microelectronic Solutions |

| UT54ACS74 | Radiation-Hardened Dual D Flip-Flops | ETC |

| UT54ACS74 | Dual D Flip-Flops | Aeroflex Circuit Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |