|

|

PDF AT91SAM9261S Data sheet ( Hoja de datos )

| Número de pieza | AT91SAM9261S | |

| Descripción | AT91 ARM Thumb-based Microcontrollers | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT91SAM9261S (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• Incorporates the ARM926EJ-S™ ARM® Thumb® Processor

– DSP Instruction Extensions

– ARM Jazelle® Technology for Java® Acceleration

– 16 Kbyte Data Cache, 16 Kbyte Instruction Cache, Write Buffer

– 210 MIPS at 190 MHz

– Memory Management Unit

– EmbeddedICE™, Debug Communication Channel Support

– Mid-level implementation Embedded Trace Macrocell™

• Additional Embedded Memories

– 32 Kbytes of Internal ROM, Single-cycle Access at Maximum Bus Speed

– 16 Kbytes of Internal SRAM, Single-cycle Access at Bus Speed

• External Bus Interface (EBI)

– Supports SDRAM, Static Memory, NAND Flash and CompactFlash®

• LCD Controller

– Supports Passive or Active Displays

– Up to 16-bits per Pixel in STN Color Mode

– Up to 16M Colors in TFT Mode (24-bit per Pixel), Resolution up to 2048 x 2048

• USB

– USB 2.0 Full Speed (12 Mbits per second) Host Double Port

• Dual On-chip Transceivers

• Integrated FIFOs and Dedicated DMA Channels

– USB 2.0 Full Speed (12 Mbits per second) Device Port

• On-chip Transceiver, 2 Kbyte Configurable Integrated FIFOs

• Bus Matrix

– Handles Five Masters and Five Slaves

– Boot Mode Select Option

– Remap Command

• Fully Featured System Controller (SYSC) for Efficient System Management, including

– Reset Controller, Shutdown Controller, Four 32-bit Battery Backup Registers for a

Total of 16 Bytes

– Clock Generator and Power Management Controller

– Advanced Interrupt Controller and Debug Unit

– Periodic Interval Timer, Watchdog Timer and Real-time Timer

– Three 32-bit PIO Controllers

• Reset Controller (RSTC)

– Based on Power-on Reset Cells, Reset Source Identification and Reset Output

Control

• Shutdown Controller (SHDWC)

– Programmable Shutdown Pin Control and Wake-up Circuitry

• Clock Generator (CKGR)

– 32,768 Hz Low-power Oscillator on Battery Backup Power Supply, Providing a

Permanent Slow Clock

– 3 to 20 MHz On-chip Oscillator and two PLLs

• Power Management Controller (PMC)

– Very Slow Clock Operating Mode, Software Programmable Power Optimization

Capabilities

– Four Programmable External Clock Signals

AT91 ARM

Thumb-based

Microcontrollers

AT91SAM9261S

Summary

6242DS–ATARM–06-Jan-09

1 page

AT91SAM9261S

www.DataSheet4U.com

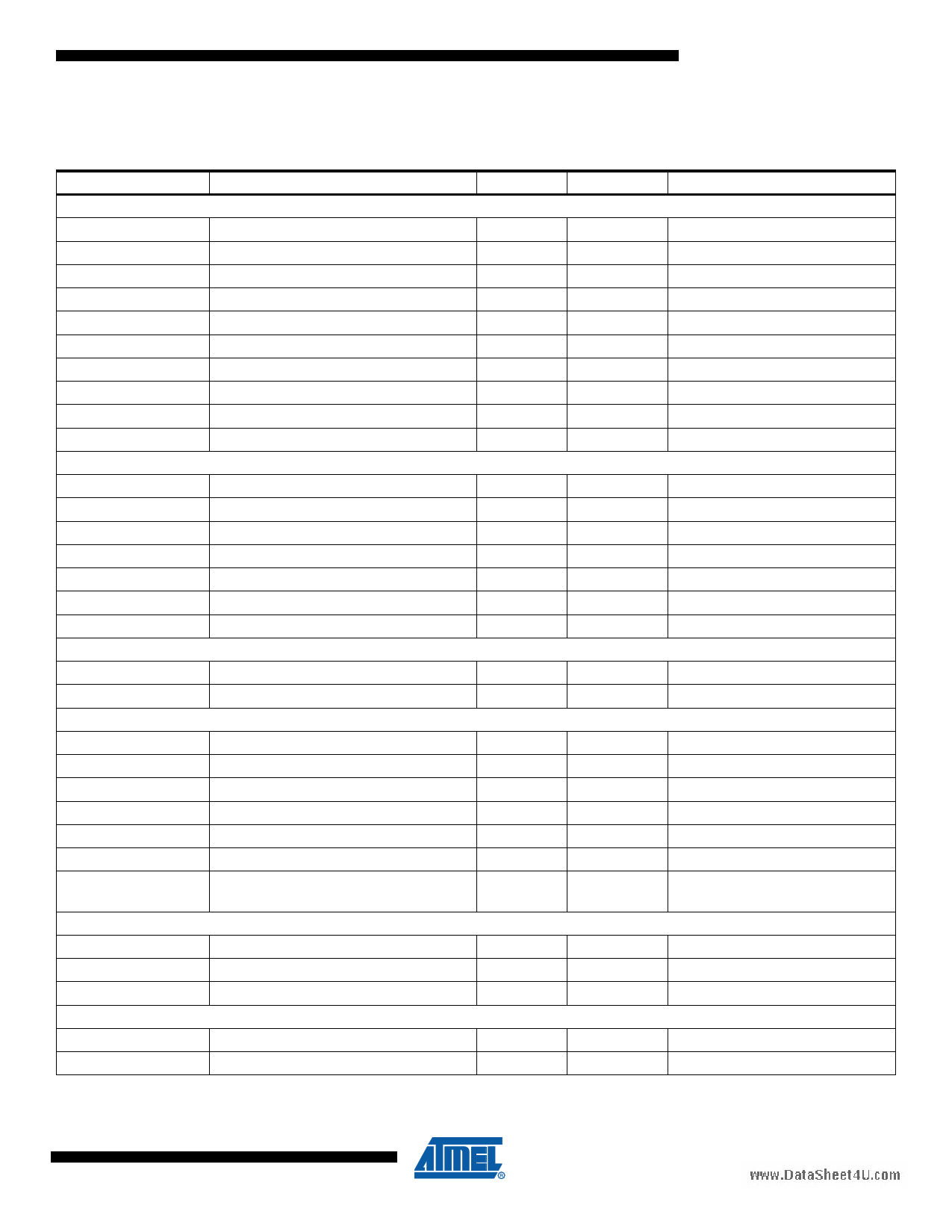

3. Signal Description

Table 3-1. Signal Description by Peripheral

Signal Name

Function

Type

Active Level

Power

VDDIOM

EBI I/O Lines Power Supply

Power

VDDIOP

Peripherals I/O Lines Power Supply

Power

VDDBU

Backup I/O Lines Power Supply

Power

VDDPLL

PLL Power Supply

Power

VDDOSC

Oscillator Power Supply

Power

VDDCORE

Core Chip Power Supply

Power

GND

Ground

Ground

GNDPLL

PLL Ground

Ground

GNDOSC

Oscillator Ground

Ground

GNDBU

Backup Ground

Ground

Clocks, Oscillators and PLLs

XIN Main Oscillator Input

Input

XOUT

Main Oscillator Output

Output

XIN32

Slow Clock Oscillator Input

Input

XOUT32

Slow Clock Oscillator Output

Output

PLLRCA

PLL Filter

Input

PLLRCB

PLL Filter

Input

PCK0 - PCK3

Programmable Clock Output

Output

Shutdown, Wakeup Logic

SHDN

Shutdown Control

Output

WKUP

Wake-Up Input

Input

ICE and JTAG

TCK

Test Clock

Input

RTCK

Returned Test Clock

Output

TDI Test Data In

Input

TDO

Test Data Out

Output

TMS

Test Mode Select

Input

NTRST

Test Reset Signal

Input

Low

JTAGSEL

JTAG Selection

Input

NRST

TST

BMS

DRXD

DTXD

Microcontroller Reset

Test Mode Select

Boot Mode Select

Debug Receive Data

Debug Transmit Data

Reset/Test

I/O

Input

Input

Debug Unit

Input

Output

Low

Comments

1.65 V to 1.95V and 3.0V to 3.6V

2.7V to 3.6V

1.08V to 1.32V

3.0V to 3.6V

3.0V to 3.6V

1.08V to 1.32V

Do not tie over VDDBU.

Accepts between 0V and VDDBU.

No pull-up resistor.

No pull-up resistor.

No pull-up resistor.

No pull-up resistor.

Pull-up resistor.

Pull-down resistor. Accepts

between 0V and VDDBU.

Pull-up resistor

Pull-down resistor.

6242DS–ATARM–06-Jan-09

5

5 Page

www.DataSheet4U.com

5. Power Considerations

AT91SAM9261S

5.1 Power Supplies

The AT91SAM9261S has six types of power supply pins:

• VDDCORE pins: Power the core, including the processor, the memories and the peripherals;

voltage ranges from 1.08V and 1.32V, 1.2V nominal.

• VDDIOM pins: Power the External Bus Interface I/O lines; voltage ranges from 1.65V to

1.95V and 3.0V to 3.6V, 1.8V and 3.3V nominal.

• VDDIOP pins: Power the Peripheral I/O lines and the USB transceivers; voltage ranges from

2.7V and 3.6V, 3.3V nominal.

• VDDBU pin: Powers the Slow Clock oscillator and a part of the System Controller; voltage

ranges from 1.08V and 1.32V, 1.2V nominal.

• VDDPLL pin: Powers the PLL cells; voltage ranges from 3.0V and 3.6V, 3.3V nominal.

• VDDOSC pin: Powers the Main Oscillator cells; voltage ranges from 3.0V and 3.6V, 3.3V

nominal.

The double power supplies VDDIOM and VDDIOP are identified in Table 4-1 on page 10. These

supplies enable the user to power the device differently for interfacing with memories and for

interfacing with peripherals.

Ground pins GND are common to VDDCORE, VDDIOM and VDDIOP pins power supplies. Sep-

arated ground pins are provided for VDDBU, VDDOSC and VDDPLL. The ground pins are

GNDBU, GNDOSC and GNDPLL, respectively.

5.2 Power Consumption

The AT91SAM9261S consumes about 550 µA of static current on VDDCORE at 25°C. This

static current rises at up to 5.5 mA if the temperature increases to 85°C.

On VDDBU, the current does not exceed 3 µA @25°C, but can rise at up to 20 µA @85°C.

For dynamic power consumption, the AT91SAM9261S consumes a maximum of 50 mA on

VDDCORE at maximum speed in typical conditions (1.2V, 25°C), processor running full-perfor-

mance algorithm.

6. I/O Line Considerations

6.1 JTAG Port Pins

TMS, TDI and TCK are Schmitt trigger inputs and have no pull-up resistors.

TDO and RTCK are outputs, driven at up to VDDIOP, and have no pull-up resistor.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level (tied

to VDDBU). It integrates a permanent pull-down resistor of about 15 kΩ to GNDBU, so that it can

be left unconnected for normal operations.

The NTRST pin is used to initialize the embedded ICE TAP Controller when asserted at a low

level. It integrates a permanent pull-up resistor of about 15 kΩ to VDDIOP, so that it can be left

unconnected for normal operations.

6242DS–ATARM–06-Jan-09

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT91SAM9261S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT91SAM9261 | ARM926EJ-S Based Microcontroller | ATMEL Corporation |

| AT91SAM9261-EK | Evaluation Board | ATMEL Corporation |

| AT91SAM9261S | AT91 ARM Thumb-based Microcontrollers | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |