|

|

PDF PO74HSTL85331A Data sheet ( Hoja de datos )

| Número de pieza | PO74HSTL85331A | |

| Descripción | 3.3V 1:4 Crystal Oscillator/ Differential Clock or Data Fanout Buffer | |

| Fabricantes | Potato Semiconductor Corporation | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PO74HSTL85331A (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

PO74HSTL85331A

3.3V 1:4 Crystal Oscillator/

Differential Clock or Data Fanout Buffer

700MHz HSTL Potato Chip

03/01/07

FEATURES:

DESCRIPTION:

. Patented Technology

The PO74HSTL85331A is a low skew, high performance

. Four HSTL differential outputs

1-to-4 Crystal Oscillator/Differential-to-3.3V HSTL

. Selectable differential CLK, nCLK or crystal inputs fanout buffer of High Performance Clock Solutions from

. CLK, nCLK pair can accept the following differential PotatoSemi. The PO74HSTL85331A has selectable

input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL differential clock or crystal inputs. The CLK, nCLK pair

. Operating frequency up to 700MHz with 2pf load

can accept most standard differential input levels. The

. Operating frequency up to 550MHz with 5pf load

clock enable is internally synchronized to eliminate runt

. Operating frequency up to 400MHz with 15pf load pulses on the outputs during asynchronous

. Very low output pin to pin skew < 50ps

assertion/deassertion of the clock enable pin.

. 3.3-ns propagation delay (typical)

. 2.4V to 3.6V power supply

. Industrial temperature range: –40°C to 85°C

. 20-pin TSSOP package

Guaranteed output and part-to-part skew characteristics

make the PO74HSTL85331A ideal for those applications

demanding well defined performance and repeatability.

Pin Configuration

VEE

CLK_EN

CLK_SEL

CLK

nCLK

XTAL1

XTAL2

nc

nc

VCC

1

2

3

4

5

6

7

8

9

10

20 Q0

19 nQ0

18 VCC

17 Q1

16 nQ1

15 Q2

14 nQ2

13 VCC

12 Q3

11 nQ3

Logic Block Diagram

CLK_EN

CLK

nCLK

XTAL1

XTAL2

CLK_SEL

0

1

D

Q

LE

Q0

nQ0

Q1

nQ1

Q2

nQ2

Q3

nQ3

1

Copyright © Potato Semiconductor Corporation

1 page

www.DataSheet4U.com

PO74HSTL85331A

3.3V 1:4 Crystal Oscillator/

Differential Clock or Data Fanout Buffer

700MHz HSTL Potato Chip

08/03/06

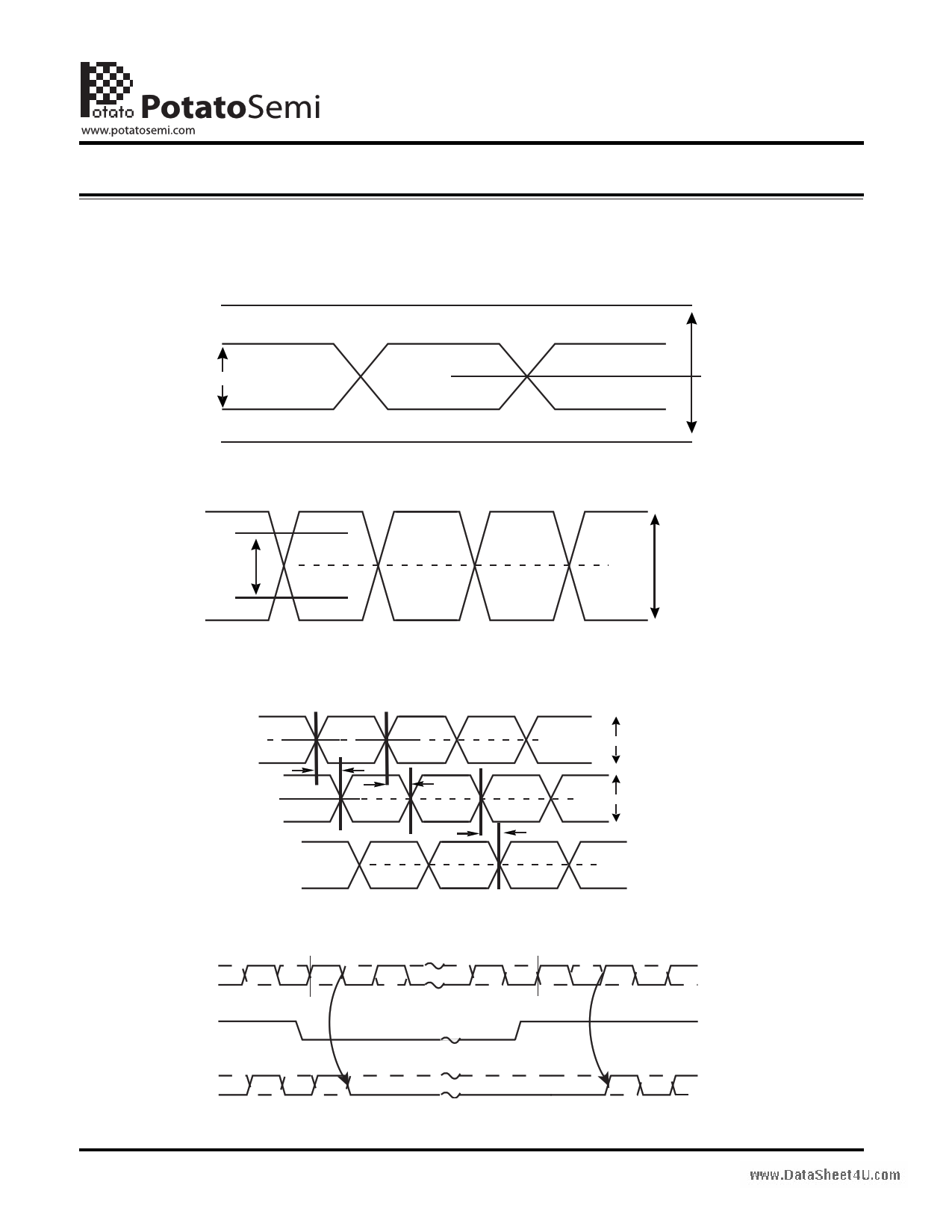

Test Waveforms

FIGURE 1. LVDS/ PECL/ ECL/ HSTL /DIFFERENTIAL INPUT WAVEFORM DEFINITIONS

VIH

VCC= 3.3V

VPP RANGE

VPP 0V-VCC

VIL

VEE=0.0V

VCC

VEE

FIGURE 2. HSTL/HSTL OUTPUT

tr,tf,

20-80%

VO

FIGURE 3. Propogation Delay, Output pulse skew, and output-to-output skew

for both CLKA or CLKB to output pair

INPUT

CLOCK

OUTPUT

CLOCK

TPLH

TPD

ANOTHER

OUTPUT

CLOCK

TPHL

FIGURE 4. CLK_EN Timing Diagram

nCLK

CLK

Disabled

CLK_EN

VPP

tSK(O)

VO

Enabled

nQ0:nQ3

Q0:Q3

5

Copyright © Potato Semiconductor Corporation

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet PO74HSTL85331A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PO74HSTL85331A | 3.3V 1:4 Crystal Oscillator/ Differential Clock or Data Fanout Buffer | Potato Semiconductor Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |