|

|

PDF BLD6G21LS-50 Data sheet ( Hoja de datos )

| Número de pieza | BLD6G21LS-50 | |

| Descripción | TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de BLD6G21LS-50 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

BLD6G21L-50; BLD6G21LS-50

TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty

transistor

Rev. 01 — 28 October 2009

Objective data sheet

1. Product profile

1.1 General description

The BLD6G21L-50 and BLD6G21LS-50 incorporate a fully integrated Doherty solution

using NXP’s state of the art GEN6 LDMOS technology. This device is perfectly suited for

TD-SCDMA base station applications at frequencies from 2010 MHz to 2025 MHz. The

main and peak device, input splitter and output combiner are integrated in a single

package. This package consists of one gate and drain lead and two extra leads of which

one is used for biasing the peak amplifier and the other is not connected. It only requires

the proper input/output match and bias setting as with a normal class-AB transistor.

Table 1. Typical performance

RF performance at Th = 25 °C.

Mode of operation

f

(MHz)

TD-SCDMA [1][2]

2010 to 2025

VDS PL(AV)

(V) (W)

28 8

Gp ηD ACPR

(dB) (%) (dBc)

13.5 42 −23

[1] Test signal: 6-carrier TD-SCDMA; PAR = 10.8 dB at 0.01 % probability on CCDF.

[2] IDq = 170 mA (main); VGS(amp)peak = 0 V.

PL(3dB)

(W)

50

CAUTION

www.DataSheet4U.com

This device is sensitive to ElectroStatic Discharge (ESD). Therefore care should be taken

during transport and handling.

1.2 Features

I Typical TD-SCDMA performance at frequencies from 2010 MHz to 2025 MHz:

N Average output power = 8 W

N Power gain = 13.5 dB

N Efficiency = 42 %

I Fully optimized integrated Doherty concept:

N integrated asymmetrical power splitter at input

N integrated power combiner

N peak biasing down to 0 V

N low junction temperature

N high efficiency

I Integrated ESD protection

1 page

NXP Semiconductors

BLD6G21L-50; BLD6G21LS-50

TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor

gate

ZS

Fig 2. Definition of transistor impedance

drain

ZL

001aaf059

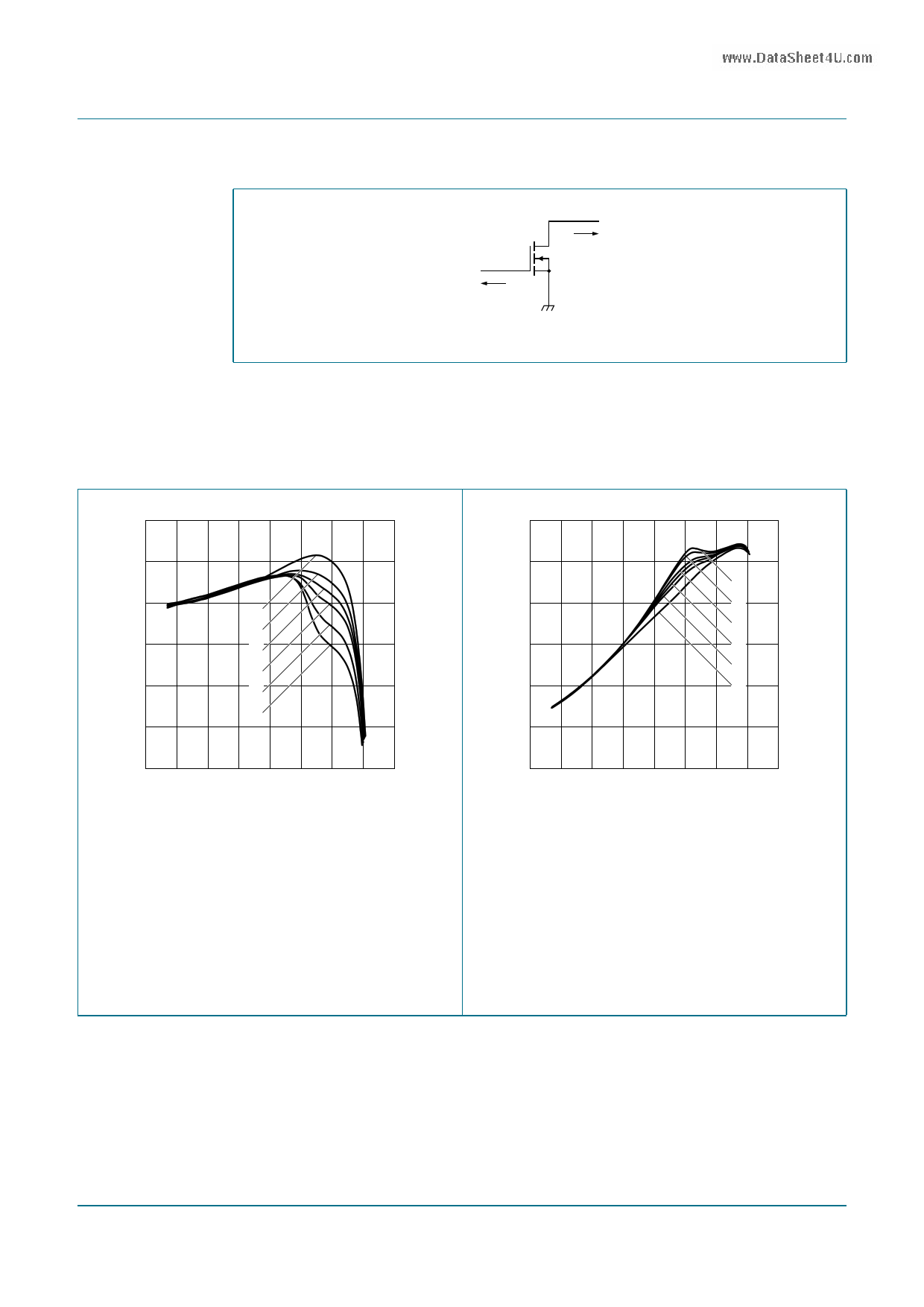

8.3 Performance curves

Performance curves are measured in a BLD6G21L-50 application circuit.

8.3.1 CW pulsed

16

Gp

(dB)

14

12

001aak934

(6)

(5)

(4)

(3)

(2)

(1)

60

ηD

(%)

40

20

001aak935

(1)

(2)

(3)

(4)

(5)

(6)

10

www.DataSheet43U0.com 35

40

45 50

PL (dBm)

VDS = 28 V; IDq = 170 mA (main); Tcase = 25 °C;

f = 2017.5 MHz; δ = 10 %; tp = 100 µs on 1 ms period.

(1) VGS(amp)peak = 0 V

(2) VGS(amp)peak = 0.2 V

(3) VGS(amp)peak = 0.4 V

(4) VGS(amp)peak = 0.5 V

(5) VGS(amp)peak = 0.6 V

(6) VGS(amp)peak = 0.8 V

Fig 3. Power gain as a function of load power;

typical values

0

30 35 40 45 50

PL (dBm)

VDS = 28 V; IDq = 170 mA (main); Tcase = 25 °C;

f = 2017.5 MHz; δ = 10 %; tp = 100 µs on 1 ms period.

(1) VGS(amp)peak = 0 V

(2) VGS(amp)peak = 0.2 V

(3) VGS(amp)peak = 0.4 V

(4) VGS(amp)peak = 0.5 V

(5) VGS(amp)peak = 0.6 V

(6) VGS(amp)peak = 0.8 V

Fig 4. Drain efficiency as a function of load power;

typical values

BLD6G21L-50_BLD6G21LS-50_1

Objective data sheet

Rev. 01 — 28 October 2009

© NXP B.V. 2009. All rights reserved.

5 of 14

5 Page

NXP Semiconductors

BLD6G21L-50; BLD6G21LS-50

TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor

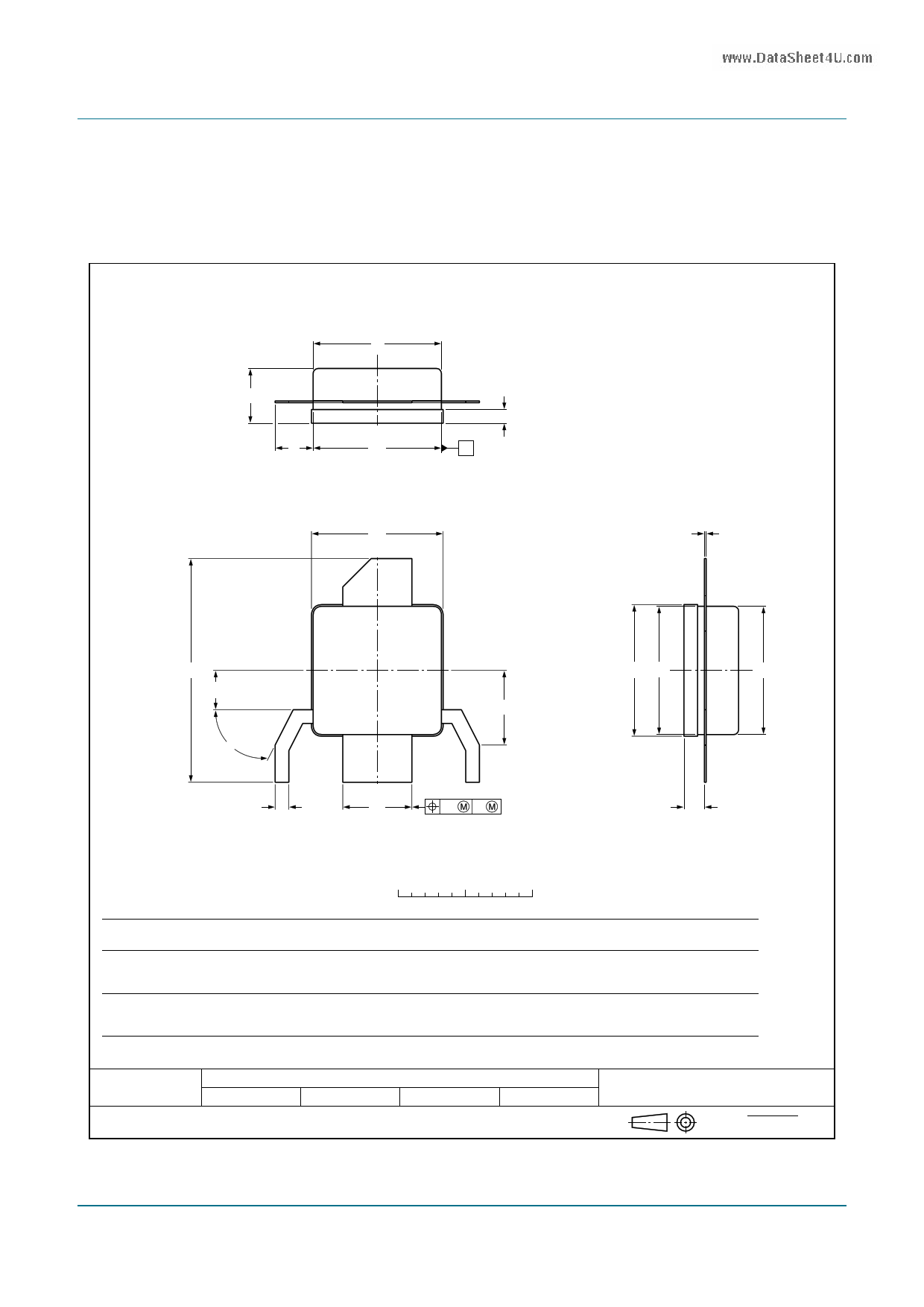

Earless flanged ceramic package; 4 leads

A

L

D

3

D1

U1

1

F

D

SOT1130B

c

H

Z

α

w w w . D a t a S h e e 4t 4 U . c 2o m

b b1

Z1

5

w2 D

U2 E1

E

Q

Dimensions

0 5 10 mm

scale

Unit(1) A b b1 c D D1 E E1 F H L Q U1 U2 w2 Z Z1 α

max 4.65 1.14 5.26 0.18 9.65 9.65 9.65 9.65 1.14 17.12 3.00 1.70 9.91 9.91

3.05 5.66 64°

mm nom

0.51

min 3.76 0.89 5.00 0.10 9.40 9.40 9.40 9.40 0.89 16.10 2.69 1.45 9.65 9.65

2.79 5.41 62°

max 0.183 0.045 0.207 0.007 0.38 0.38 0.38 0.38 0.045 0.674 0.118 0.069 0.39 0.39

0.120 0.223 64°

inches nom

0.02

min 0.148 0.035 0.197 0.004 0.37 0.37 0.37 0.37 0.035 0.634 0.106 0.059 0.38 0.38

0.110 0.213 62°

Note

1. millimeter dimensions are derived from the original inch dimensions.

sot1130b_po

Outline

version

References

IEC

JEDEC

JEITA

European

projection

Issue date

SOT1130B

09-07-23

09-10-12

Fig 15. Package outline SOT1130B

BLD6G21L-50_BLD6G21LS-50_1

Objective data sheet

Rev. 01 — 28 October 2009

© NXP B.V. 2009. All rights reserved.

11 of 14

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet BLD6G21LS-50.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BLD6G21LS-50 | TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |