|

|

PDF AT52BC3221AT Data sheet ( Hoja de datos )

| Número de pieza | AT52BC3221AT | |

| Descripción | 32-Mbit Flash 8-Mbit PSRAM Stack Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT52BC3221AT (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

• 32-Mbit Flash and 4-Mbit/8-Mbit PSRAM

• Single 66-ball (8 mm x 10 mm x 1.2 mm) CBGA Package

• 2.7V to 3.3V Operating Voltage

Flash

• 32-megabit (2M x 16)

• 2.7V to 3.3V Read/Write

• Access Time – 70 ns

• Sector Erase Architecture

– Sixty-three 32K Word Sectors with Individual Write Lockout

– Eight 4K Word Sectors with Individual Write Lockout

• Fast Word Program Time – 15 µs

• Suspend/Resume Feature for Erase and Program

– Supports Reading and Programming from Any Sector by Suspending Erase of a

Different Sector

– Supports Reading Any Word by Suspending Programming of Any Other Word

• Low-power Operation

– 12 mA Active

– 13 µA Standby

• Data Polling, Toggle Bit, Ready/Busy for End of Program Detection

• VPP Pin for Write Protection and Accelerated Program/Erase Operations

• RESET Input for Device Initialization

• Sector Lockdown Support

• Top or Bottom Boot Block Configuration Available

• 128-bit Protection Register

• Minimum 100,000 Erase Cycles

PSRAM

• 8-megabit (512K x 16)

• 2.7V to 3.3V VCC

• 70 ns Access Time

• Extended Temperature Range

• ISB0 < 10 µA when Deep Power-Down

www.DataSheet4U.com

32-Mbit Flash +

8-Mbit PSRAM

Stack Memory

AT52BC3221A

AT52BC3221AT

Preliminary

Device Number

AT52BC3221A

AT52BC3221AT

Flash Boot

Location

Bottom

Top

Flash Plane

Configuration

32M (2M x 16)

32M (2M x 16)

PSRAM

Configuration

8M (512K x 16)

8M (512K x 16)

Rev. 3466A–STKD–11/04

1

1 page

Device

Operation

3466A–STKD–11/04

AT52BC3221A(T)

www.DataSheet4U.com

READ: The 32-Mbit Flash memory is accessed like an EPROM. When CE and OE are low

and WE is high, the data stored at the memory location determined by the address pins are

asserted on the outputs. The outputs are put in the high impedance state whenever CE or OE

is high. This dual-line control gives designers flexibility in preventing bus contention.

COMMAND SEQUENCES: When the device is first powered on, it will be reset to the read or

standby mode, depending upon the state of the control line inputs. In order to perform other

device functions, a series of command sequences are entered into the device. The command

sequences are shown in the “Command Definition in Hex” table on page 12 (I/O8 - I/O15 are

don’t care inputs for the command codes). The command sequences are written by applying a

low pulse on the WE or CE input with CE or WE low (respectively) and OE high. The address

is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the

first rising edge of CE or WE. Standard microprocessor write timings are used. The address

locations used in the command sequences are not affected by entering the command

sequences.

RESET: A RESET input pin is provided to ease some system applications. When RESET is at

a logic high level, the device is in its standard operating mode. A low level on the RESET input

halts the present device operation and puts the outputs of the device in a high impedance

state. When a high level is reasserted on the RESET pin, the device returns to the read or

standby mode, depending upon the state of the control inputs.

ERASURE: Before a word can be reprogrammed, it must be erased. The erased state of

memory bits is a logical “1”. The entire device can be erased by using the Chip Erase com-

mand or individual sectors can be erased by using the Sector Erase command.

CHIP ERASE: The entire device can be erased at one time by using the six-byte chip erase

software code. After the chip erase has been initiated, the device will internally time the erase

operation so that no external clocks are required. The maximum time to erase the chip is tEC.

If the sector lockdown has been enabled, the chip erase will not erase the data in the sector

that has been locked out; it will erase only the unprotected sectors. After the chip erase, the

device will return to the read or standby mode.

SECTOR ERASE: As an alternative to a full chip erase, the device is organized into 71 sec-

tors (SA0 - SA70) that can be individually erased. The Sector Erase command is a six-bus

cycle operation. The sector address is latched on the falling WE edge of the sixth cycle while

the 30H data input command is latched on the rising edge of WE. The sector erase starts after

the rising edge of WE of the sixth cycle. The erase operation is internally controlled; it will

automatically time to completion. The maximum time to erase a sector is tSEC. When the sec-

tor programming lockdown feature is not enabled, the sector will erase (from the same Sector

Erase command). An attempt to erase a sector that has been protected will result in the oper-

ation terminating immediately.

WORD PROGRAMMING: Once a memory block is erased, it is programmed (to a logical “0”)

on a word-by-word basis. Programming is accomplished via the internal device command reg-

ister and is a four-bus cycle operation. The device will automatically generate the required

internal program pulses.

Any commands written to the chip during the embedded programming cycle will be ignored. If

a hardware reset happens during programming, the data at the location being programmed

will be corrupted. Please note that a data “0” cannot be programmed back to a “1”; only erase

operations can convert “0”s to “1”s. Programming is completed after the specified tBP cycle

time. The Data Polling feature or the Toggle Bit feature may be used to indicate the end of a

program cycle. If the erase/program status bit is a “1”, the device was not able to verify that the

erase or program operation was performed successfully.

5

5 Page

AT52BC3221A(T)

www.DataSheet4U.com

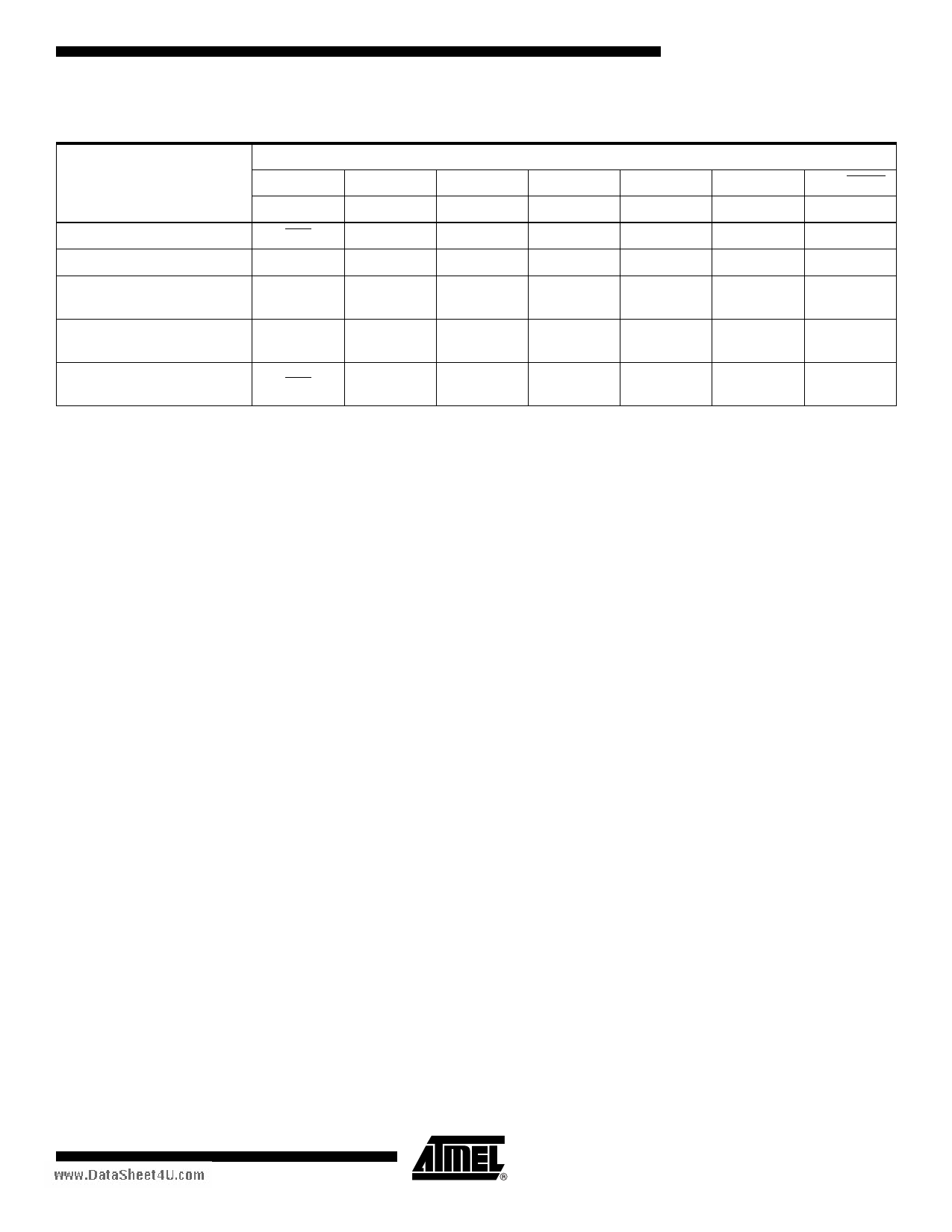

Status Bit Table

Status Bit

I/O7

I/O7

I/O6

I/O5(1)

I/O3(2)

I/O2 RDY/BUSY

Configuration Register

00

01

00/01

00/01

00/01

00/01

00/01

Programming

I/O7 0 TOGGLE 0 0 1 0

Erasing

0 0 TOGGLE 0 0 TOGGLE 0

Erase Suspended & Read

Erasing Sector

1

1

1

0

0 TOGGLE 1

Erase Suspended & Read

Non-erasing Sector

DATA

DATA

DATA

DATA

DATA

DATA

1

Erase Suspended &

Program Non-erasing Sector

I/O7

0 TOGGLE 0

0 TOGGLE 0

Notes: 1. I/O5 switches to a “1” when a program or an erase operation has exceeded the maximum time limits or when a program or

sector erase operation is performed on a protected sector.

2. I/O3 switches to a “1” when the VPP level is not high enough to successfully perform program and erase operations.

3466A–STKD–11/04

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT52BC3221AT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT52BC3221A | 32-Mbit Flash 8-Mbit PSRAM Stack Memory | ATMEL Corporation |

| AT52BC3221AT | 32-Mbit Flash 8-Mbit PSRAM Stack Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |