|

|

PDF AD6549 Data sheet ( Hoja de datos )

| Número de pieza | AD6549 | |

| Descripción | (AD6548 / AD6549) Single Chip GSM Radio | |

| Fabricantes | MediaTek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD6549 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

GSM850/900/1800/1900

Single Chip GSM Radio

AD6548/9

FEATURES

Fully Integrated GSM Transceiver including

Direct Conversion Receiver

4 Differential LNAs

Integrated Active RX Channel Select Filters

Programmable Gain Baseband Amplifiers

Translation Loop Direct VCO Modulator

Integrated TX VCO and tank

External TX filters eliminated

Integrated Loop filter components

High performance multi band PLL system

Fast Fractional-N Synthesizer

Integrated Local Oscillator VCO

Fully Integrated Loop filters

Crystal Reference Oscillator & Tuning System (AD6548)

Power Management

Integrated LDOs allow direct battery supply connection

Small footprint

32-Lead 5 X 5 mm Chipscale Package

APPLICATIONS

Dual, Triple and Quad Band Radios

- GSM850, E-GSM 900, DCS1800 and PCS1900

- GPRS to Class 12- EDGE RX

VCC_FE 1

I2

IB 3

VCC_BBI 4

SDATA 5

SCLK 6

SEN 7

NC 8

AD6548/9

LFCSP-32

(5X5 mm)

24 VCC_BBQ

23 Q

22 QB

21 REF_OP

20 REFIN

19 REFINB

18 VAFC

1273 VCC_REF

GENERAL DESCRIPTION

The AD6548/9 provides a highly integrated direct conversion

radio solution that combines, on a single chip, all radio and

power management functions necessary to build the most com-

pact GSM radio solution possible. The only external components

required for a complete radio design are the Rx SAWs, PA,

Switchplexer and a few passives enabling an extremely small

cost effective GSM Radio solution.

The AD6548/9 uses the industry proven direct conversion re-

ceiver architecture of the OthelloTM family. For Quad band appli-

cations the front end features four fully integrated programmable

gain differential LNAs. The RF is then downconverted by quad-

rature mixers and then fed to the baseband programmable-gain

amplifiers and active filters for channel selection. The Receiver

output pins can be directly connected to the baseband analog

processor. The Receive path features automatic calibration and

tracking to remove DC offsets.

The transmitter features a translation-loop architecture for di-

rectly modulating baseband signals onto the integrated TX VCO.

The translation-loop modulator and TX VCO are extremely low

noise removing the need for external SAW filters prior to the PA.

The AD6548/9 uses a single integrated LO VCO for both the

receive and the transmit circuits. The synthesizer lock times are

optimized for GPRS applications up to and including class 12.

To dramatically reduce the BOM both TX Translational loop and

main PLL Loop Filters are fully integrated into the device.

www.DataSheet.co.kr

AD6548 incorporates a complete reference crystal calibration

system. This allows the external VCTCXO to be replaced with a

low cost crystal. No other external components are required. The

AD6549 uses the traditional VCTCXO reference source.

The AD6548/9 also contains on-chip low dropout voltage regula-

tors (LDOs) to deliver regulated supply voltages to the functions

on chip, with a battery input voltage of between 2.9V and 5.5V.

Comprehensive power down options are included to minimize

power consumption in normal use.

A standard 3 wire serial interface is used to program the IC. The

interface features low-voltage digital interface buffers compatible

with logic levels from 1.6V to 3.0V.

The AD6548/9 is packaged in a 5mm× 5mm , 32-lead LFCSP

package.

ORDERING GUIDE

Model

Temperature

Package

Range

AD6548BCPZ -20°C to +85°C

LFCSP-32

AD6549BCPZ -20°C to +85°C

LFCSP-32

Rev B (1st October 2007)

Information furnished by MediaTek is believed to be accurate and reliable.

However, no responsibility is assumed by MediaTek for its use, nor for any

infringements of patents or other rights of third parties that may result from

its use. No license is granted by implication or otherwise under any patent or

patent rights of MediaTek. Trademarks and registered trademarks are the

property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.mediatek.com

Fax: 781/326-8703

© 2008 MediaTek, Inc. All rights reserved.

Datasheet pdf - http://www.DataSheet4U.net/

1 page

at each of the baseband outputs via internal series resistor along

with an external shunt capacitor. The external capacitor is not

normally required with ADI baseband ICs. The on chip filter

has an auto calibration feature ensuring that the filters are tuned

for optimum performance.

The baseband amplifiers have programmable gain for system

AGC. A total of 57 dB of gain control is provided in 3dB steps

programmable over the serial interface. This together with the

LNA gain control gives a total of 77dB of gain control range.

The receive baseband outputs are routed to the common Rx/Tx

I/Q ports for connection with the baseband converters.

Gain Control

Gain[4:0]

I

Optional

Q

Automatic Tuning

Control

Ref

AD6548/9

Figure 3 Baseband Amplifiers

Baseband Output D.C. Offset Correction

In order to minimize D.C. offsets inherent in the receiver and

maximize dynamic range a D.C offset correction circuit is inte-

grated. This correction is triggered over the serial bus and then

an offset tracking loop is enabled to minimize residual offsets

under all conditions. The tracking loop is fully hardware inte-

grated, requiring no software intervention.

Receiver Local Oscillator (LO) Generator

The Rx LO generator is used to avoid DC offset problems as-

sociated with LO leakage into the receiver RF path. By operat-

ing the VCO at a frequency other than the desired receive fre-

quencies, any leakage of the VCO will fall out of band. The LO

generator is used to convert the offset synthesized VCO output

to the on-frequency quadrature LO required by the chipset. The

LO generator is implemented as a regenerative frequency di-

vider, performing a 2/3 multiplication of the VCO output for

the high band (DCS1800/PCS1900) and a 1/3 multiplication for

low band (E-GSM 900/GSM850).

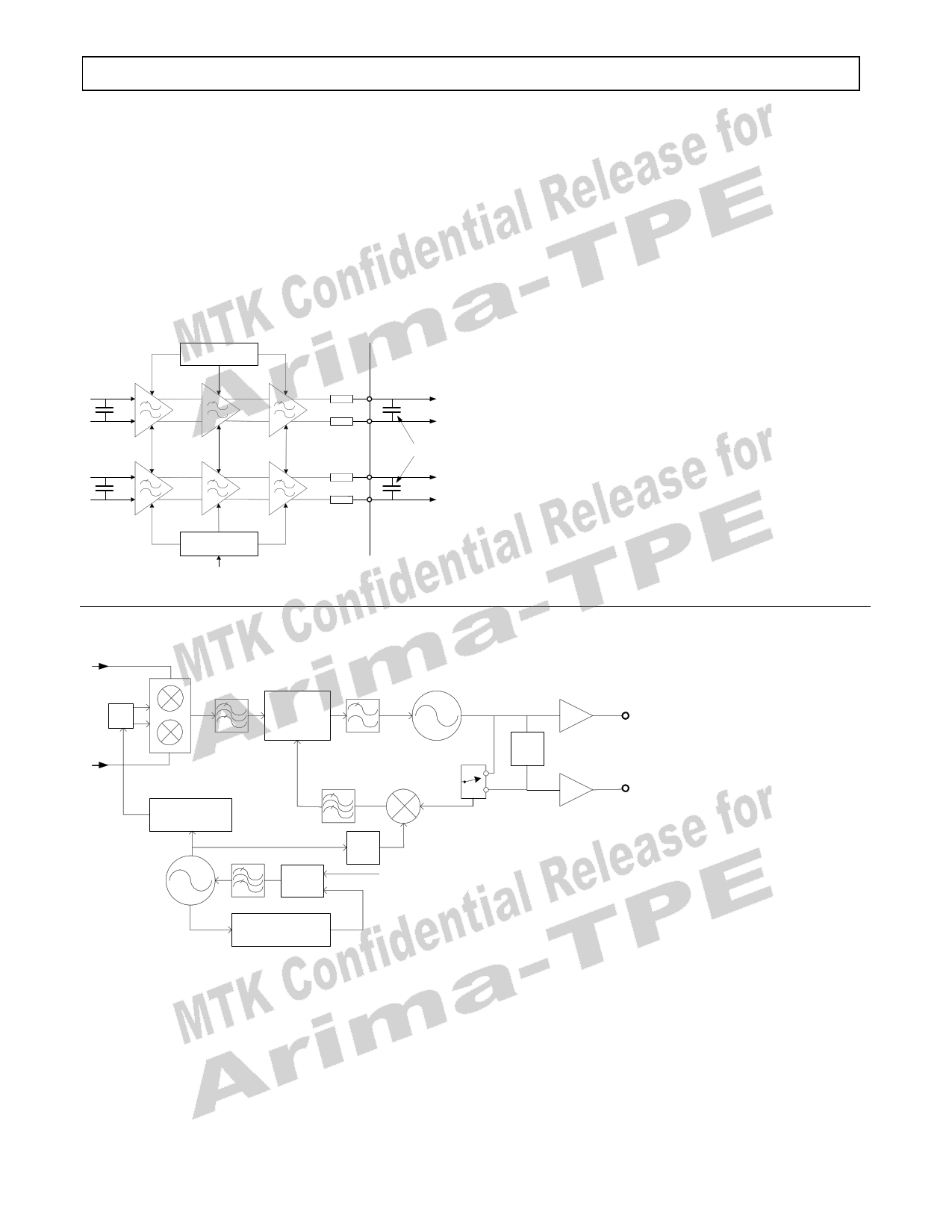

Transmitter

www.DataSheet.co.kr

I

/4

Q

Phase Frequency

Detector

Loop Filter

PFD

TX VCO

1648-1910 MHz

Feedback Down

converting Mixer

/2

1800/1900 MHz Tx

Regenerative

divider 5/7

Band select

switch

850/900 MHz Tx

/2

Main VCO

2520-2985 MHz

PFD

Fractional-n

Synthesizer

26 MHz

Reference

Figure 4 Transmit Path

Overview

The transmit section of the AD6548/9 radio implements a

translation loop modulator. This consists of a quadrature modu-

lator, high speed phase-frequency detector (PFD) with charge

pump output, loop filter, TX VCO and a feedback down con-

verting mixer. The VCO output (divided by 2 for low band) is

fed to the power amplifier with a portion internally fed back

into the down-converting feedback mixer to close the feedback

loop.

Product characteristics and specifications are subject to change without notice. MediaTek assumes no obligation regarding future manufacture unless otherwise agreed to in

writing. No responsibility is assumed by MediaTek for its use; nor for any infringements of patents or other rights of third parties, which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of MediaTek.

Rev B

-5- MediaTek Proprietary Information

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

AD6548/9

AD6548

Power

Control

Serial

Bus

H

VCC_REF

L

Register Name

SEN

Power

Control

(Addr4)

Register

Bits

H

LDO_EN

L

H

LOVCO_LDO_EN

L

LOVCO_COREPU

SYN_PU

TX_ON

PA control signals

External

Control

Signals

I/Q signal

FEM signals

Ramp

Power PLL

Control Divider

Power

Control

200us

100us

dummy

Active TX Burst

I

mA

120

110

Wait Mode Alert Mode

100

90

80

70

60

50

40 External Components

30

20

VCXO

Buffer

10

www.DataSheet.co.kr

FEM

Transmit Mode

Transmitter + TX VCO

Synthesizer + LO VCO

VCXO

time

Figure 10 Typical timing of the power up sequence prior to the TX burst and the resulting current consumption

Note:

This timing diagram assumes a preceding RX burst as shown in figure 9, where the LDOs are not disabled. This is acceptable for traffic

mode.

Product characteristics and specifications are subject to change without notice. MediaTek assumes no obligation regarding future manufacture unless otherwise agreed to in

writing. No responsibility is assumed by MediaTek for its use; nor for any infringements of patents or other rights of third parties, which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of MediaTek.

Rev B

-11- MediaTek Proprietary Information

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet AD6549.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD654 | Low Cost Monolithic Voltage-to-Frequency Converter | Analog Devices |

| AD6548 | (AD6548 / AD6549) Single Chip GSM Radio | MediaTek |

| AD6549 | (AD6548 / AD6549) Single Chip GSM Radio | MediaTek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |