|

|

PDF N25Q064A Data sheet ( Hoja de datos )

| Número de pieza | N25Q064A | |

| Descripción | NOR Flash Memory | |

| Fabricantes | Micron | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de N25Q064A (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

64Mb, 3V, Multiple I/O Serial Flash Memory

Features

Micron Serial NOR Flash Memory

3V, Multiple I/O, 4KB Sector Erase

N25Q064A

Features

• SPI-compatible serial bus interface

• 108 MHz (MAX) clock frequency

• 2.7–3.6V single supply voltage

• Dual/quad I/O instruction provides increased

throughput up to 432 MHz

• Supported protocols

– Extended SPI, dual I/O, and quad I/O

• Execute-in-place (XIP) mode for all three protocols

– Configurable via volatile or nonvolatile registers

– Enables memory to work in XIP mode directly af-

ter power-on

• PROGRAM/ERASE SUSPEND operations

• Continuous read of entire memory via a single com-

mand

– Fast read

– Quad or dual output fast read

– Quad or dual I/O fast read

• Flexible to fit application

– Configurable number of dummy cycles

– Output buffer configurable

• 64-byte, user-lockable, one-time programmable

(OTP) dedicated area

• Erase capability

– Subsector erase 4KB uniform granularity blocks

– Sector erase 64KB uniform granularity blocks

– Full-chip erase

• Write protection

– Software write protection applicable to every

64KB sector via volatile lock bit

– Hardware write protection: protected area size

defined by five nonvolatile bits (BP0, BP1, BP2,

BP3, and TB)

– Additional smart protections, available upon re-

quest

• Electronic signature

– JEDEC-standard 2-byte signature (BA17h)

– Unique ID code (UID): 17 read-only bytes, in-

cluding:

• Two additional extended device ID (EDID)

bytes to identify device factory options

• Customized factory data (14 bytes)

• Minimum 100,000 ERASE cycles per sector

• More than 20 years data retention

• Packages JEDEC standard, all RoHS compliant

– F6 = V-PDFN-8 6mm x 5mm (MLP8 6mm x 5mm)

– F8 = V-PDFN-8 8mm x 6mm (MLP8 8mm x 6mm)

– 12 = T-PBGA-24b05 6mm x 8mm

– 14 = T-PBGA-24b05 6mm x 8mm, 4x6 ball array

– SF = SOP2-16 300 mils body width (SO16W)

– SE = SOP2-8 208 mils body width (SO8W)

PDF: 09005aef845665f4

n25q_64mb_3v_65nm.pdf - Rev. K 08/13 EN

1 Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

Free Datasheet http://www.datasheet4u.com/

1 page

64Mb, 3V, Multiple I/O Serial Flash Memory

Features

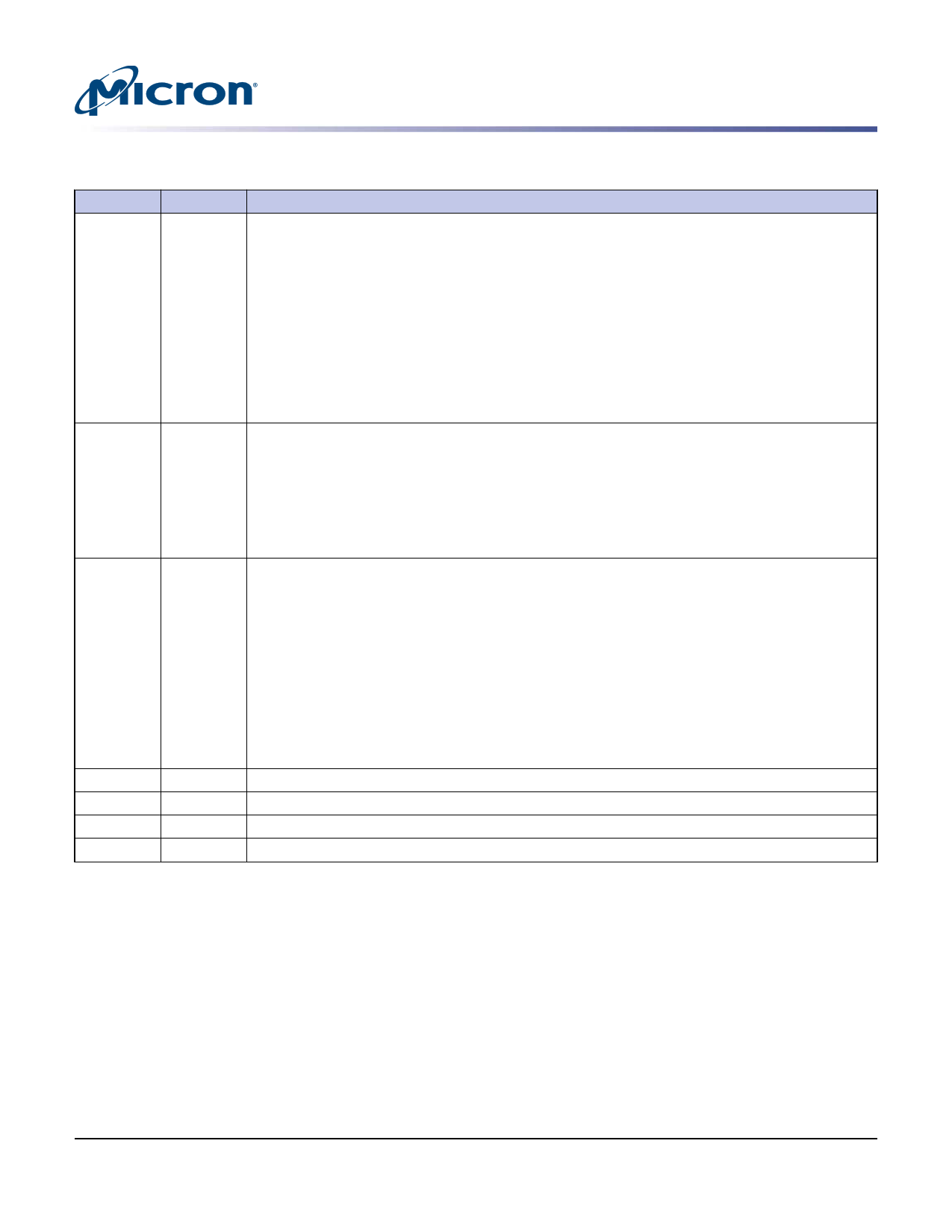

List of Tables

Table 1: Signal Descriptions ........................................................................................................................... 10

Table 2: Sectors[127:0] ................................................................................................................................... 13

Table 3: Data Protection using Device Protocols ............................................................................................. 14

Table 4: Memory Sector Protection Truth Table .............................................................................................. 14

Table 5: Protected Area Sizes – Upper Area ..................................................................................................... 14

Table 6: Protected Area Sizes – Lower Area ...................................................................................................... 15

Table 7: SPI Modes ........................................................................................................................................ 16

Table 8: Extended, Dual, and Quad SPI Protocols ............................................................................................ 19

Table 9: Status Register Bit Definitions ........................................................................................................... 21

Table 10: Nonvolatile Configuration Register Bit Definitions ........................................................................... 22

Table 11: Volatile Configuration Register Bit Definitions .................................................................................. 23

Table 12: Sequence of Bytes During Wrap ....................................................................................................... 24

Table 13: Supported Clock Frequencies .......................................................................................................... 24

Table 14: Enhanced Volatile Configuration Register Bit Definitions .................................................................. 24

Table 15: Flag Status Register Bit Definitions .................................................................................................. 25

Table 16: Command Set ................................................................................................................................. 27

Table 17: Lock Register .................................................................................................................................. 32

Table 18: Data/Address Lines for READ ID and MULTIPLE I/O READ ID Commands ....................................... 35

Table 19: Read ID Data Out ............................................................................................................................ 35

Table 20: Extended Device ID, First Byte ......................................................................................................... 35

Table 21: Serial Flash Discovery Parameter – Header Structure ........................................................................ 37

Table 22: Parameter ID .................................................................................................................................. 37

Table 23: Command/Address/Data Lines for READ MEMORY Commands ....................................................... 39

Table 24: Data/Address Lines for PROGRAM Commands ................................................................................ 43

Table 25: Suspend Parameters ....................................................................................................................... 53

Table 26: Operations Allowed/Disallowed During Device States ...................................................................... 54

Table 27: OTP Control Byte (Byte 64) .............................................................................................................. 56

Table 28: XIP Confirmation Bit ....................................................................................................................... 59

Table 29: Effects of Running XIP in Different Protocols .................................................................................... 59

Table 30: Power-Up Timing and VWI Threshold ............................................................................................... 62

Table 31: AC RESET Conditions ...................................................................................................................... 63

Table 32: Absolute Ratings ............................................................................................................................. 67

Table 33: Operating Conditions ...................................................................................................................... 67

Table 34: Input/Output Capacitance .............................................................................................................. 67

Table 35: AC Timing Input/Output Conditions ............................................................................................... 68

Table 36: DC Current Characteristics and Operating Conditions ...................................................................... 69

Table 37: DC Voltage Characteristics and Operating Conditions ...................................................................... 69

Table 38: AC Characteristics and Operating Conditions ................................................................................... 70

Table 39: Part Number Information ................................................................................................................ 78

Table 40: Package Details ............................................................................................................................... 79

PDF: 09005aef845665f4

n25q_64mb_3v_65nm.pdf - Rev. K 08/13 EN

5 Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

5 Page

64Mb, 3V, Multiple I/O Serial Flash Memory

Signal Descriptions

Table 1: Signal Descriptions (Continued)

Symbol

HOLD#

W#

VPP

VCC

VSS

DNU

NC

Type

Control

Input

Control

Input

Power

Power

Ground

–

–

Description

HOLD: Pauses any serial communications with the device without deselecting the device. DQ1

(output) is High-Z. DQ0 (input) and the clock are "Don't Care." To enable HOLD, the device

must be selected with S# driven LOW.

HOLD# is used for input/output during the following operations: QUAD OUTPUT FAST READ,

QUAD INPUT/OUTPUT FAST READ, QUAD INPUT FAST PROGRAM, and QUAD INPUT EXTENDED

FAST PROGRAM.

In QIO-SPI, HOLD# acts as an I/O (DQ3 functionality), and the HOLD# functionality is disabled

when the device is selected. When the device is deselected (S# is HIGH) in parts with RESET#

functionality, it is possible to reset the device unless this functionality is not disabled by means

of dedicated registers bits.

The HOLD# functionality can be disabled using bit 4 of the NVCR or bit 4 of the VECR.

Write protect: W# can be used as a protection control input or in QIO-SPI operations. When in

extended SPI with single or dual commands, the WRITE PROTECT function is selectable by the

voltage range applied to the signal. If voltage range is low (0V to VCC), the signal acts as a

write protection control input. The memory size protected against PROGRAM or ERASE opera-

tions is locked as specified in the status register block protect bits 3:0.

W# is used as an input/output (DQ2 functionality) during QUAD INPUT FAST READ and QUAD

INPUT/OUTPUT FAST READ operations and in QIO-SPI.

Supply voltage: If VPP is in the voltage range of VPPH, the signal acts as an additional power

supply, as defined in the AC Measurement Conditions table.

During QIFP, QIEFP, and QIO-SPI PROGRAM/ERASE operations, it is possible to use the addition-

al VPP power supply to speed up internal operations. However, to enable this functionality, it is

necessary to set bit 3 of the VECR to 0.

In this case, VPP is used as an I/O until the end of the operation. After the last input data is shif-

ted in, the application should apply VPP voltage to VPP within 200ms to speed up the internal

operations. If the VPP voltage is not applied within 200ms, the PROGRAM/ERASE operations

start at standard speed.

The default value of VECR bit 3 is 1, and the VPP functionality for quad I/O modify operations is

disabled.

Device core power supply: Source voltage.

Ground: Reference for the VCC supply voltage.

Do not use.

No connect.

PDF: 09005aef845665f4

n25q_64mb_3v_65nm.pdf - Rev. K 08/13 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet N25Q064A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| N25Q064A | NOR Flash Memory | Micron |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |