|

|

PDF AT25SF041 Data sheet ( Hoja de datos )

| Número de pieza | AT25SF041 | |

| Descripción | 2.5V Minimum SPI Serial Flash Memory | |

| Fabricantes | Adesto | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT25SF041 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

AT25SF041

4-Mbit, 2.5V Minimum

SPI Serial Flash Memory with Dual-I/O and Quad-I/O Support

Features

Single 2.5V - 3.6V Supply

Serial Peripheral Interface (SPI) Compatible

Supports SPI Modes 0 and 3

Supports Dual and Quad Output Read

104MHz Maximum Operating Frequency

Clock-to-Output (tV) of 6 ns

Flexible, Optimized Erase Architecture for Code + Data Storage Applications

Uniform 4-Kbyte Block Erase

Uniform 32-Kbyte Block Erase

Uniform 64-Kbyte Block Erase

Full Chip Erase

Hardware Controlled Locking of Protected Blocks via WP Pin

3 Protected Programmable Security Register Pages

Flexible Programming

Byte/Page Program (1 to 256 Bytes)

Fast Program and Erase Times

0.7ms Typical Page Program (256 Bytes) Time

70ms Typical 4-Kbyte Block Erase Time

300ms Typical 32-Kbyte Block Erase Time

600ms Typical 64-Kbyte Block Erase Time

JEDEC Standard Manufacturer and Device ID Read Methodology

Low Power Dissipation

2µA Deep Power-Down Current (Typical)

10µA Standby current (Typical)

4mA Active Read Current (Typical)

Endurance: 100,000 Program/Erase Cycles

Data Retention: 20 Years

Complies with Full Industrial Temperature Range

Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options

8-lead SOIC (150-mil and 208-mil)

8-pad Ultra Thin DFN (5 x 6 x 0.6 mm and 2 x 3 x 0.6 mm)

8-lead TSSOP (4 x 4 mm)

Die in Wafer Form

DS-25SF041–044F–4/2016

1 page

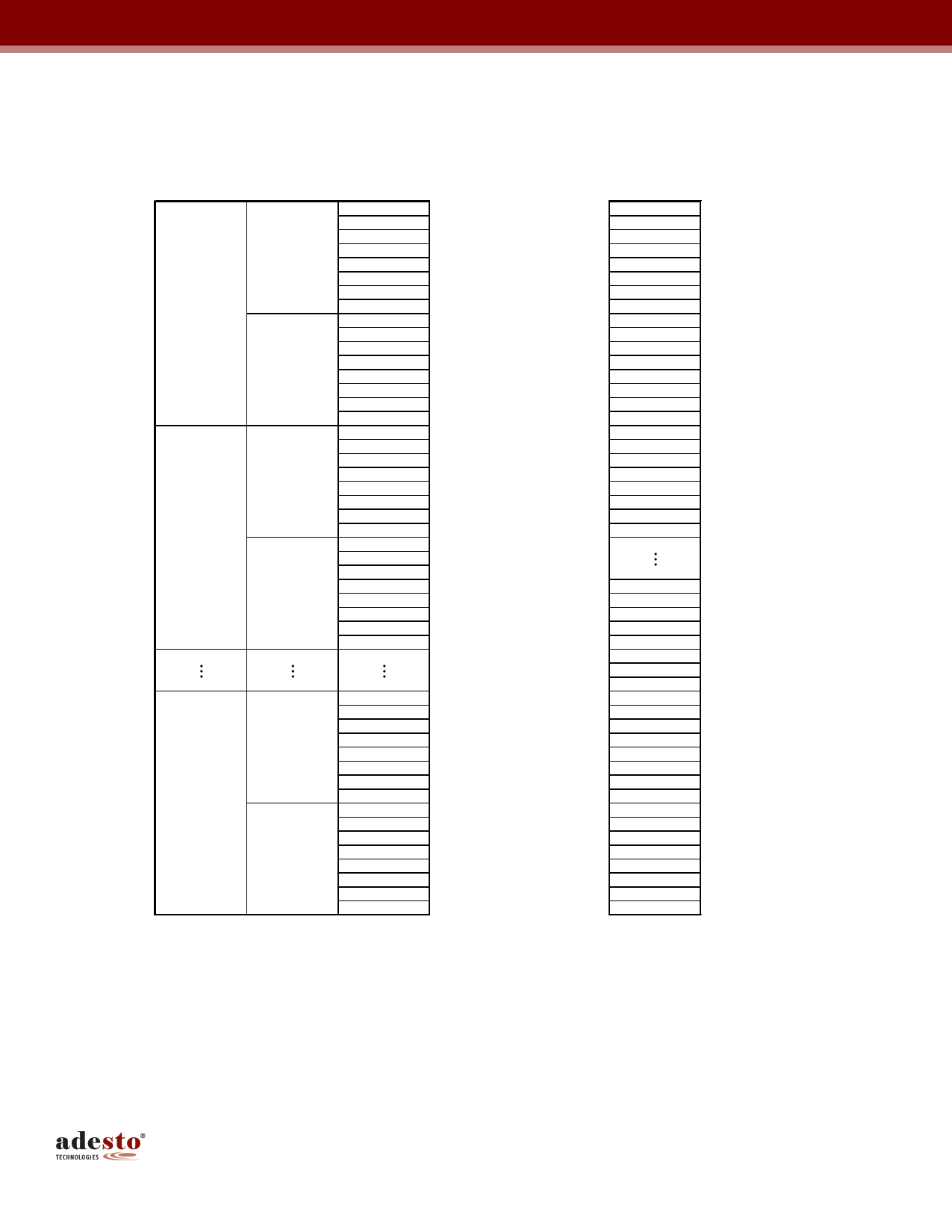

Figure 3-1. Memory Architecture Diagram

Block Erase Detail

64KB

32KB

4KB

Block Erase

Block Erase

Block Erase

(D8h Command) (52h Command) (20h Command)

64KB

Sector 7

32KB

32KB

64KB

Sector 6

32KB

32KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

4KB

Block Address

Range

07FFFFh

07EFFFh

07DF F F h

0 7 CF F F h

07BFFFh

07AF F F h

079FFFh

078FFFh

077FFFh

076FFFh

075FFFh

074FFFh

073FFFh

072FFFh

071FFFh

070FFFh

06FFFFh

06EFFFh

06DF F F h

0 6 CF F F h

06BFFFh

06AF F F h

069FFFh

068FFFh

067FFFh

066FFFh

065FFFh

064FFFh

063FFFh

062FFFh

061FFFh

060FFFh

– 07F000h

– 07E000h

– 07D000h

– 07C000h

– 07B000h

– 07A000h

– 079000h

– 078000h

– 077000h

– 076000h

– 075000h

– 074000h

– 073000h

– 072000h

– 071000h

– 070000h

– 06F000h

– 06E000h

– 06D000h

– 06C000h

– 06B000h

– 06A000h

– 069000h

– 068000h

– 067000h

– 066000h

– 065000h

– 064000h

– 063000h

– 062000h

– 061000h

– 060000h

64KB

Sector 0

32KB

32KB

4KB 00F F F F h – 00F 000h

4KB 00E F F F h – 00E 000h

4KB 00DF F F h – 00D000h

4KB 00CF F F h – 00C000h

4KB 00BF F F h – 00B000h

4KB 00AF F F h – 00A000h

4KB 009F F F h – 009000h

4KB 008F F F h – 008000h

4KB 007F F F h – 007000h

4KB 006F F F h – 006000h

4KB 005F F F h – 005000h

4KB 004F F F h – 004000h

4KB 003F F F h – 003000h

4KB 002F F F h – 002000h

4KB 001F F F h – 001000h

4KB 000F F F h – 000000h

Page Program Detail

1-256 Byte

Page Program

(02h Command)

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

Page Address

Range

07FFFFh

07FEFFh

07F DF F h

0 7 F CF F h

07FBFFh

07F AF F h

07F9FFh

07F8FFh

07F7FFh

07F6FFh

07F5FFh

07F4FFh

07F3FFh

07F2FFh

07F1FFh

07F0FFh

07EFFFh

07EEFFh

07E DF F h

0 7 E CF F h

07EBFFh

07E AF F h

07E9FFh

07E8FFh

– 07FF00h

– 07FE00h

– 07F D00h

– 07FC00h

– 07FB00h

– 07F A00h

– 07F900h

– 07F800h

– 07F700h

– 07F600h

– 07F500h

– 07F400h

– 07F300h

– 07F200h

– 07F100h

– 07F000h

– 07EF00h

– 07EE00h

– 07E D00h

– 07EC00h

– 07EB00h

– 07E A00h

– 07E900h

– 07E800h

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

0017FFh

0016FFh

0015FFh

0014FFh

0013FFh

0012FFh

0011FFh

0010FFh

000FFFh

000EFFh

000DF F h

0 0 0 CF F h

000BFFh

000AF F h

0009FFh

0008FFh

0007FFh

0006FFh

0005FFh

0004FFh

0003FFh

0002FFh

0001FFh

0000FFh

– 001700h

– 001600h

– 001500h

– 001400h

– 001300h

– 001200h

– 001100h

– 001000h

– 000F00h

– 000E00h

– 000D00h

– 000C00h

– 000B00h

– 000A00h

– 000900h

– 000800h

– 000700h

– 000600h

– 000500h

– 000400h

– 000300h

– 000200h

– 000100h

– 000000h

AT25SF041

DS-25SF041–044F–4/2016

5

5 Page

Figure 6-5. Dual-I/O Read Array (Previous command set M5, M4 = 1,0)

CS

SCK

I/O0

(SI)

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21

Address Bits

A23-A16

Address Bits

A15-A8

A7-A0

M7-M0

Byte 1

Byte 2

A22 A20 A18 A16 A14 A

MSB

A0 M6 M4 M2 M0 D6 D4 D2 D0 D6

I/O1

(SO)

A23 A21 A19 A17 A15 A

MSB

A1 M7 M5 M3 M1 D7 D5 D3 D1 D7

6.4 Quad-Output Read Array (6Bh)

The Quad-Output Read Array command is similar to the Dual-Output Read Array command. The Quad-Output Read

Array command allows four bits of data to be clocked out of the device on every clock cycle, rather than just one or two.

The Quad Enable bit (QE) of the Status Register must be set to enable for the Quad-Output Read Array instruction.

The Quad-Output Read Array command can be used at any clock frequency, up to the maximum specified by fRDQO. To

perform the Quad-Output Read Array operation, the CS pin must first be asserted and then the opcode 6Bh must be

clocked into the device. After the opcode has been clocked in, the three address bytes must be clocked in to specify the

location of the first byte to read within the memory array. Following the three address bytes, a single dummy byte must

also be clocked into the device.

After the three address bytes and the dummy byte have been clocked in, additional clock cycles will result in data being

output on the I/O3-0 pins. The data is always output with the MSB of a byte first and the MSB is always output on the I/O3

pin. During the first clock cycle, bit 7 of the first data byte will be output on the I/O3 pin while bits 6, 5, and 4 of the same

data byte will be output on the I/O2, I/O1, and I/O0 pins, respectively. During the next clock cycle, bits 3, 2, 1, and 0 of the

first data byte will be output on the I/O3, I/O2, I/O1 and I/O0 pins, respectively.

The sequence continues with each byte of data being output after every two clock cycles. When the last byte (07FFFFh)

of the memory array has been read, the device will continue reading from the beginning of the array (000000h). No

delays will be incurred when wrapping around from the end of the array to the beginning of the array.Deasserting the CS

pin will terminate the read operation and put the WP, HOLD, SO, SI pins into a high-impedance state. The CS pin can be

deasserted at any time and does not require that a full byte of data be read.

AT25SF041

DS-25SF041–044F–4/2016

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT25SF041.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT25SF041 | 2.5V Minimum SPI Serial Flash Memory | Adesto |

| AT25SF041-MAHD-T | 2.5V Minimum SPI Serial Flash Memory | Adesto |

| AT25SF041-MHD-T | 2.5V Minimum SPI Serial Flash Memory | Adesto |

| AT25SF041-SHD-B | 2.5V Minimum SPI Serial Flash Memory | Adesto |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |