|

|

PDF MT29F16G16ADBCA Data sheet ( Hoja de datos )

| Número de pieza | MT29F16G16ADBCA | |

| Descripción | NAND Flash Memory | |

| Fabricantes | Micron | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MT29F16G16ADBCA (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Micron Confidential and Proprietary

8Gb,16Gb: x8, x16 NAND Flash Memory

Features

NAND Flash Memory

MT29F8G08ABACA, MT29F8G16ABACA, MT29F8G08ABBCA,

MT29F8G16ABBCA, MT29F16G08ADACA, MT29F16G16ADACA,

MT29F16G08ADBCA , MT29F16G16ADBCA

Features

• Open NAND Flash Interface (ONFI) 1.0-compliant1

• Single-level cell (SLC) technology

• Organization

– Page size x8: 4320 bytes (4096 + 224 bytes)

– Page size x16: 2160 words (2048 + 112 words)

– Block size: 64 pages (256K + 14K bytes)

– Plane size: 2 planes x 2048 blocks per plane

– Device size: 8Gb: 4096 blocks

– Device size: 16Gb: 8192 blocks

• Asynchronous I/O performance

– tRC/tWC: 20ns (3.3V), 30ns (1.8V)

• Array performance

– Read page: 25µs

– Program page: 200µs (TYP)

– Erase block: 2ms (TYP)

• Command set: ONFI NAND Flash Protocol

• Advanced command set

– Program page cache mode

– Read page cache mode

– One-time programmable (OTP) mode

– Block lock (1.8V only)

– Programmable drive strength

– Two-plane commands

– Multi-die (LUN) operations

– Read unique ID

– Internal data move

• Operation status byte provides software method for

detecting

– Operation completion

– Pass/fail condition

– Write-protect status

• Ready/Busy# (R/B#) signal provides a hardware

method of detecting operation completion

• WP# signal: Write protect entire device

• First block (block address 00h) is valid when ship-

ped from factory with ECC. For minimum required

ECC, see Error Management.

• RESET (FFh) required as first command after

power-on

• Alternative method of device initialization after

power-up (contact factory)

• Internal data move operations supported within the

plane from which data is read

• Quality and reliability

– Data retention: JESD47G-compliant; see qualifi-

cation report

– Endurance: See qualification report

• Operating voltage range

– VCC: 2.7–3.6V

– VCC: 1.7–1.95V

• Operating temperature

– Commercial: 0°C to +70°C

– Industrial (IT): –40ºC to +85ºC

• Package

– 48-pin TSOP type 1, CPL2

– 63-ball VFBGA

Notes: 1. The ONFI 1.0 specification is available at

www.onfi.org.

2. CPL = Center parting line

PDF: 09005aef83ea4f61

m71m_8Gb_nand.pdf – Rev. L 1/12 EN

1 Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

1 page

Micron Confidential and Proprietary

8Gb,16Gb: x8, x16 NAND Flash Memory

Features

List of Figures

Figure 1: Marketing Part Number Chart ............................................................................................................ 2

Figure 2: 48-Pin TSOP – Type 1, CPL (Top View) ................................................................................................ 9

Figure 3: 63-Ball VFBGA, x8 (Balls Down, Top View) ........................................................................................ 10

Figure 4: 63-Ball VFBGA, x16 (Balls Down, Top View) ...................................................................................... 11

Figure 5: 48-Pin TSOP – Type 1, CPL ............................................................................................................... 12

Figure 6: 63-Ball VFBGA ................................................................................................................................ 13

Figure 7: NAND Flash Die (LUN) Functional Block Diagram ............................................................................ 14

Figure 8: Array Organization – 8Gb x 8 ............................................................................................................ 15

Figure 9: Array Organization – 8Gb x 16 .......................................................................................................... 16

Figure 10: Array Organization – 16Gb x 8, Dual-Die, Single-CE# Bare Die Configuration ................................... 17

Figure 11: Array Organization – 16Gb x 16, Dual-Die, Single-CE# Bare Die Configuration ................................. 18

Figure 12: Asynchronous Command Latch Cycle ............................................................................................ 20

Figure 13: Asynchronous Address Latch Cycle ................................................................................................ 21

Figure 14: Asynchronous Data Input Cycles .................................................................................................... 22

Figure 15: Asynchronous Data Output Cycles ................................................................................................. 23

Figure 16: Asynchronous Data Output Cycles (EDO Mode) ............................................................................. 24

Figure 17: READ/BUSY# Open Drain .............................................................................................................. 25

Figure 18: tFall and tRise (3.3V VCC) ................................................................................................................ 26

Figure 19: tFall and tRise (1.8V VCC) ................................................................................................................ 26

Figure 20: IOL vs. Rp (VCC = 3.3V VCC) .............................................................................................................. 27

Figure 21: IOL vs. Rp (1.8V VCC) ....................................................................................................................... 27

Figure 22: TC vs. Rp ....................................................................................................................................... 28

Figure 23: R/B# Power-On Behavior ............................................................................................................... 29

Figure 24: RESET (FFh) Operation .................................................................................................................. 34

Figure 25: READ ID (90h) with 00h Address Operation .................................................................................... 35

Figure 26: READ ID (90h) with 20h Address Operation .................................................................................... 35

Figure 27: READ PARAMETER (ECh) Operation .............................................................................................. 38

Figure 28: READ UNIQUE ID (EDh) Operation ............................................................................................... 44

Figure 29: SET FEATURES (EFh) Operation .................................................................................................... 46

Figure 30: GET FEATURES (EEh) Operation .................................................................................................... 46

Figure 31: READ STATUS (70h) Operation ...................................................................................................... 50

Figure 32: READ STATUS ENHANCED (78h) Operation ................................................................................... 50

Figure 33: RANDOM DATA READ (05h-E0h) Operation ................................................................................... 51

Figure 34: RANDOM DATA READ TWO-PLANE (06h-E0h) Operation .............................................................. 52

Figure 35: RANDOM DATA INPUT (85h) Operation ........................................................................................ 53

Figure 36: PROGRAM FOR INTERNAL DATA INPUT (85h) Operation .............................................................. 55

Figure 37: READ PAGE (00h-30h) Operation ................................................................................................... 59

Figure 38: READ PAGE CACHE SEQUENTIAL (31h) Operation ......................................................................... 60

Figure 39: READ PAGE CACHE RANDOM (00h-31h) Operation ....................................................................... 61

Figure 40: READ PAGE CACHE LAST (3Fh) Operation ..................................................................................... 62

Figure 41: READ PAGE TWO-PLANE (00h-00h-30h) Operation ........................................................................ 64

Figure 42: PROGRAM PAGE (80h-10h) Operation ............................................................................................ 66

Figure 43: PROGRAM PAGE CACHE (80h–15h) Operation (Start) ..................................................................... 68

Figure 44: PROGRAM PAGE CACHE (80h–15h) Operation (End) ...................................................................... 68

Figure 45: PROGRAM PAGE TWO-PLANE (80h–11h) Operation ....................................................................... 70

Figure 46: ERASE BLOCK (60h-D0h) Operation .............................................................................................. 71

Figure 47: ERASE BLOCK TWO-PLANE (60h–D1h) Operation .......................................................................... 72

Figure 48: READ FOR INTERNAL DATA MOVE (00h-35h) Operation ................................................................ 74

Figure 49: READ FOR INTERNAL DATA MOVE (00h–35h) with RANDOM DATA READ (05h–E0h) ..................... 74

Figure 50: PROGRAM FOR INTERNAL DATA MOVE (85h–10h) Operation ........................................................ 75

PDF: 09005aef83ea4f61

m71m_8Gb_nand.pdf – Rev. L 1/12 EN

5 Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

5 Page

Micron Confidential and Proprietary

8Gb,16Gb: x8, x16 NAND Flash Memory

Signal Assignments

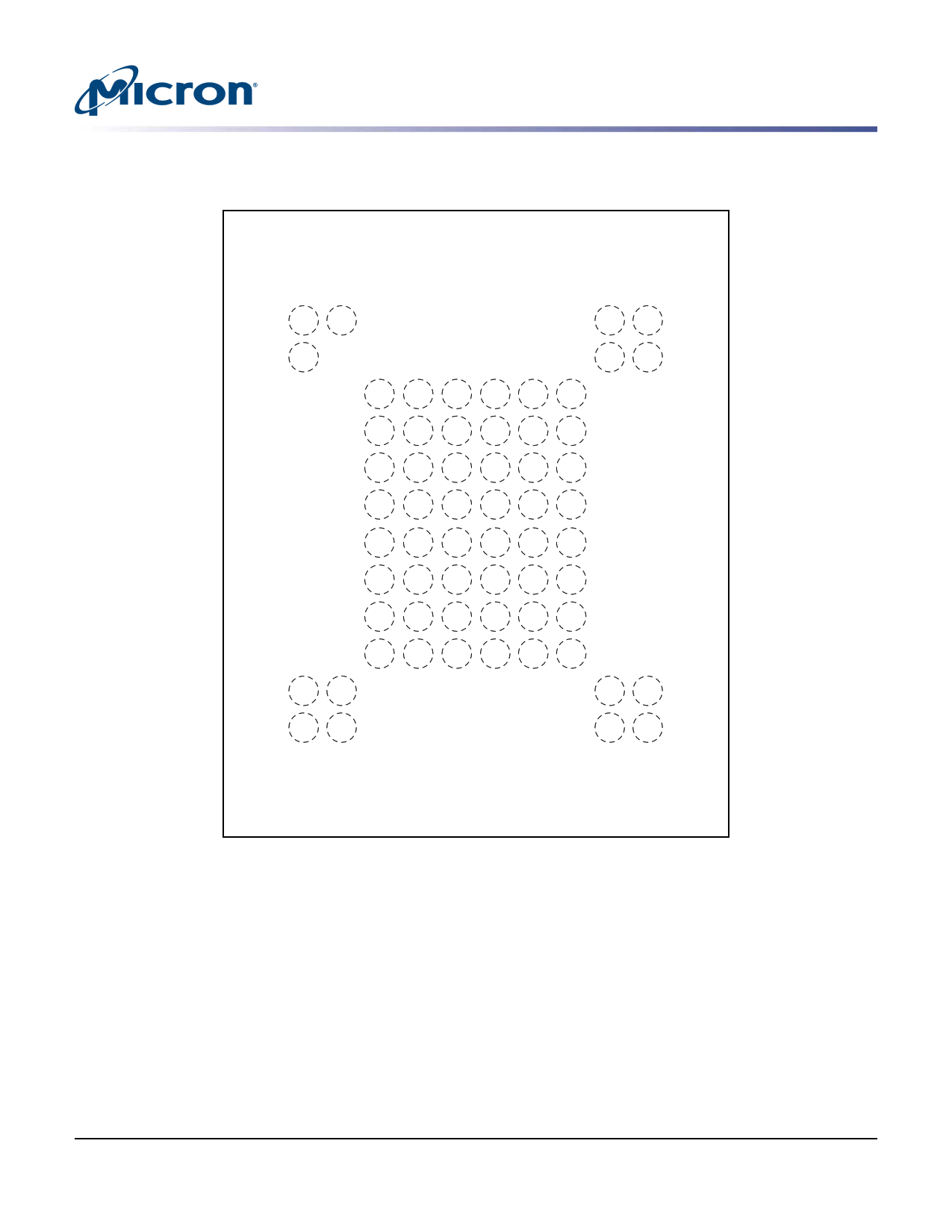

Figure 4: 63-Ball VFBGA, x16 (Balls Down, Top View)

1 2 3 4 5 6 7 8 9 10

A NC NC

NC NC

B NC

NC NC

C WP# ALE Vss CE# WE# R/B#

D Vcc RE# CLE NC NC NC

E NC NC NC NC NC NC

F NC NC NC NC Vss NC

G DNU Vcc LOCK1 I/O13 I/O15 DNU

H I/O8 I/O0 I/O10 I/O12 I/O14 Vcc

J I/O9 I/O1 I/O11 Vcc I/O5 I/O7

K Vss I/O2 I/O3 I/O4 I/O6 Vss

L NC NC

NC NC

M NC NC

NC NC

Note: 1. For the 3V device, G5 changes to DNU. NO LOCK function is available on the 3.3V de-

vice.

PDF: 09005aef83ea4f61

m71m_8Gb_nand.pdf – Rev. L 1/12 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet MT29F16G16ADBCA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MT29F16G16ADBCA | NAND Flash Memory | Micron |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |