|

|

PDF ISL6455IRZ Data sheet ( Hoja de datos )

| Número de pieza | ISL6455IRZ | |

| Descripción | Triple Output Regulator | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6455IRZ (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

®

Data Sheet

ISL6455, ISL6455A

December 21, 2005

FN9196.0

Triple Output Regulator with Single

Synchronous Buck and Dual LDO

The ISL6455 is a highly integrated triple output regulator

which provides a single chip solution for FPGAs and wireless

chipset power management. The device integrates a high

efficiency synchronous buck regulator (adjustable) with two

ultra low noise LDO regulators (adjustable). Either the

ISL6455 or ISL6455A can be selected based on whether

3.3V ±10% or 5V ±10% is required as an input voltage.

The synchronous current mode control PWM regulator with

integrated N- and P-channel power MOSFET provides

adjustable voltages based on external resistor setting.

Synchronous rectification with internal MOSFETs is used to

achieve higher efficiency and reduced number of external

components. Operating frequency is typically 750kHz

allowing the use of smaller inductor and capacitor values.

The device can be synchronized to an external clock signal

in the range of 500kHz to 1MHz. The PG_PWM output

indicates loss of regulation on PWM output.

The ISL6455 also has two LDO adjustable regulators using

internal PMOS transistors as pass devices. LDO2 features

ultra low noise typically below 30µVRMS to aid VCO stability.

The EN_LDO pin controls LDO1 and LDO2 outputs. The

ISL6455 also integrates a RESET function, which eliminates

the need for additional RESET IC required in WLAN and

other applications. The IC asserts a RESET signal whenever

the VIN supply voltage drops below a preset threshold,

keeping it asserted for at least 25ms after VIN has risen

above the reset threshold. The PG_LDO output indicates

loss of regulation on either of the two LDO outputs. Other

features include overcurrent protection and thermal

shutdown for all the three outputs.

High integration and the thin Quad Flat No-lead (QFN)

package makes ISL6455 an ideal choice for powering

FPGAs and small form factor wireless cards such as

PCMCIA, mini-PCI and Cardbus-32.

Ordering Information

PART NUMBER* PART

TEMP. PACKAGE PKG.

(Note)

MARKING RANGE (°C) (Pb-Free) DWG. #

ISL6455IRZ

6455IRZ

-40 to 85 24 Ld QFN L24.4x4B

ISL6455AIRZ 6455AIRZ -40 to 85 24 Ld QFN L24.4x4B

Add “-TK” or T5K suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

Features

• Fully integrated synchronous buck regulator + dual LDO

• PWM output voltage adjustable.

- 0.8V to 2.5V with ISL6455 (VIN = 3.3V)

- 0.8V to 3.3V with ISL6455A (VIN = 5.0V)

• High output current. . . . . . . . . . . . . . . . . . . . . . . . . 600mA

• Dual LDO adjustable options

- LDO1, 1.2V to Vin-0.3V (3.3Vmax). . . . . . . . . . . 300mA

- LDO2, 1.2V to Vin-0.3V (3.3Vmax). . . . . . . . . . . 300mA

• Ultra-compact DC/DC converter design

• Stable with small ceramic output capacitors and no load

• High conversion efficiency

• Low shutdown supply current

• Low dropout voltage for LDOs

- LDO1 . . . . . . . . . . . . . . . . . . 150mV (typical) at 300mA

- LDO2 . . . . . . . . . . . . . . . . . . 150mV (typical) at 300mA

• Low output voltage noise

- <30µVRMS (typical) for LDO2 (VCO supply)

• PG_LDO and PG_PWM (PWM and LDO) outputs

• Extensive circuit protection and monitoring features

- PWM overvoltage protection

- Overcurrent protection

- Shutdown

- Thermal shutdown

• Integrated RESET output for microprocessor reset

• Proven reference design for total WLAN system solution

• QFN package

- Compliant to JEDEC PUB95 MO-220 QFN - Quad Flat

No Leads - Product Outline

- Near Chip-Scale package footprint Improves PCB

efficiency and is thinner in Profile

• Pb-free plus anneal available (RoHS compliant)

Applications

• WLAN cards

- PCMCIA, Cardbus32, MiniPCI cards

- Compact flash cards

• Hand-held instruments

Related Literature

• TB363 - Guidelines for Handling and Processing Moisture

Sensitive Surface Mount Devices (SMDs)

• TB389 - PCB Land Pattern Design and Surface Mount

Guidelines for QFN Packages

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6455, ISL6455A

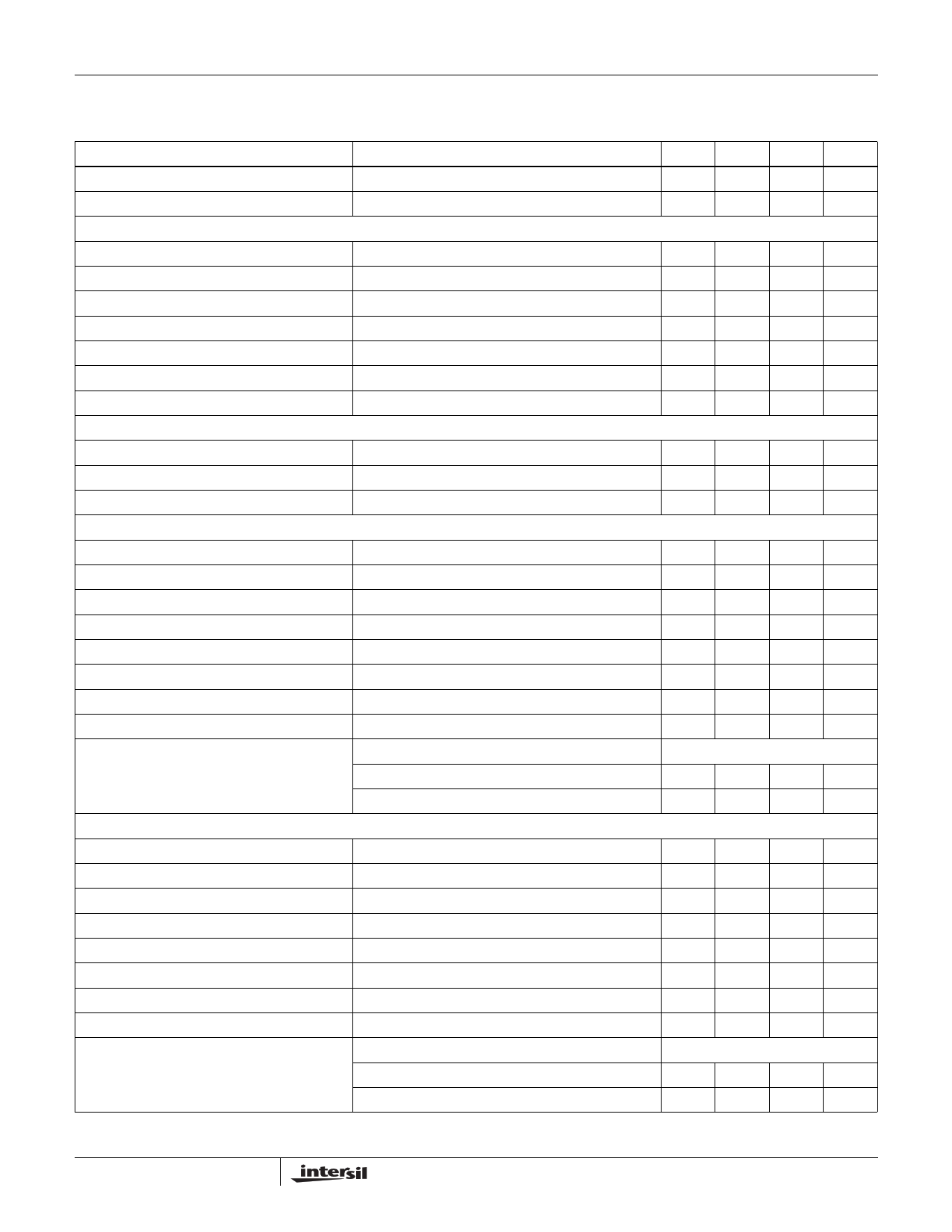

Electrical Specifications

PARAMETER

Recommended operating conditions unless otherwise noted. VIN = VIN_LDO = PVCC = 3.3V for ISL6455 and

5.0V for the ISL6455A, Compensation Capacitors = 33nF for LDO1 and LDO2. TA = -40°C to 85° (Note 2), typical

values are at TA = 25°C. (Continued)

TEST CONDITIONS

MIN TYP MAX UNITS

Efficiency

Soft-Start Time

IOUT = 200mA, VIN = 3.3V, VOUT = 1.8V

4096 Clock Cycles @ 750kHz

- 93 - %

- 5.5 - ms

OSCILLATOR

Oscillator Frequency

TA = -40°C to +85°C

Frequency Synchronization Range (fSYNC)

Clock signal on SYNC pin

SYNC High Level Input Voltage

As % of VIN

SYNC Low Level Input Voltage

As % of VIN

Sync Input Leakage Current

SYNC = GND or VIN

Min Duty Cycle of External Clock Signal (Note 6)

620 750 880 kHz

500 - 1000 kHz

70 -

-%

- - 30 %

-1.0 - 1.0 µA

- 20 - %

Max Duty Cycle of External Clock Signal (Note 6)

- 80 - %

PG_PWM

Rising Threshold

Falling Threshold

Leakage Current

LDO1 SPECIFICATIONS

1.2mA source/sink, FB_PWM vs 0.45V VREF

FB_PWM vs 0.45V VREF

PG_PWM = GND or VIN

+5.5

-10.5

-

8.0

-8.0

0.01

+10.5

-5.5

0.1

%

%

µA

Output Voltage Range

VIN_VLDO > 3.0V

1.2 - 2.7 V

Output Voltage Range

VIN_VLDO > 3.6V

1.2 - 3.3 V

FB_LDO1 Voltage Accuracy (Note 7)

Maximum Output Current (Note 6)

Output Current Limit (Note 6)

IOUT = 10mA

VIN = 3.6V

-1.5 - 1.5 %

300 -

- mA

350 420 600 mA

Dropout Voltage (Note 4)

FB_LDO1 Line Regulation

FB_LDO1 Load Regulation

Output Voltage Noise (Note 6)

LDO2 SPECIFICATIONS

IOUT = 300mA

IOUT = 10mA, VIN_LDO = 3.0-5.5V

IOUT = 10mA to 300mA

10Hz < f < 100kHz, IOUT = 10mA

COUT = 2.2µF

COUT = 10µF

- 150 300 mV

-0.5 - 0.5 %/V

-0.5 - 0.5 %

- 65 - µVRMS

- 60 - µVRMS

Output Voltage Range

VIN_VLDO > 3.0V

1.2 - 2.7 V

Output Voltage Range

VIN_VLDO > 3.6V

1.2 - 3.3 V

FB_LDO2 Voltage Accuracy (Note 7)

Maximum Output Current (Note 6)

Output Current Limit (Note 6)

IOUT = 10mA

VIN = 3.6V

-1.5 - 1.5 %

300 -

- mA

350 420 600 mA

Dropout Voltage (Note 4)

FB_LDO2 Line Regulation

FB_LDO2 Load Regulation

Output Voltage Noise (Note 6)

IOUT = 300mA

IOUT = 10mA, VIN_LDO = 3.0-5.5V

IOUT = 10mA to 300mA

10Hz < f < 100kHz, IOUT = 10mA

COUT = 2.2µF

COUT = 10µF

- 150 300 mV

-0.5 - 0.5 %/V

-0.5 - 0.5 %

- 30 - µVRMS

- 20 - µVRMS

5 FN9196.0

December 21, 2005

5 Page

ISL6455, ISL6455A

the inductor. The DC resistance of the inductor will influence

directly the efficiency of the converter. Therefore, an inductor

with lowest DC resistance should be selected for highest

efficiency.

In order to avoid saturation of the inductor, the inductor

should be rated at least for the maximum output current plus

the inductor ripple current.

TABLE 1. RECOMMENDED INDUCTORS

OUTPUT INDUCTOR

CURRENT VALUE

VENDOR PART #

COMMENTS

600mA

8.2µH Coilcraft

MSS6122-822MX

ISL6455

600mA

12µH

Coilcraft

MSS6122-123MX

ISL6455A

OUTPUT CAPACITOR SELECTION

For the best performance, a low ESR output capacitor is

needed. If an output capacitor is selected with an ESR value

≤120mΩ, its RMS ripple current rating will always meet the

application requirements. The RMS ripple current is

calculated as:

IRMS(C)O

=

VO

×

-1---L-–----×-V---V----f--O---I--

×

-------1---------

2× 3

The overall output ripple voltage is the sum of the voltage

spike caused by the output capacitor ESR plus the voltage

ripple caused by charge and discharging the output

capacitor:

∆VO

=

VO

×

-1---L-–----×-V---V----f--O---I--

×

8-----×-----C--1---O-----×-----f

+

E S R

Where the highest output voltage ripple occurs at the highest

input voltage.

TABLE 2. RECOMMENDED CAPACITORS

CAPACITOR

VALUE

ESR/mΩ

VENDOR PART # COMMENTS

10µF

<50 TDK

Ceramic

C2012X5R0J106M

INPUT CAPACITOR SELECTION

Because of the nature of the buck converter having a

pulsating input current, a low ESR input capacitor is required

for best input voltage filtering and minimizing the

interference with other circuits caused by high input voltage

spikes.

The input capacitor should have a minimum value of 10µF

and can be increased without any limit for better input

voltage filtering. The input capacitor should be rated for the

maximum input ripple current calculated as:

IRMS = IO(max) ×

V--V---O-I-

×

1

–

V--V---O-I-

The worst case RMS ripple current occurs at D = 0.5.

Ceramic capacitors show good performance because of

their low ESR value, and because they are less sensitive to

voltage transients, compared to tantalum capacitors.

Place the input capacitor as close as possible to the input pin

of the IC for best performance.

Output Voltage Setting

The equations for the Output voltages are given below:

VOUT = 0---R-.--4--f-5--(Re + Rf)

VOUT1 = 1----.R-1----b8---4-- (Ra + Rb)

VOUT2 = 1----.R-1----d8---4-- (Rc + Rd)

The output resistors should be selected so that the minimum

output load is about 200µA.

Layout Considerations

As for all switching power supplies, the layout is an important

step in the design of ISL6455, ISL6455A based power

supply due to the high switching frequency and low noise

LDO implementations.

Allocate two board levels as ground planes, with many vias

between them to create a low impedance, high-frequency

plane. Tie all the device ground pins through multiple vias

each to this ground plane, as close to the device as possible.

Also tie the exposed pad on the bottom of the device to this

ground plane.

Use wide and short traces for the high current paths. The

input capacitor should be placed as close as possible to the

IC pins as well as the inductor and output capacitor. Use a

common ground node to minimize the effects of ground

noise.

11 FN9196.0

December 21, 2005

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ISL6455IRZ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6455IRZ | Triple Output Regulator | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |