|

|

PDF ispPAC-POWR1014 Data sheet ( Hoja de datos )

| Número de pieza | ispPAC-POWR1014 | |

| Descripción | In-System Programmable Power Supply Supervisor / Reset Generator and Sequencing Controller | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ispPAC-POWR1014 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ispPAC-® POWR1014/A

In-System Programmable Power Supply Supervisor,

Reset Generator and Sequencing Controller

March 2015

Data Sheet DS1014

Features

Monitor and Control Multiple Power Supplies

• Simultaneously monitors up to 10 power

supplies

• Provides up to 14 output control signals

• Programmable digital and analog circuitry

Embedded PLD for Sequence Control

• 24-macrocell CPLD implements both state

machines and combinatorial logic functions

Embedded Programmable Timers

• Four independent timers

• 32µs to 2 second intervals for timing sequences

Analog Input Monitoring

• 10 independent analog monitor inputs

• Two programmable threshold comparators per

analog input

• Hardware window comparison

• 10-bit ADC for I2C monitoring (ispPAC-

POWR1014A only)

High-Voltage FET Drivers

• Power supply ramp up/down control

• Programmable current and voltage output

• Independently configurable for FET control or

digital output

2-Wire (I2C/SMBus™ Compatible) Interface

• Comparator status monitor

• ADC readout

• Direct control of inputs and outputs

• Power sequence control

• Only available with ispPAC-POWR1014A

3.3 V Operation, Wide Supply Range 2.8 V

to 3.96 V

• Industrial temperature range: –40°C to +85°C

• 48-pin TQFP package, lead-free option

Multi-Function JTAG Interface

• In-system programming

• Access to all I2C registers

• Direct input control

Application Block Diagram

Primary

Supply

3.3 V

Primary

Supply

Primary

Supply

2.5 V

1.8 V

Primary

Supply

POL#1

Primary

Supply

POL#N

Other Control/Supervisory

Signals

12 Digital

Outputs

2 MOSFET

Drivers

ADC*

4 Timers

ispPAC-POWR1014A

*ispPAC-POWR1014A only.

CPLD

24 Macrocells

53 Inputs

4 Digital

Inputs

I2C

Interface

I2C

Bus*

CPU

Description

Lattice’s Power Manager II ispPAC-POWR1014/A is a

general-purpose power-supply monitor and sequence

controller, incorporating both in-system programmable

logic and in-system programmable analog functions

implemented in non-volatile E2CMOS® technology. The

ispPAC-POWR1014/A device provides 10 independent

analog input channels to monitor up to 10 power supply

test points. Each of these input channels has two inde-

pendently programmable comparators to support both

high/low and in-bounds/out-of-bounds (window-com-

pare) monitor functions. Four general-purpose digital

inputs are also provided for miscellaneous control func-

tions.

The ispPAC-POWR1014/A provides 14 open-drain digi-

tal outputs that can be used for controlling DC-DC con-

verters, low-drop-out regulators (LDOs) and opto-

couplers, as well as for supervisory and general-pur-

pose logic interface functions. Two of these outputs

(HVOUT1-HVOUT2) may be configured as high-voltage

© 2015 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other

brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without

notice.

www.latticesemi.com

1

DS1014_2.1

1 page

ispPAC-POWR1014/A Data Sheet

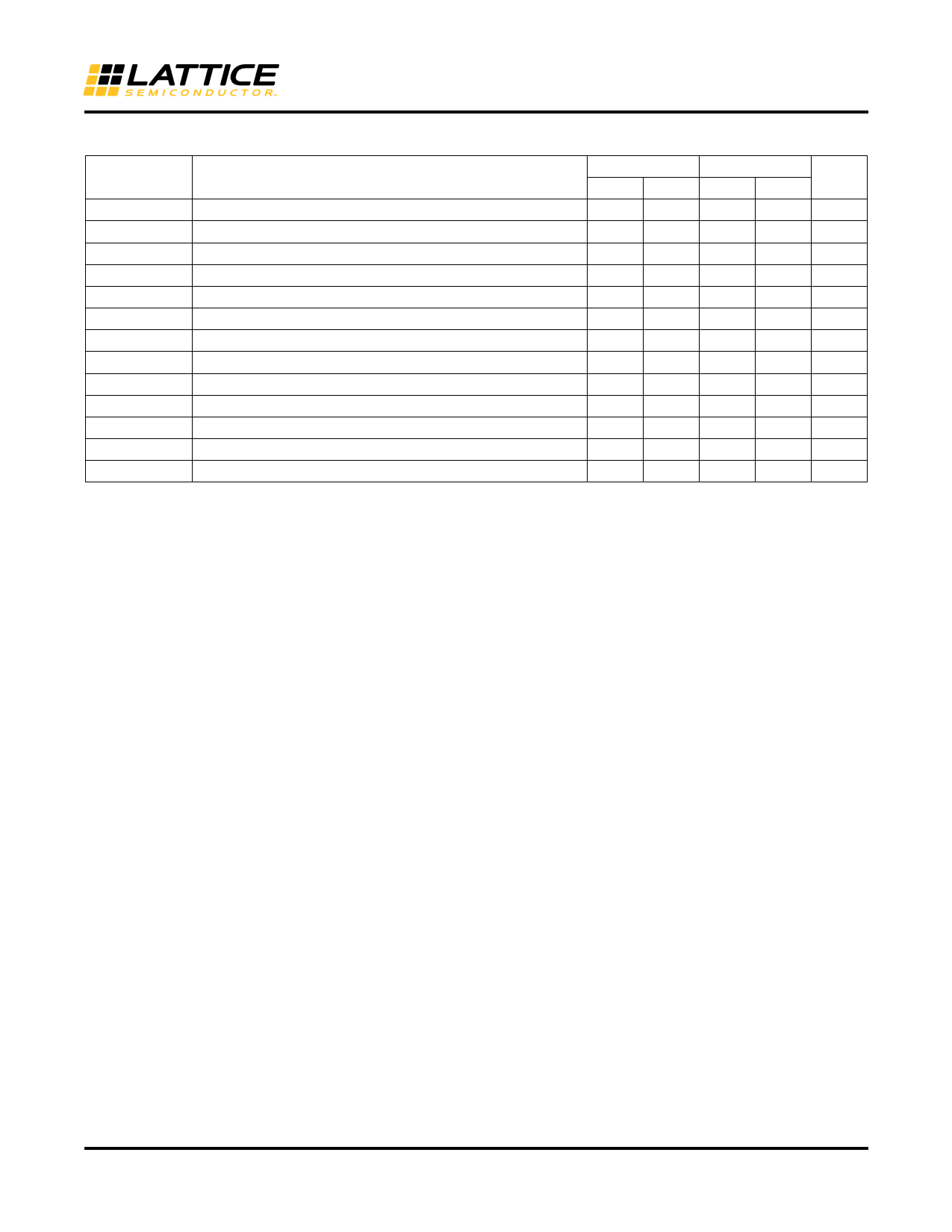

Absolute Maximum Ratings

Absolute maximum ratings are shown in the table below. Stresses beyond those listed may cause permanent dam-

age to the device. Functional operation of the device at these or any other conditions beyond those indicated in the

recommended operating conditions of this specification is not implied.

Symbol

VCCD

VCCA

VCCINP

VCCJ

APS

VIN

VMON

VTRI

ISINKMAXTOTAL

TS

TA

Parameter

Core supply

Analog supply

Digital input supply (IN[1:4])

JTAG logic supply

Alternate E2 programming supply

Digital input voltage (all digital I/O pins)

VMON input voltage

Voltage applied to tri-stated pins

Maximum sink current on any output

Storage temperature

Ambient temperature

Conditions

HVOUT[1:2]

OUT[3:14]

Min.

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–65

–65

Max.

4.5

4.5

6

6

4

6

6

13.3

6

23

150

125

Units

V

V

V

V

V

V

V

V

V

mA

oC

oC

Recommended Operating Conditions

Symbol

VCCD, VCCA

VCCINP

VCCJ

APS

VIN

VMON

VOUT

TAPROG

TA

Parameter

Core supply voltage at pin

Digital input supply for IN[1:4] at pin

JTAG logic supply voltage at pin

Conditions

Alternate E2 programming supply at pin VCCD and VCCA powered

VCCD and VCCA not powered

Input voltage at digital input pins

Input voltage at VMON pins

Open-drain output voltage

OUT[3:14] pins

HVOUT[1:2] pins in open-drain

mode

Ambient temperature during

programming

Ambient temperature

Power applied

Min. Max.

2.8 3.96

2.25 5.5

2.25 3.6

No connect

Must be left floating

3.0 3.6

–0.3 5.5

–0.3 5.9

–0.3 5.5

–0.3 13.0

–40 85

–40 85

Units

V

V

V

V

V

V

V

V

V

oC

oC

ESD Performance

Pin Group

All pins

ESD Stress

HBM

CDM

Min.

2000

1000

Units

V

V

5

5 Page

ispPAC-POWR1014/A Data Sheet

I2C Port Characteristics1

100 kHZ

400 kHZ

Symbol

Definition

Min. Max. Min. Max. Units

FI2C I2C clock/data rate

1002

4002 kHz

TSU;STA

After start

4.7 0.6 µs

THD;STA

After start

4 0.6 µs

TSU;DAT

Data setup

250 100

ns

TSU;STO

Stop setup

4 0.6 µs

THD;DAT

Data hold; SCL= Vih_min = 2.1 V

0.3 3.45 0.3 0.9 µs

TLOW

Clock low period

4.7 10 1.3 10 µs

THIGH

Clock high period

4 0.6 µs

TF Fall time; 2.25 V to 0.65 V

300 300 ns

TR Rise time; 0.65 V to 2.25 V

1000

300 ns

TTIMEOUT

Detect clock low timeout

25 35 25 35 ms

TPOR

Device must be operational after power-on reset

500 500

ms

TBUF

Bus free time between stop and start condition

4.7 1.3 µs

1. Applies to ispPAC-POWR1014A only.

2. If FI2C is less than 50 kHz, then the ADC DONE status bit is not guaranteed to be set after a valid conversion request is completed. In this

case, waiting for the TCONVERT minimum time after a convert request is made is the only way to guarantee a valid conversion is ready for

readout. When FI2C is greater than 50 kHz, ADC conversion complete is ensured by waiting for the DONE status bit.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ispPAC-POWR1014.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ispPAC-POWR1014 | In-System Programmable Power Supply Supervisor / Reset Generator and Sequencing Controller | Lattice Semiconductor |

| ispPAC-POWR1014A | In-System Programmable Power Supply Supervisor / Reset Generator and Sequencing Controller | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |