|

|

PDF NB3W1900L Data sheet ( Hoja de datos )

| Número de pieza | NB3W1900L | |

| Descripción | 3.3V 100/133MHz Differential 1:19 HCSL-Compatible Push-Pull Clock ZDB/Fanout Buffer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3W1900L (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

NB3W1900L

3.3 V 100/133 MHz

Differential 1:19

HCSL-Compatible Push‐Pull

Clock ZDB/Fanout Buffer for

PCIe[

www.onsemi.com

Description

The NB3W1900L differential clock buffers are designed to work in

conjunction with a PCIe compliant source clock synthesizer to provide

point-to-point clocks to multiple agents. The device is capable of

distributing the reference clocks for Intel® QuickPath Interconnect

(Intel QPI), PCIe Gen1/Gen2/Gen3.The NB3W1900L internal PLL is

optimized to support 100 MHz and 133 MHz frequency operation.

The NB3W1900L is developed with the low-power NMOS Push-Pull

buffer type.

Features

• 19 Low Power Differential Clock Output Pairs @ 0.7 V

• Output-to-Output Skew Performance: < 85 ps

• Cycle-to-Cycle Jitter (PLL Mode): < 50ps

• Low Phase Jitter (Intel QPI, PCIe Gen 2/Gen 3 Phase Jitter

Compliant)

• Input-to-Output Delay Variation: < 50 ps

• Fixed-Feedback for Lowest Input-to-Output Delay Variation

• Spread Spectrum Compatible; Tracks Input Clock Spreading for Low

EMI

• 100 MHz and 133 MHz PLL Mode to Meet the Next Generation

PCIe Gen2 / Gen 3 and Intel QPI Phase Jitter

• Individual OE Control via SMBus

• Low-Power NMOS Push-Pull HCSL−Compatible Outputs

• PLL Configurable for PLL Mode or Bypass Mode

(Fanout Operation)

• SMBus Address Configurable to Allow Multiple Buffers in a Single

Control Network

• Programmable PLL Bandwidth

• Two Tri-level Addresses Selection (Nine SMBus Addresses)

• QFN 72-pin Package, 10 mm × 10 mm

• These are Pb-Free Devices

1 72

QFN72

MN SUFFIX

CASE 485DK

MARKING DIAGRAM

1

NB3W

1900L

AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

ORDERING INFORMATION

See detailed ordering and shipping information on page 19 of

this data sheet.

© Semiconductor Components Industries, LLC, 2016

July, 2016 − Rev. 1

1

Publication Order Number:

NB3W1900L/D

1 page

NB3W1900L

Table 7. NB3W1900L PIN DESCRIPTIONS (continued)

Pin Number

Pin Name

Type

Description

36

DIF6#

OUT 0.7 V differential complementary clock output

37

DIF7

OUT 0.7 V differential true clock output

38

DIF7#

OUT 0.7 V differential complementary clock output

39

GND

GND Ground pin

40

VDDIO

PWR Power supply for differential outputs

41

DIF8

OUT 0.7 V differential true clock output

42

DIF8#

OUT 0.7 V differential complementary clock output

43

DIF9

OUT 0.7 V differential true clock output

44

DIF9#

OUT 0.7 V differential complementary clock output

45

VDD

PWR Power supply nominal 3.3 V

46

GND

GND Ground pin

47

DIF10

OUT 0.7 V differential true clock output

48

DIF10#

OUT 0.7 V differential complementary clock output

49

DIF11

OUT 0.7 V differential true clock output

50

DIF11#

OUT 0.7 V differential complementary clock output

51

GND

GND Ground pin

52

VDDIO

PWR Power supply for differential outputs

53

DIF12

OUT 0.7 V differential true clock output

54

DIF12#

OUT 0.7 V differential complementary clock output

55

DIF13

OUT 0.7 V differential true clock output

56

DIF13#

OUT 0.7 V differential complementary clock output

57

VDDIO

PWR Power supply for differential outputs

58

GND

GND Ground pin

59

DIF14

OUT 0.7 V differential true clock output

60

DIF14#

OUT 0.7 V differential complementary clock output

61

DIF15

OUT 0.7 V differential true clock output

62

DIF15#

OUT 0.7 V differential complementary clock output

63

GND

GND Ground pin

64

VDD

PWR Power supply nominal 3.3 V

65

DIF16

OUT 0.7 V differential true clock output

66

DIF16#

OUT 0.7 V differential complementary clock output

67

DIF17

OUT 0.7 V differential true clock output

68

DIF17#

OUT 0.7 V differential complementary clock output

69

VDDIO

PWR Power supply for differential outputs

70

GND

GND Ground pin

71

DIF18

OUT 0.7 V differential true clock output

72

DIF18#

OUT 0.7 V differential complementary clock output

EP

Exposed Pad

Thermal The Exposed Pad (EP) on the QFN-72 package bottom is thermally connected to

the die for improved heat transfer out of package. The exposed pad must be

attached to a heat-sinking conduit. The pad is electrically connected to the die, and

must be electrically and thermally connected to GND on the PC board.

1. All VDD, VDDR, VDDIO,VDDA and GND pins must be externally connected to a power supply for proper operation.

www.onsemi.com

5

5 Page

NB3W1900L

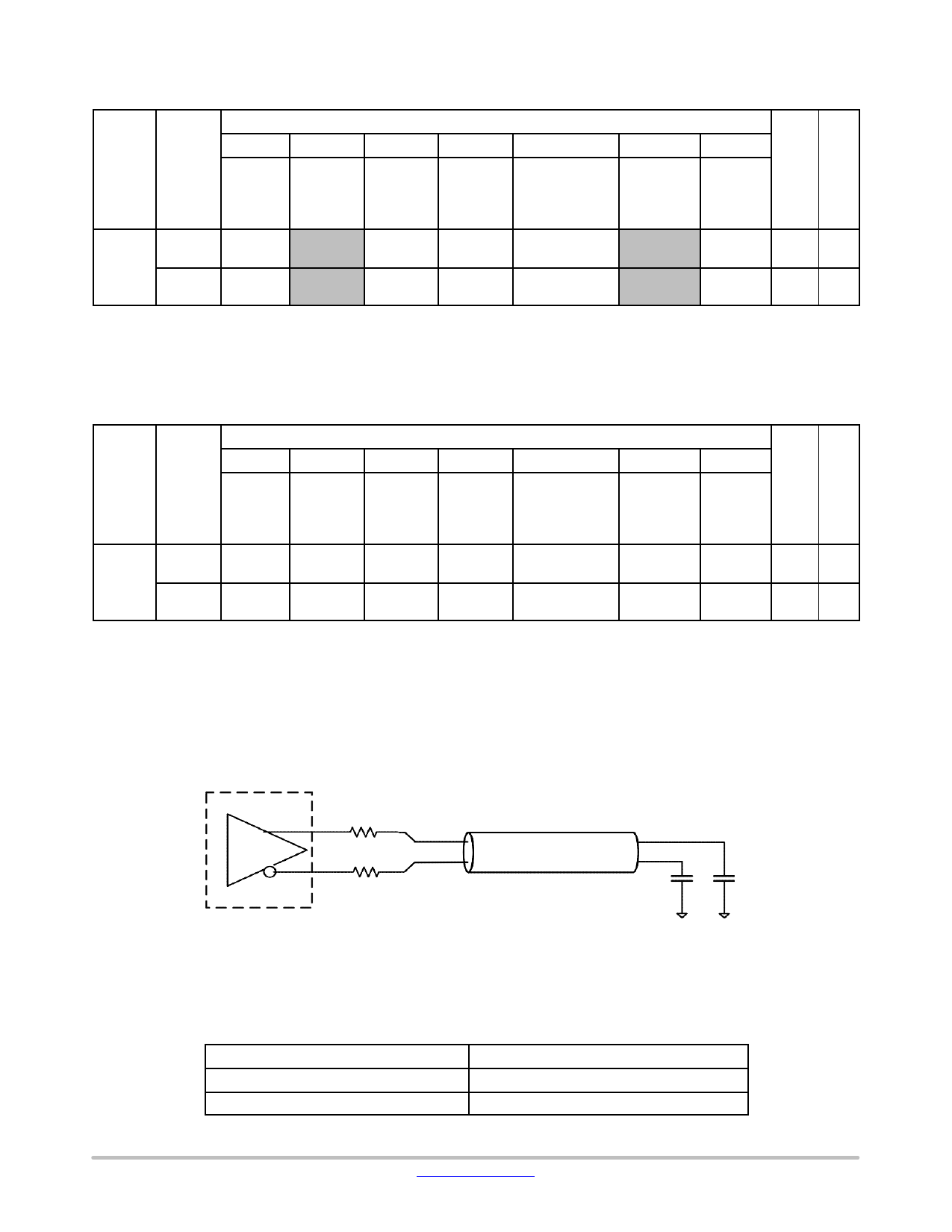

Table 15. CLOCK PERIODS-DIFFERENTIAL OUTPUTS WITH SPREAD SPECTRUM DISABLED

Measurement Window

1 Clock

1 ms

0.1 s

0.1s

0.1s

1 ms 1 Clock

−SSC

− ppm

−c 2c jitter Short−Term Long-Term

Center AbsPer Average Average

SSC OFF Freq. MHz Min

Min

Min

0 ppm

Period

Nominal

DIF 1 00.00 9.94900

9.99900 10 .0000 0

+ ppm Long−

Term Average

Max

1 0.001 00

+SSC +c2c jitter

Short−Term Abs Per

Average Max Max

10.05100

Unit Notes

ns 37,

38, 39

1 33.33 7.44925

7.49925 7.50000

7.50075

7.55 075

ns 37,

38, 40

37. Guaranteed by design and characterization, not tested in production.

38. All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ/CK410B+ accuracy

requirements (±100 ppm). The NB3W1900L it self does not contribute to ppm error.

39. Driven by SRC out put of main clock, 100.00 MHz PLL Mode or Bypass mode.

40. Driven by CPU out put of main clock, 133.33 MHz PLL Mode or Bypass mode.

Table 16. CLOCK PERIODS-DIFFERENTIAL OUTPUTS WITH SPREAD SPECTRUM ENABLED

Measurement Window

1 Clock

1 ms

0.1s

0.1s

0.1s

1 ms 1 Clock

−SSC

− ppm

−c2c jitter Short−Term Long-Term

Center AbsPer Average Average 0 ppm Peri-

SSC ON Freq. MHz Min

Min

Min od Nominal

+ ppm Long−

Term Average

Max

+SSC +c2c jitter

Short−Term AbsPer

Average Max Max

Unit Notes

DIF 99.75 9.94906 9. 99906 10.02406 10.02506 10.02607

10.05107

10.10107

ns 41,

42, 43

133.00 7.44930 7. 49930 7.51805 7.51880

7.51955

7.53830

7.58830

ns 41,

42, 44

41. Guaranteed by design and characterization, not tested in production.

42. All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ/ CK410B+ accuracy

requirements (±100 ppm). The NB3W1900L it self does not contribute to ppm error.

43. Driven by SRC out put of main clock, 100.00 MHz PLL Mode or Bypass mode.

44. Driven by CPU out put of main clock, 133.33 MHz PLL Mode or Bypass mode.

TEST LOADS

LP−HCSL

Differential

Output

Rs Differential Zo,

10 inches

Rs

Figure 3. NB3W1900L Differential Test Loads

Table 17. DIFFERENTIAL OUTPUT TERMINATIONS

DIF Zo (W)

100

85

Rs (W)

33

27

www.onsemi.com

11

2pF 2pF

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet NB3W1900L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3W1900L | 3.3V 100/133MHz Differential 1:19 HCSL-Compatible Push-Pull Clock ZDB/Fanout Buffer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |