|

|

PDF CY28551-3 Data sheet ( Hoja de datos )

| Número de pieza | CY28551-3 | |

| Descripción | Universal Clock Generator | |

| Fabricantes | Silicon Laboratories | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY28551-3 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

CY28551-3

Universal Clock Generator for Intel, VIA and SIS®

Features

• Compliant to Intel CK505

• Selectable CPU clock buffer type for Intel P4 or K8

selection

• Selectable CPU frequencies

• Universal clock to support Intel, SiS and VIA platform

• 0.7V Differential CPU clock for Intel CPU

• 3.3V Differential CPU clock for AMD K8

• 100-MHz differential SRC clocks

• 96-MHz differential dot clock

• 133-MHz Link clock

• 48-MHz USB clocks

• 33-MHz PCI clock

• Dynamic Frequency Control

• Dial-A-Frequency

• WatchDog Timer

• Two Independent Overclocking PLLs

• Low-voltage frequency select input

• I2C support with readback capabilities

• Ideal Lexmark Spread Spectrum profile for maximum

electromagnetic interference (EMI) reduction

• 3.3V power supply

• 56-pin QFN packages

CPU SRC SATA PCI REF LINK DOT96 24_48M 48M

x 2 x 6 x1 x 6 x 3 x2

x1

x1 x 1

Block Diagram

Xin 14.318-MHz

Xout Crystal

PLLReference

DOC[2:1]

FS[D:A]

SEL_P4_K8

SEL[1:0]

PLL1 Divider

CPU

PLL2 Divider

PCIEX

Multiplexer

Controller

PLL3 Divider

SATA

Pin Configuration

VDD_REF

REF[2:0]

VDD_CPU

CPUT[1:0]

CPUC[1:0]

VDD_PCIEX

PCIET[6:2]

PCIEC6:2]

VDD_SATA

PCIET0/SATAT

PCIEC0/SATAC

VDD_DOT

DOT96T/SATAT/LINK0

DOT96C/SATAC/LINK1

VDD_PCI

PCI[6:0]

56 55 54 53 52 51 50 49 48 47 46 45 44 43

*SEL0/ PCI5 1

42 Xout

VDD48 2

41 VDDREF

**SEL24_48/ 24_48M 3

40 SCLK

**SEL1/48M 4

39 SDATA

VSS48 5

38 VTTPWRG#/PD

VDDDOT 6

37 CPUT0

LINK0/DOT96T/SATAT 7

LINK1/DOT96C/SATAC 8

CY28551-3

36 CPUC0

35 VDDCPU

VSSDOT 9

34 CPUT1

VDDSATA 10

33 CPUC1

SATAT/PCIEXT0 11

32 VSSCPU

SATAC/PCIEXC0 12

31 **DOC2

VSSSATA 13

30 VSSA

NC 14

29 VDDA

15 16 17 18 19 20 21 22 23 24 25 26 27 28

VTTPWR_GD#/PD

SEL24_48

RESET_I#

SDATA

SCLK

PLL4

Fixed

Divider

I2C

Logic

WDT

VDD_48

48M

24_48M

SRESET#

* Indicates internal pull-up

** indicates internal pull-down

...................... Document #: 001-05677 Rev. *D Page 1 of 28

400 West Cesar Chavez, Austin, TX 78701

1+(512) 416-8500 1+(512) 416-9669

www.silabs.com

1 page

CY28551-3

Serial Data Interface

Data Protocol

To enhance the flexibility and function of the clock synthesizer,

a two-signal serial interface is provided. Through the Serial

Data Interface, various device functions, such as individual

clock output buffers, can be individually enabled or disabled.

The registers associated with the Serial Data Interface

initialize to their default setting upon power-up, and therefore

use of this interface is optional. Clock device register changes

are normally made upon system initialization, if any are

required. The interface cannot be used during system

operation for power management functions.

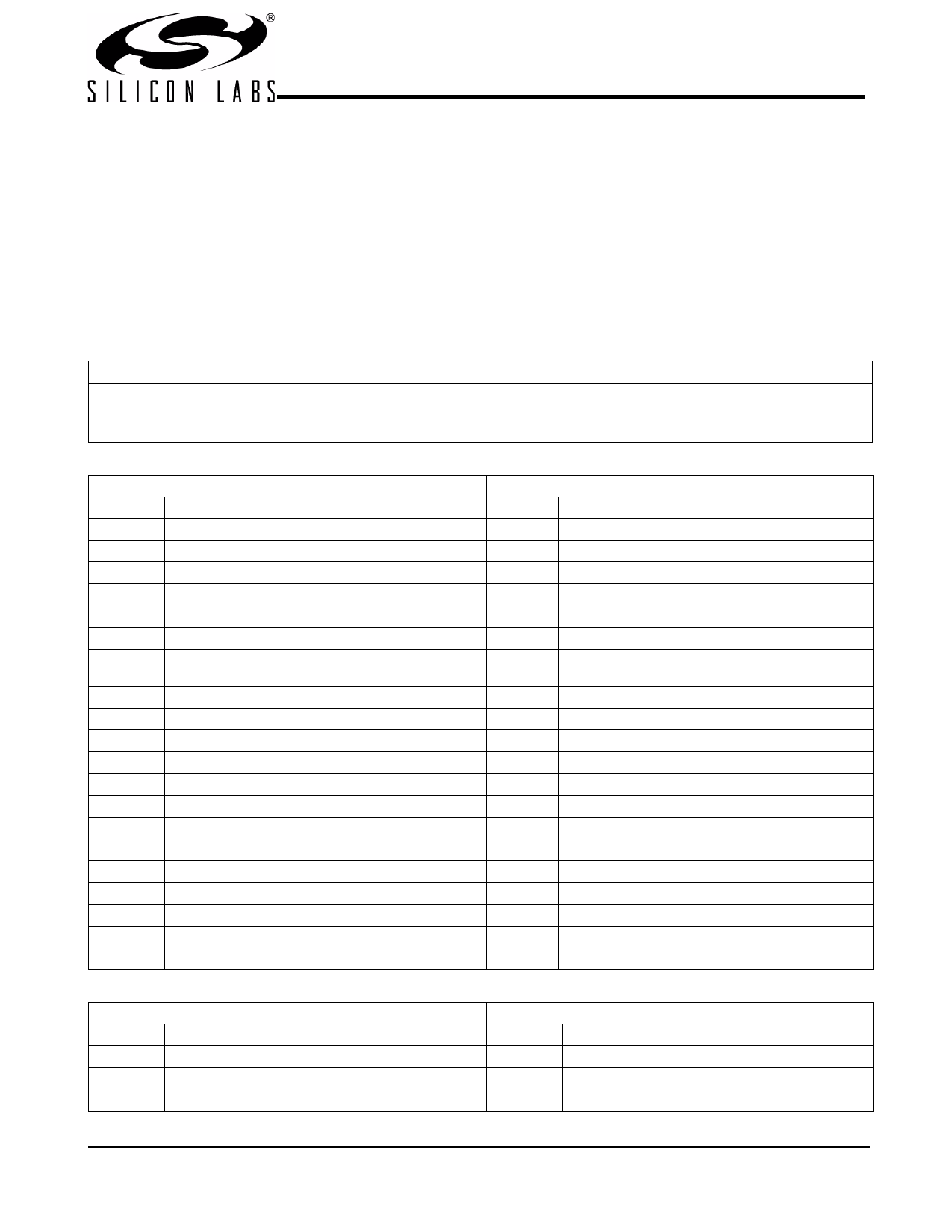

Table 2. Command Code Definition

The clock driver serial protocol accepts byte write, byte read,

block write, and block read operations from the controller. For

block write/read operation, the bytes must be accessed in

sequential order from lowest to highest byte (most significant

bit first) with the ability to stop after any complete byte has

been transferred. For byte write and byte read operations, the

system controller can access individually indexed bytes. The

offset of the indexed byte is encoded in the command code,

as described in Table 2. The block write and block read

protocol is outlined in Table 3 while Table 4 outlines the corre-

sponding byte write and byte read protocol. The slave receiver

address is 11010010 (D2h).

Bit Description

7 0 = Block read or block write operation, 1 = Byte read or byte write operation

(6:0) Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be

'0000000'

Table 3. Block Read and Block Write Protocol

Bit

1

8:2

9

10

18:11

19

27:20

28

36:29

37

45:38

46

....

....

....

....

Block Write Protocol

Description

Start

Slave address – 7 bits

Write

Acknowledge from slave

Command Code – 8 bits

Acknowledge from slave

Byte Count – 8 bits

(Skip this step if I2C_EN bit set)

Acknowledge from slave

Data byte 1 – 8 bits

Acknowledge from slave

Data byte 2 – 8 bits

Acknowledge from slave

Data Byte/Slave Acknowledges

Data Byte N – 8 bits

Acknowledge from slave

Stop

Bit

1

8:2

9

10

18:11

19

20

Block Read Protocol

Description

Start

Slave address – 7 bits

Write

Acknowledge from slave

Command Code – 8 bits

Acknowledge from slave

Repeat start

27:21

28

29

37:30

38

46:39

47

55:48

56

....

....

....

....

Slave address – 7 bits

Read = 1

Acknowledge from slave

Byte Count from slave – 8 bits

Acknowledge

Data byte 1 from slave – 8 bits

Acknowledge

Data byte 2 from slave – 8 bits

Acknowledge

Data bytes from slave/Acknowledge

Data Byte N from slave – 8 bits

NOT Acknowledge

Stop

Table 4. Byte Read and Byte Write Protocol

Byte Write Protocol

Bit Description

1 Start

8:2 Slave address – 7 bits

9 Write

Byte Read Protocol

Bit Description

1 Start

8:2 Slave address – 7 bits

9 Write

......................Document #: 001-05677 Rev. *D Page 5 of 28

5 Page

CY28551-3

Byte 13: Control Register 13 (continued)

Bit @Pup

30

20

10

Type

R/W

R/W

R/W

Name

WD_TIMER2

WD_TIMER1

WD_TIMER0

00

R/W

WD_EN

Description

Watchdog timer time stamp selection

000: Reserved (test mode)

001: 1 * Time_Scale

010: 2 * Time_Scale

011: 3 * Time_Scale

100: 4 * Time_Scale

101: 5 * Time_Scale

110: 6 * Time_Scale

111: 7 * Time_Scale

Watchdog timer enable, when the bit is asserted, Watchdog timer is

triggered and time stamp of WD_Timer is loaded

0 = Disable, 1 = Enable

Byte 14: Control Register 14

Bit @Pup

70

60

50

40

30

20

10

00

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Name

CPU_DAF_N7

CPU_DAF_N6

CPU_DAF_N5

CPU_DAF_N4

CPU_DAF_N3

CPU_DAF_N2

CPU_DAF_N1

CPU_DAF_N0

Description

If Prog_CPU_EN is set, the values programmed in CPU_DAF_N[8:0] and

CPU_DAF_M[6:0] will be used to determine the CPU output frequency.

The setting of the FS_Override bit determines the frequency ratio for CPU

and other output clocks. When it is cleared, the same frequency ratio

stated in the Latched FS[E:A] register will be used. When it is set, the

frequency ratio stated in the FSEL[3:0] register will be used.

Byte 15: Control Register 15

Bit @Pup

70

60

Type

R/W

R/W

50

40

30

20

10

00

R/W

R/W

R/W

R/W

R/W

R/W

Name

CPU_DAF_N8

CPU_DAF_M6

CPU_DAF_M5

CPU_DAF_M4

CPU_DAF_M3

CPU_DAF_M2

CPU_DAF_M1

CPU_DAF_M0

Description

If Prog_CPU_EN is set, the values programmed in CPU_DAF_N[8:0] and

CPU_DAF_M[6:0] will be used to determine the CPU output frequency.

The setting of the FS_Override bit determines the frequency ratio for CPU

and other output clocks. When it is cleared, the same frequency ratio

stated in the Latched FS[E:A] register will be used. When it is set, the

frequency ratio stated in the FSEL[3:0] register will be used.

Byte 16: Control Register 16

Bit @Pup

70

60

50

40

30

20

10

00

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Name

PCIE_DAF_N7

PCIE_DAF_N6

PCIE_DAF_N5

PCIE_DAF_N4

PCIE_DAF_N3

PCIE_DAF_N2

PCIE_DAF_N1

PCIE_DAF_N0

Description

The PCIE_DAF_N[8:0] will be used to configure PCIE frequency for Dial-A

Frequency

.................... Document #: 001-05677 Rev. *D Page 11 of 28

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet CY28551-3.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY28551-3 | Universal Clock Generator | Silicon Laboratories |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |