|

|

PDF EN29F010 Data sheet ( Hoja de datos )

| Número de pieza | EN29F010 | |

| Descripción | 1 Megabit (128K x 8-bit) 5V Flash Memory | |

| Fabricantes | Eon Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de EN29F010 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

EN29F010

1 Megabit (128K x 8-bit) 5V Flash Memory

EN29F010

FEATURES

• 5.0V operation for read/write/erase

operations

• Fast Read Access Time

- 45ns, 55ns, 70ns, and 90ns

• Sector Architecture:

- 8 uniform sectors of 16Kbytes each

- Supports full chip erase

- Individual sector erase supported

- Sector protection:

Hardware locking of sectors to prevent

program or erase operations within

individual sectors

• High performance program/erase speed

- Byte program time: 7µs typical

- Sector erase time: 300ms typical

- Chip erase time: 3s typical

• Low Standby Current

- 1µA CMOS standby current-typical

- 1mA TTL standby current

• Low Power Active Current

- 12mA typical active read current

- 30mA program/erase current

• JEDEC Standard program and erase

commands

• JEDEC standard DATA polling and toggle

bits feature

• Single Sector and Chip Erase

• Sector Unprotect Mode

• Embedded Erase and Program Algorithms

• Erase Suspend / Resume modes:

Read and program another Sector during

Erase Suspend Mode

• 0.23 µm triple-metal double-poly

triple-well CMOS Flash Technology

• Low Vcc write inhibit < 3.2V

• 100K endurance cycle

• Package Options

- 32-pin PDIP

- 32-pin PLCC

- 32-pin 8mm x 20mm TSOP (Type 1)

- 32-pin 8mm x 14mm TSOP (Type 1)

• Commercial and Industrial Temperature

Ranges

GENERAL DESCRIPTION

The EN29F010 is a 1-Megabit, electrically erasable, read/write non-volatile flash memory.

Organized into 128K bytes with 8 bits per byte, the 1M of memory is arranged in eight uniform

sectors of 16Kbytes each. Any byte can be programmed typically in 7µs. The EN29F010 features

5.0V voltage read and write operation, with access times as fast as 45ns to eliminate the need for

WAIT states in high-performance microprocessor systems.

The EN29F010 has separate Output Enable ( OE ), Chip Enable ( CE ), and Write Enable ( W E )

controls, which eliminate bus contention issues. This device is designed to allow either single

Sector or full chip erase operation, where each Sector can be individually protected against

program/erase operations or temporarily unprotected to erase or program. The device can sustain a

minimum of 100K program/erase cycles on each Sector.

This Data Sheet may be revised by subsequent versions 1

or modifications due to changes in technical specifications.

©2003 Eon Silicon Solution, Inc., www.essi.com.tw

Rev. A, Issue Date: 2003/10/20

1 page

EN29F010

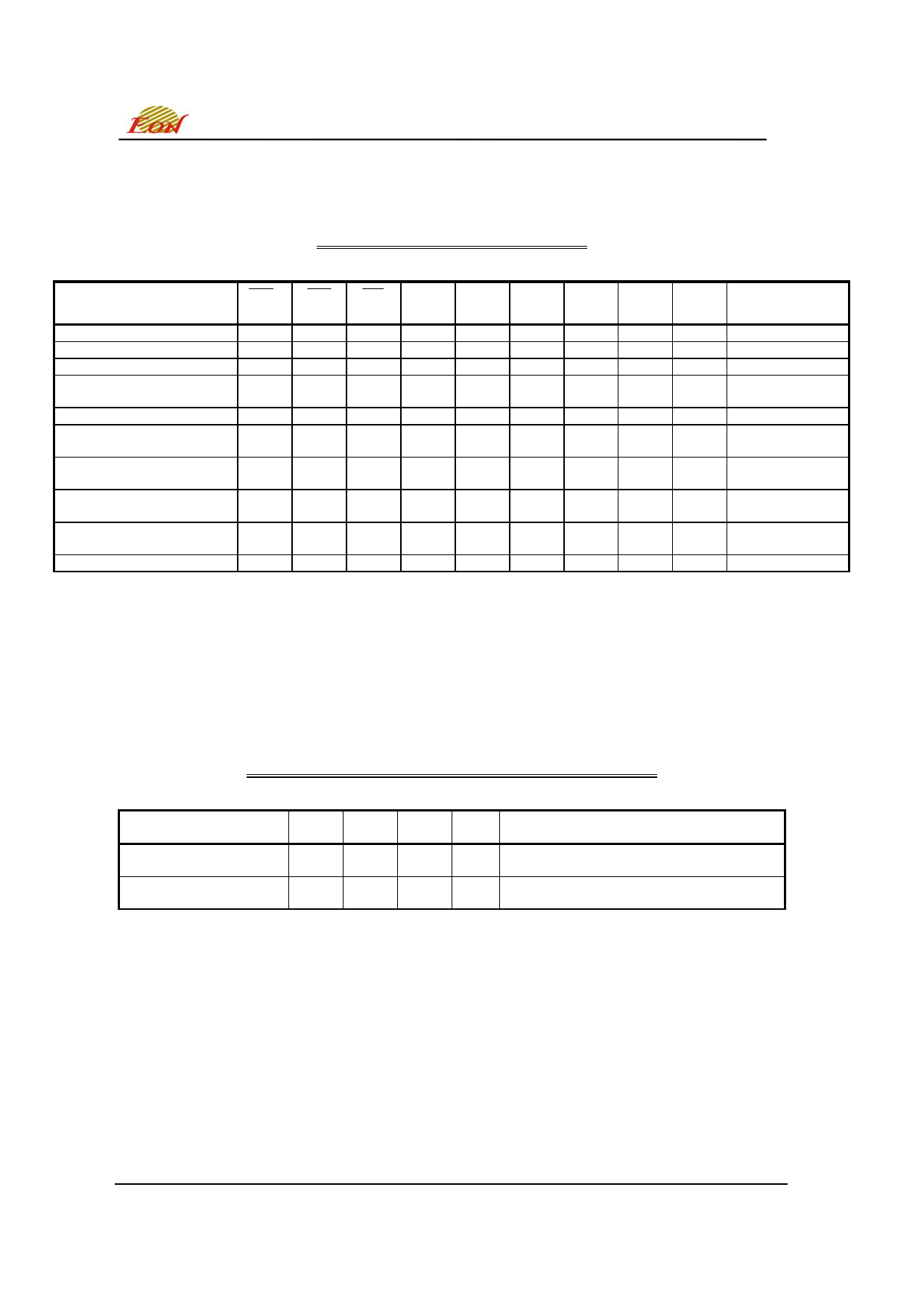

TABLE 3. OPERATING MODES

1M FLASH USER MODE TABLE

USER MODE

C E WE OE A9 A8 A6 A1 A0 Ax/y

DQ(0-7)

STANDBY

READ

OUTPUT DISABLE

READ

MANUFACTURE ID

READ DEVICE ID

VERIFY SECTOR

PROTECTION

SECTOR

PROTECTION

VERIFY SECTOR

UNPROTECTION

SECTOR

UNPROTECTION

WRITE

HXXXXXXXX

HI-Z

L H L A9 A8 A6 A1 A0 Ax/y

DQ (0-7)

L H H X X X X X Ax/y

HI-Z

L H L VID L/H L L L X MANUFACTURE

ID

L H L VID X L L H X

DEVICE ID

L H L VID X L H L X

CODE

L Pulse VID VID

X

L

X

X

X

L

L H L VID X H H L X

X

CODE

L Pulse VID VID

X

H

H

L

X

L

L L H A9 A8 A6 A1 A0 Ax/y

X

DIN (0-7)

NOTES:

1) L = VIL, H = VIH, VID = 11.0V ± 0.5V

2) X = Don’t care, either VIH or VIL

3) Ax/y: Ax = Addr(x), Ay = Addr(y)

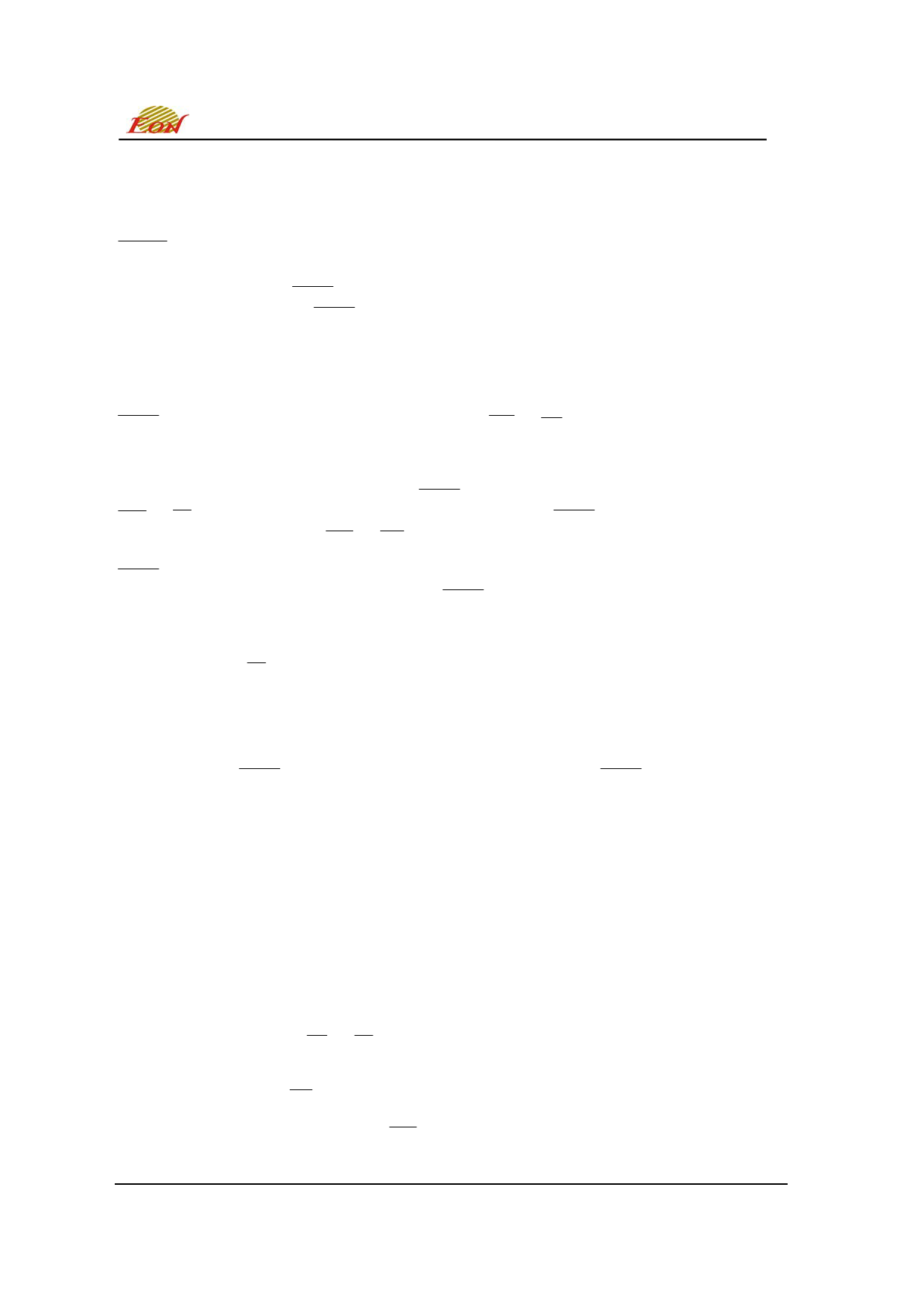

TABLE 4. DEVICE IDENTIFICTION

1M FLASH MANUFACTURER/DEVICE ID TABLE

A8 A6 A1 A0

READ

MANUFACTURER ID

READ

DEVICE ID

H(1)

X(2)

L

L

LL

LH

DQ(7-0)

HEX

MANUFACTURER ID

1C

DEVICE ID

20

NOTES:

1) If a Manufacturing ID is read with A8 = L, the chip will output a configuration code 7Fh. A further

Manufacturing ID must be read with A8 = H.

2) X = Don’t care

This Data Sheet may be revised by subsequent versions

5

or modifications due to changes in technical specifications.

©2003 Eon Silicon Solution, Inc., www.essi.com.tw

Rev. A, Issue Date: 2003/10/20

5 Page

EN29F010

WRITE OPERATION STATUS

DQ7

DATA Polling

The EN29F010 provides DATA Polling on DQ7 to indicate to the host system the status of the

embedded operations. The DATA Polling feature is active during the Byte Programming, Sector

Erase, Chip Erase, and Erase Suspend. (See Table 6)

When the Byte Programming is in progress, an attempt to read the device will produce the

complement of the data last written to DQ7. Upon the completion of the Byte Programming, an

attempt to read the device will produce the true data last written to DQ7. For the Byte Programming,

DATA polling is valid after the rising edge of the fourth WE or CE pulse in the four-cycle sequence.

When the embedded Erase is in progress, an attempt to read the device will produce a “0” at the

DQ7 output. Upon the completion of the embedded Erase, the device will produce the “1” at the DQ7

output during the read. For Chip Erase, the DATA polling is valid after the rising edge of the sixth

W E or CE pulse in the six-cycle sequence. For Sector Erase, DATA polling is valid after the last

rising edge of the sector erase W E or C E pulse.

DATA Polling must be performed at any address within a sector that is being programmed or

erased and not a protected sector. Otherwise, DATA polling may give an inaccurate result if the

address used is in a protected sector.

Just prior to the completion of the embedded operations, DQ7 may change asynchronously when

the output enable ( OE ) is low. This means that the device is driving status information on DQ7 at

one instant of time and valid data at the next instant of time. Depending on when the system

samples the DQ7 output, it may read the status of valid data. Even if the device has completed the

embedded operations and DQ7 has a valid data, the data output on DQ0-DQ6 may be still invalid.

The valid data on DQ0-DQ7 will be read on the subsequent read attempts.

The flowchart for DATA Polling (DQ7) is shown on Flowchart 5. The DATA Polling (DQ7) timing

diagram is shown in Figure 8.

DQ6

Toggle Bit I

The EN29F010 provides a “Toggle Bit” on DQ6 to indicate to the host system the status of the

embedded programming and erase operations. (See Table 6)

During an embedded Program or Erase operation, successive attempts to read data from the device

at any address (by toggling OE or CE ) will result in DQ6 toggling between “zero” and “one”. Once

the embedded Program or Erase operation is complete, DQ6 will stop toggling and valid data will be

read on the next successive attempts. During Byte Programming, the Toggle Bit is valid after the

rising edge of the fourth WE pulse in the four-cycle sequence. For Chip Erase, the Toggle Bit is

valid after the rising edge of the sixth-cycle sequence. For Sector Erase, the Toggle Bit is valid after

the last rising edge of the Sector Erase W E pulse. The Toggle Bit is also active during the sector

erase time-out window.

This Data Sheet may be revised by subsequent versions 11 ©2003 Eon Silicon Solution, Inc., www.essi.com.tw

or modifications due to changes in technical specifications.

Rev. A, Issue Date: 2003/10/20

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EN29F010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EN29F010 | 1 Megabit (128K x 8-bit) 5V Flash Memory | Eon Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |