|

|

PDF AT89LP51RD2 Data sheet ( Hoja de datos )

| Número de pieza | AT89LP51RD2 | |

| Descripción | 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT89LP51RD2 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

Features

• 8-bit Microcontroller Compatible with 8051 Products

• Enhanced 8051 Architecture

– Single Clock Cycle per Byte Fetch

– 12 Clock per Machine Cycle Compatibility Mode

– Up to 20 MIPS Throughput at 20 MHz Clock Frequency

– Fully Static Operation: 0 Hz to 20 MHz

– On-chip 2-cycle Hardware Multiplier

– 16x16 Multiply–Accumulate Unit

– 256 x 8 Internal RAM

– On-chip 2KB Expanded RAM (ERAM)

• Software Selectable Size (0, 256, 512, 768, 1024, 1792, 2048 Bytes)

– Dual Data Pointers

– 4-level Interrupt Priority

• Nonvolatile Program and Data Memory

– 64KB of In-System Programmable (ISP) Flash Program Memory

– 4KB of EEPROM (AT89LP51ED2/ID2 Only)

– 512-byte User Signature Array

– Endurance: 10,000 Write/Erase Cycles

– Serial Interface for Program Downloading

– 2KB Boot ROM Contains Low Level Flash Programming Routines and a Default

Serial Bootloader

• Peripheral Features

– Three 16-bit Enhanced Timer/Counters

– Seven 8-bit PWM Outputs

– 16-bit Programmable Counter Array

• High Speed Output, Compare/Capture

• Pulse Width Modulation, Watchdog Timer Capabilities

– Enhanced UART with Automatic Address Recognition and Framing

Error Detection

– Enhanced Master/Slave SPI with Double-buffered Send/Receive

– Two Wire Interface 400K bit/s

– Programmable Watchdog Timer with Software Reset

– 8 General-purpose Interrupt and Keyboard Interface Pins

• Special Microcontroller Features

– Dual Oscillator Support: Crystal, 32 kHz Crystal, 8 MHz Internal (AT89LP51ID2)

– Two-wire On-Chip Debug Interface

– Brown-out Detection and Power-on Reset with Power-off Flag

– Selectable Polarity External Reset Pin

– Low Power Idle and Power-down Modes

– Interrupt Recovery from Power-down Mode

– 8-bit Clock Prescaler

• I/O and Packages

– Up to 40 Programmable I/O Lines

– Green (Pb/Halide-free) PLCC44, VQFP44, QFN44, PDIP40

– Configurable I/O Modes

• Quasi-bidirectional (80C51 Style), Input-only (Tristate)

• Push-pull CMOS Output, Open-drain

• Operating Conditions

– 2.4V to 5.5V VCC Voltage Range

– -40° C to 85°C Temperature Range

– 0 to 20 MHz @ 2.4V–5.5V (Single-cycle)

8-bit Flash

Microcontroller

with 64KB

Program

Memory

AT89LP51RD2

AT89LP51ED2

AT89LP51ID2

Preliminary

Summary

3714AS–MICRO–7/11

1 page

AT89LP51RD2/ED2/ID2 Summary - Preliminary

Table 1-1. Atmel AT89LP51RD2/ED2/ID2 Pin Description

Pin Number

VQFP

VQFN PLCC

(1)

PDIP

Symbol

Type Description

I/O P0.2: User-configurable I/O Port 0 bit 2.

35 41 37 P0.2 I/O AD2: External memory interface Address/Data bit 2.

I ADC2: ADC analog input 2.

I/O P0.1: User-configurable I/O Port 0 bit 1.

36 42 38 P0.1 I/O AD1: External memory interface Address/Data bit 1.

I ADC1: ADC analog input 1.

I/O P0.0: User-configurable I/O Port 0 bit 0.

37 43 39 P0.0 I/O AD0: External memory interface Address/Data bit 0.

I ADC0: ADC analog input 0.

38 44 40 VDD

I Supply Voltage

39 1

P4.2

P4.2: User-configurable I/O Port 4bit 2.

I/O

XTAL2B: Output from low-frequency inverting oscillator amplifier B (AT89LP51ID2 only). It may

be used as a port pin if the internal RC oscillator or external clock is selected as the clock

source.

P1.0: User-configurable I/O Port 1 bit 0.

40 2

1

P1.0

I/O T2: Timer 2 External Input or Clock Output.

I/O XTAL1B: Input to the low-frequency inverting oscillator amplifier B and internal clock generation

circuits. It may be used as a port pin if the internal RC oscillator is selected as the clock source.

41 3

I/O P1.1: User-configurable I/O Port 1 bit 1.

2 P1.1

I T2EX: Timer 2 External Capture/Reload Input.

I SS: SPI Slave-Select.

42 4

3

P1.2

I/O P1.2: User-configurable I/O Port 1 bit 2.

43 5

4

P1.3

I/O P1.3: User-configurable I/O Port 1 bit 3.

I/O CEX0: Capture/Compare external I/O for PCA module 0.

44

Note:

I/O P1.4: User-configurable I/O Port 1 bit 4.

6 5 P1.4 I SS: SPI Slave-Select (Remap Mode). This pin is an input for In-System Programming

I/O CEX1: Capture/Compare external I/O for PCA module 1.

1. The AT89LP51ID2 is not available in the PDIP package.

2. Overview

The Atmel® AT89LP51RD2/ED2/ID2 is a low-power, high-performance CMOS 8-bit 8051 micro-

controller with 64KB of In-System Programmable Flash program memory. The AT89LP51ED2

and AT89LP51ID2 provide an additional 4KB of EEPROM for nonvolatile data storage. The

devices are manufactured using Atmel's high-density nonvolatile memory technology and are

compatible with the industry-standard 80C51 instruction set.

The AT89LP51RD2/ED2/ID2 is built around an enhanced CPU core that can fetch a single byte

from memory every clock cycle. In the classic 8051 architecture, each fetch requires 6 clock

cycles, forcing instructions to execute in 12, 24 or 48 clock cycles. In the

AT89LP51RD2/ED2/ID2 CPU, standard instructions need only one to four clock cycles providing

six to twelve times more throughput than the standard 8051. Seventy percent of instructions

need only as many clock cycles as they have bytes to execute, and most of the remaining

instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS

throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current con-

sumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a

much lower speed and thereby greatly reducing power consumption and EMI. The

3714AS–MICRO–7/11

5

5 Page

AT89LP51RD2/ED2/ID2 Summary - Preliminary

2.3.9 Security

The AT89LP51RD2/ED2/ID2 does not support the external access pin (EA). Therefore it is not

possible to execute from external program memory in address range 0000H–1FFFH. When the

third Lockbit is enabled (Lock Mode 4) external program execution is disabled for all addresses

above 1FFFH. This differs from AT89C51RD2/ED2/ID2 where Lock Mode 4 prevents EA from

being sampled low, but may still allow external execution at addresses outside the 8K internal

space.

2.3.10

Programming

The AT89LP51RD2/ED2/ID2 supports a richer command set for In-System Programming (ISP).

Existing AT89C51RD2/ED2 programmers should be able to program the

AT89LP51RD2/ED2/ID2 in byte mode. In page mode the AT89LP51RD2/ED2/ID2 only supports

programming of a half-page of 64 bytes and therefore requires an extra address byte as com-

pared to AT89C51RD2/ED2. Furthermore the device signature is located at addresses 0000H,

0001H and 0003H instead of 0000H, 0100H and 0200H.

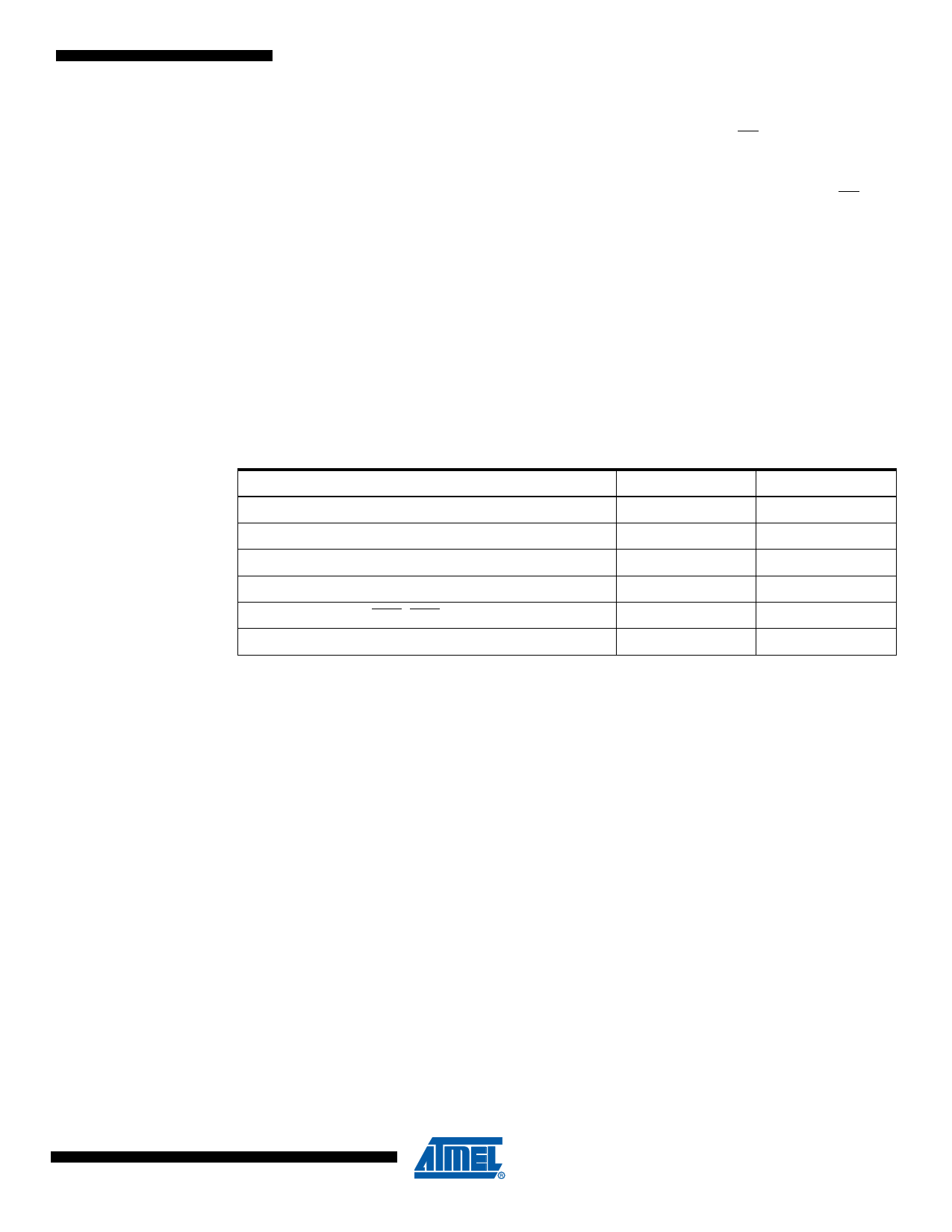

Table 2-3. Compatibility Mode versus Fast Mode Summary

Feature

Compatibility

Instruction Fetch in System Clocks

3

Instruction Execution Time in System Clocks

6, 12, 18 or 24

Default System Clock Divisor

2

Default Timer Prescaler Divisor

6

Pin Sampling Rate (INT0, INT1, T0, T1, T2, T2EX)

Prescaler Rate

Minimum RST input pulse in System Clocks

12

Fast

1

1, 2, 3, 4 or 5

1

1

System Clock

2

3714AS–MICRO–7/11

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet AT89LP51RD2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT89LP51RD2 | 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |