|

|

PDF SAMG53G19B Data sheet ( Hoja de datos )

| Número de pieza | SAMG53G19B | |

| Descripción | SMART ARM-based Flash MCU | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SAMG53G19B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

SAM G53G / SAM G53N

Atmel | SMART ARM-based Flash MCU

DATASHEET

Description

The Atmel® | SMART SAM G53 is a series of Flash microcontrollers based on the

high-performance 32-bit ARM® Cortex®-M4 RISC processor. It operates at a

maximum speed of 48 MHz and features up to 512 Kbytes of Flash and 96 Kbytes

of SRAM. The peripheral set includes one USART, two UARTs, three I2C-bus

interfaces (TWI), up to two SPIs, two three-channel general-purpose 16-bit timers,

two I2S controllers with two-way, one-channel pulse density modulation, one real-

time timer (RTT) and one 8-channel 12-bit ADC.

The Atmel | SMART SAM G53 devices have two software-selectable low-power

modes: Sleep and Wait. In Sleep mode, the processor is stopped while all other

functions can be kept running. In Wait mode, all clocks and functions are stopped

but some peripherals can be configured to wake up the system based on events,

including partial asynchronous wake-up (SleepWalking™).

The Event System allows peripherals to receive, react to and send events in

Active and Sleep modes without processor intervention.

A general-purpose microcontroller with the best ratio in terms of reduced power

consumption, processing power and peripheral set, the SAM G53 series sustains

a wide range of applications including consumer, industrial control, and PC

peripherals.

The device operates from 1.62V to 3.6V and is available in a 49-ball WLCSP

package and a 100-pin LQFP package.

Features

Core

̶ ARM Cortex-M4 up to 48 MHz

̶ Memory Protection Unit (MPU)

̶ DSP Instructions

̶ Floating Point Unit (FPU)

̶ Thumb®-2 instruction set

Memories

̶ 512 Kbytes embedded Flash

̶ 96 Kbytes embedded SRAM

System

̶ Embedded voltage regulator for single-supply operation

Atmel-11240F-ATARM-SAM-G53G-SAM-G53N-Datasheet_24-Jul-15

1 page

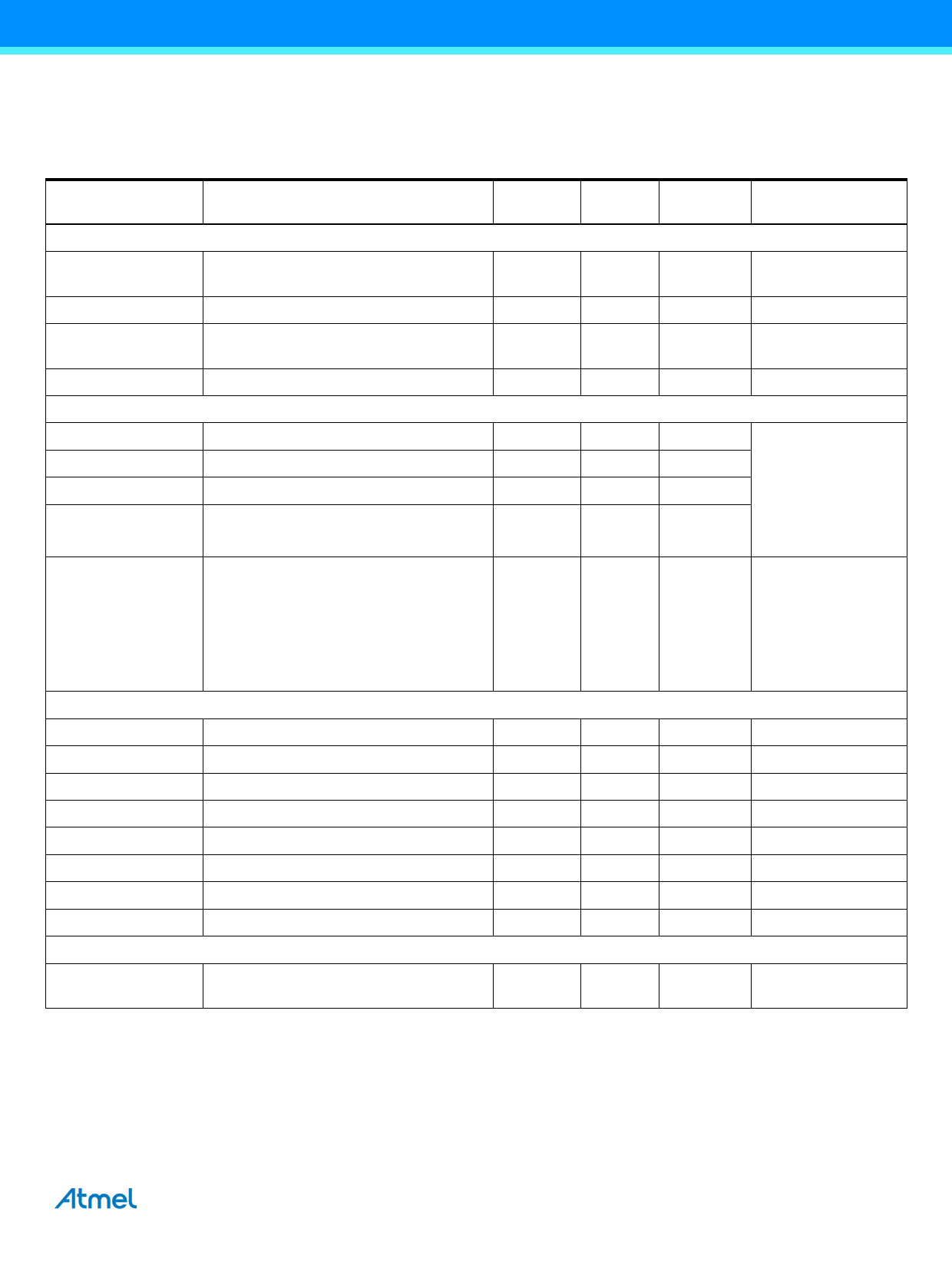

3. Signal Description

Table 3-1 provides details on the signal names classified by peripheral.

Table 3-1. Signal Description List

Signal Name

VDDIO

VDDOUT

Function

Type

Power Supplies

Peripheral I/O Lines, Voltage Regulator,

ADC Power Supply

Power

Voltage Regulator Output

Power

Active

Level

–

–

VDDCORE

Core Chip Power Supply

Power

–

GND

XIN

XOUT

XIN32

Ground

Ground

Clocks, Oscillators and PLLs

Main Oscillator Input (Bypass mode)

Input

Main Oscillator Output

Output

Slow Clock Oscillator Input (Bypass mode)

Input

–

–

–

–

XOUT32

Slow Clock Oscillator Output

Output

–

PCK0 - PCK2

Programmable Clock Output

Output

–

TCK

TDI

TDO

TRACESWO

SWDIO

SWCLK

TMS

JTAGSEL

ERASE

ICE and JTAG

Test Clock

Input

Test Data In

Input

Test Data Out

Output

Trace Asynchronous Data Out

Output

Serial Wire Input/Output

I/O

Serial Wire Clock

Input

Test Mode Select

Input

JTAG Selection

Input

Flash Memory

Flash and NVM Configuration Bits Erase

Command

Input

–

–

–

–

–

–

–

High

High

Voltage

Reference

Comments

– 1.62V to 3.6V

––

–

Connected externally

to VDDOUT

––

VDDIO

–

VDDIO

–

–

Reset state:

- PIO input

- Internal pull-up

disabled

- Schmitt Trigger

enabled

Reset state:

- PIO input

- Internal pull-up

enabled

- Schmitt Trigger

enabled

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

No pull-up resistor

No pull-up resistor

–

–

–

–

No pull-up resistor

Pull-down resistor

VDDIO

Pull-down (15 kΩ)

resistor

SAM G53G / SAM G53N [DATASHEET]

Atmel-11240F-ATARM-SAM-G53G-SAM-G53N-Datasheet_24-Jul-15

5

5 Page

5.4.2

Wait Mode

Wait mode allows the device to achieve very low power consumption levels while remaining in a powered state

with a wake-up time of less than 5 µs. Current consumption in Wait mode is typically less than 8 µA (total current

consumption). In Wait mode, the clocks of the core, the peripherals and memories are stopped. However, power

supplies are maintained to ensure memory and CPU context retention.

The wake-up time of 5 µs is achieved when entry into and exit from Wait mode are performed in internal SRAM.

The wake-up time increases to 70 µs if entry into Wake-up mode is performed in internal Flash.

Wait mode is entered using either the WAITMODE bit in the PMC Clock Generator Main Oscillator register

(CKGR_MOR) or the Wait for Event (WFE) instruction. Detailed sequences are provided below.

Note that the WFE instruction can add complexity in application state machines due to the fact that the WFE

instruction goes along with an event flag of the Cortex core (cannot be managed by the software application). The

event flag can be set by interrupts, a debug event or an event signal from another processor. Since an interrupt

can take place just before the execution of WFE, WFE takes into account events that happened in the past. As a

result, WFE prevents the device from entering Wait mode if an interrupt event has occurred. To work around this

complexity, follow the sequence using the WAITMODE bit described below.

The Cortex-M4 processor is able to handle external or internal events in order to wake up the core. This is done by

configuring the external lines WKUP0–15 as fast start-up wake-up pins (refer to Section 5.5 “Fast Start-up”) or the

RTT and RTC alarms for internal events.

To enter Wait mode using the WAITMODE bit:

1. Select the 8/16/24 MHz fast RC oscillator as the Main Clock. If frequency of 24 MHz is selected and the code is

running from the SRAM, wake-up time is less than 5 µs.

2. Program the FLPM field in the PMC Fast Startup Mode Register (PMC_FSMR)(1).

3. Set the number of Flash wait states to 0 by writing a zero to the FWS field in the EEFC Flash Mode Register

(EEFC_MR).

4. Write a one to the WAITMODE bit in the PMC Clock Generator Main Oscillator Register (CKGR_MOR).

5. Wait for MCKRDY = 1 in the PMC Status Register (PMC_SR).

To enter Wait mode using the WFE instruction:

1. Select the 8/16/24 MHz fast RC oscillator as the Main Clock. If 24 MHz is selected and the code is running on the

SRAM, wake-up time is less than 5 µs.

2. Program the FLPM field in the PMC Fast Startup Mode Register (PMC_FSMR)(1).

3. Set the number of Flash wait states to 0 by writing a zero to the FWS field in the EEFC Flash Mode Register

(EEFC_MR).

4. Write a one to the LPM bit in the PMC Fast Startup Mode Register (PMC_FSMR).

5. Ensure that the SLEEPDEEP bit in the System Control Register (SCB_SCR) is cleared.

6. Execute the Wait For Event (WFE) instruction of the processor.

Note:

1. Depending on the value of the field FLPM, the Flash enters three different modes:

FLPM = 0: Flash in Stand-by mode (low power consumption levels)

FLPM = 1: Flash in Deep power-down mode (extra low power consumption levels)

FLPM = 2: Flash in Idle mode. Memory ready for Read access.

5.4.3

Sleep Mode

In Sleep mode, power consumption of the device versus response time is optimized. Only the core clock is

stopped. The peripheral clocks can be enabled. The current consumption in Sleep mode is application-dependent.

Sleep mode is entered via Wait for Interrupt (WFI) instructions.

The processor can be awakened from an interrupt if the WFI instruction of the Cortex-M4 is used.

SAM G53G / SAM G53N [DATASHEET]

Atmel-11240F-ATARM-SAM-G53G-SAM-G53N-Datasheet_24-Jul-15

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAMG53G19B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAMG53G19A | SMART ARM-based Flash MCU | ATMEL Corporation |

| SAMG53G19B | SMART ARM-based Flash MCU | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |