|

|

PDF PEF24911 Data sheet ( Hoja de datos )

| Número de pieza | PEF24911 | |

| Descripción | Quad ISDN 2B1Q Echocanceller Digital Front End | |

| Fabricantes | Infineon Technologies | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PEF24911 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet, DS 3, July 2001

DFE-Q V2.1

Quad ISDN 2B1Q

Echocanceller Digital

Front End

PEF 24911 Version 2.1

Wired

Communications

Never stop thinking.

1 page

PEF 24911

Table of Contents

Page

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2 Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.3 System Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.4 Operational Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Pin Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3 Pinning Changes from DFE-Q V1.3 to DFE-Q V2.1 . . . . . . . . . . . . . . . . . 19

3

3.1

3.2

3.2.1

3.2.2

3.2.3

3.2.4

3.2.5

3.3

3.4

3.5

3.6

3.7

3.8

3.8.1

3.8.2

3.8.3

3.9

3.10

3.11

3.12

3.13

3.14

3.15

3.16

3.16.1

3.16.2

3.16.3

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

IOM®-2 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

IOM®-2 Interface Frame Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Superframe Marker Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

IOM®-2 Command/ Indicate Channel . . . . . . . . . . . . . . . . . . . . . . . . . . 24

IOM®-2 Monitor Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

MON-12 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Interface to the Analog Front End . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

General Purpose I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

U-Transceiver Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2B1Q Frame Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Maintenance Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

M4 Bit Reporting to State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

M4, M5, M6 Bit Control Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Start of Maintenance Bit Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Embedded Operations Channel (EOC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

EOC Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Cyclic Redundancy Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Scrambling/ Descrambling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Encoding/ Decoding (2B1Q) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

C/I Codes (2B1Q) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

State Machine Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

LT Mode State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Inputs to the U-Transceiver in LT-Mode . . . . . . . . . . . . . . . . . . . . . . . . 58

Outputs of the U-Transceiver in LT-Mode . . . . . . . . . . . . . . . . . . . . . . . 62

LT-States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4 Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2 Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.3 Layer 1 Activation/ Deactivation Procedures . . . . . . . . . . . . . . . . . . . . . . . 71

Data Sheet

2001-07-16

5 Page

PEF 24911

Introduction

1 Introduction

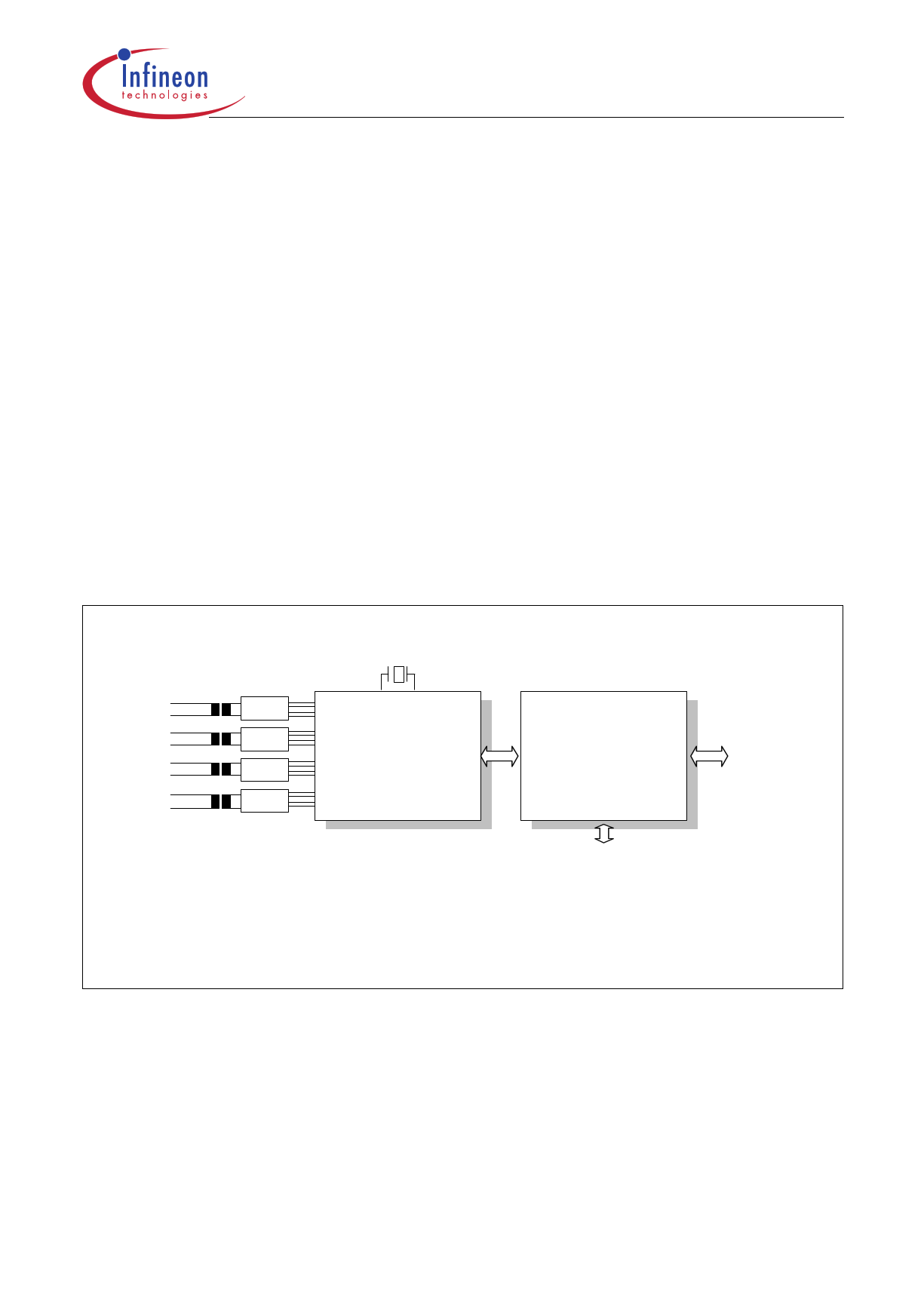

The Quad ISDN 2B1Q Echocanceller Digital Front End (DFE-Q) is the digital part of an

optimized two-chip solution featuring 4x ISDN basic rate access and IDSL access at 144

kbit/s. The PEF 24911 is designed to provide in conjunction with the Quad ISDN

Echocanceller Analog Front End (PEF 24902 V2.1) full duplex data transmission at the

U-reference point according to ANSI T1.601 (1998), ETSI TS 102 080 (1998) and ITU-

T G.961 standards.

The DFE-Q 2nd generation has been completely reengineered to guarantee the

availability of the well proved DFE-Q/AFE solution over the year 2000. The PEF 24911

V2.1 is downwards pin compatible and functionally equivalent to the DFE-Q V1.x. Thus,

line card manufacturers can make use of the most advanced process technology without

the need to change their current design (besides the changeover to 3.3 V power supply).

No software changes are required if the DFE-Q V2.1 is deployed in existing DFE-Q V1.x

solutions. Some new features are provided such as free programmable filtering options

for the maintenance bits (M1-6) and enhanced monitoring and test functions. The data

rate is programmable from 1 Mbit/s to 4 Mbit/s.

4x U

Hyb rid

Hyb rid

Hyb rid

Hyb rid

15.36MHz

AFE V2.1

PEF 24902

DFE-Q V2.1

PEF 24911

I OM ®-2

Relay Driver/

Power Controller

chipset.vsd

Figure 1 DFE-Q/ AFE 2nd Generation Chip Set

The output and input pins are throughout 5 V TTL compatible although the PEF 24911

is processed in advanced 3.3 V CMOS technology. A power down state with very low

power consumption is featured.

The PEF 24911 comes in a P-MQFP-64 package.

Data Sheet 1 2001-07-16

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PEF24911.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PEF24911 | Quad ISDN 2B1Q Echocanceller Digital Front End | Infineon Technologies |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |