|

|

PDF ISL2671286 Data sheet ( Hoja de datos )

| Número de pieza | ISL2671286 | |

| Descripción | 20kSPS SAR ADC | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL2671286 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

12-Bit, 20kSPS SAR ADC

ISL2671286

The ISL2671286 is a sampling SAR-type ADC which features

excellent linearity over supply and temperature variations, and

provides a drop-in compatible alternative to all ADS1286

performance grades. The robust high impedance input

minimizes errors due to leakage currents, and specified

measurement accuracy is maintained with input signals up to

the supply rails.

The reference accepts inputs between 1.25V to 5.0V, providing

design flexibility in a wide variety of applications. The

ISL2671286 also features up to 8kV Human Body Model ESD

survivability.

The serial digital interface is SPI compatible and is easily

interfaced to all popular FPGAs and microcontrollers.

Operating from a 5V supply, power dissipation is 1.4mW at a

sampling rate of 20kSPS and just 15µW between conversions

utilizing the Auto Power-Down mode. These features make the

ISL2671286 an excellent solution for remote industrial

sensors and battery-powered instruments.

The ISL2671286 is available in an 8 Ld SOIC package and is

specified for operation over the industrial temperature range

of –40°C to +85°C.

Features

• Drop-In Compatible with ADS1286 (All Performance Grades)

• Simple SPI-compatible Serial Digital Interface

• Guaranteed No Missing Codes

• 20kHz Sampling Rate

• +4.50V to +5.25V Supply

• Low 280µA Operating Current (20kSPS)

• Power-down Current between Conversions: 3µA

• Excellent Differential Non-Linearity (0.75LSB Max)

• Low THD: -83dB (Typ)

• Pb-Free (RoHS Compliant)

• Available in SOIC Package

Applications

• Remote Data Acquisition

• Battery Operated Systems

• Industrial Process Control

• Energy Measurement

• Data Acquisition Systems

• Pressure Sensors

• Flow Controllers

VREF

+VCC

+IN DCLOCK

SAR

LOGIC

SERIAL

INTERFACE

DOUT

–IN CS/SHDN

VREF

GND

FIGURE 1. BLOCK DIAGRAM

3

2

1

0

-1

-2

-3

0

512 1024 1536 2048 2560 3072 3584

CODE

FIGURE 2. DIFFERENTIAL LINEARITY ERROR vs CODE

4096

November 1, 2011

FN7863.0

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 |Copyright Intersil Americas Inc. 2011. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL2671286

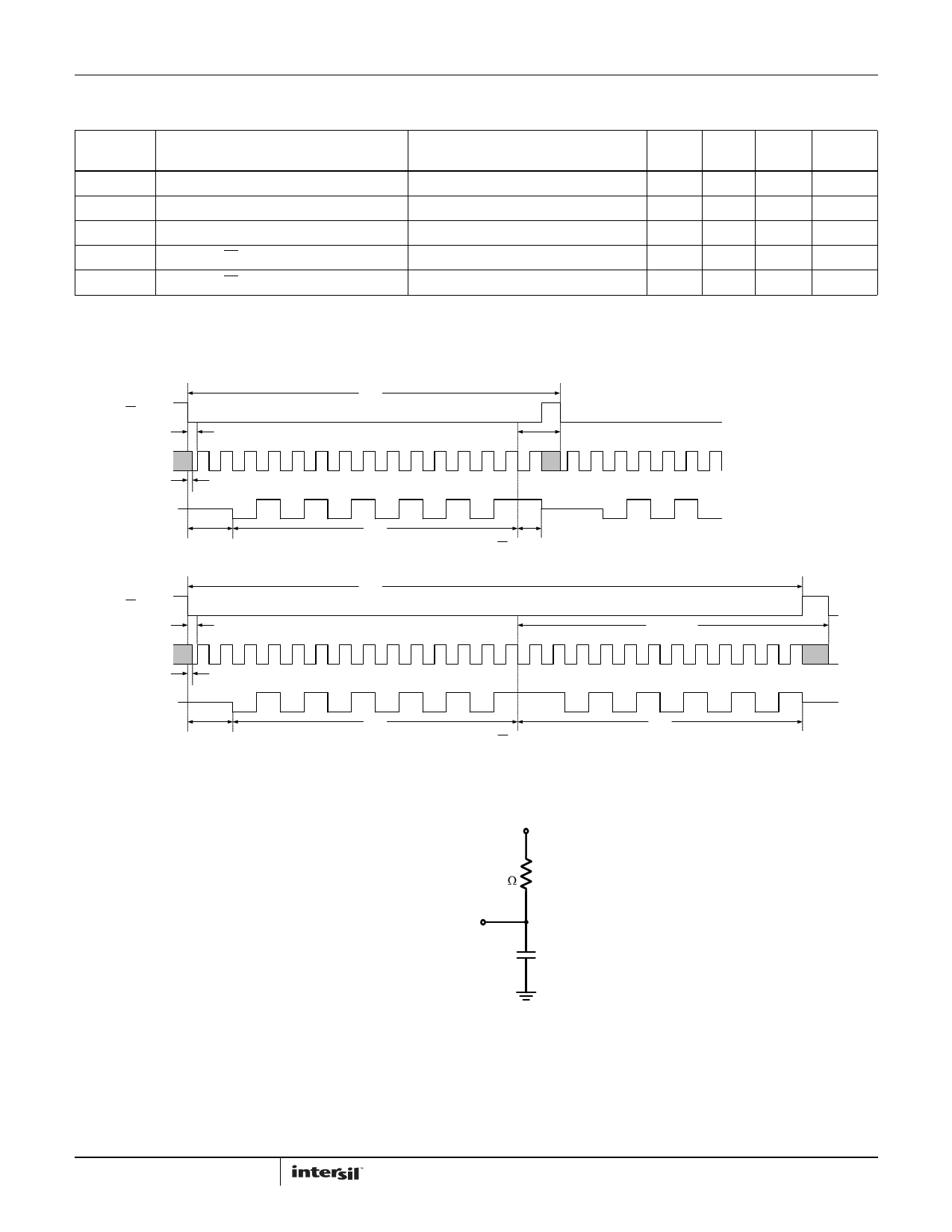

Timing Specifications At fCLK = 200kHz , unless otherwise noted. Typical values are at TA = +25°C. Boldface limits apply over the

operating temperature range, -40°C to +85°C. (Continued)

SYMBOL

PARAMETER

TEST CONDITIONS

MIN MAX

(Note 8) TYP (Note 8) UNITS

thDO

Output Data Remains Valid After DCLOCK↓ CLOAD = 100pF

15 30

ns

tf DOUT Fall Time

See test circuits; Figure 4

1 100

ns

tR DOUT Rise Time

See test circuits; Figure 4

1 100

ns

tCSD Delay Time, CS/SHDN↓ to DCLOCK↓

See operating sequence; Figure 3

0 ns

tSUCS

Delay Time, CS/SHDN↓ to DCLOCK↑

See operating sequence; Figure 3

30

ns

NOTE:

11. During characterization, tDIS is measured from the release point with a 10pF load (see Figure 4) and the equivalent timing using the ADS1286

loading (3kΩ, 100pF) is calculated.

CS/SHDN

DCLOCK

DOUT

CS/SHDN

DCLOCK

DOUT

tSUCS

tCYC

POWER

DOWN

tCSD

Hi-Z

tSMPL

Null

Bit B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0(1)

Hi-Z

(MSB)

tCONV

tDATA

Note: (1) After completing the data transfer, additional clocks applied while CS/SHDN is low

will result in the previous data being retransmitted LSB-first, followed by indefinite

transmission of zeros

tCYC

Null

Bit B11 B10 B9

B8

tSUCS

POWER

DOWN

tCSD

Hi-Z

tSMPL

Null

Bit B11 B10 B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9 B10 B11

Hi-Z

(2)

(MSB)

tCONV

tDATA

Note: (2) After completing the data transfer, additional clocks applied while CS/SHDN is low

will result in indefinite transmission of zeros

FIGURE 3. SERIAL INTERFACE TIMING DIAGRAM

+VCC

RL

2.85k

OUTPUT PIN

CL

10pF

FIGURE 4. EQUIVALENT LOAD CIRCUIT

5 FN7863.0

November 1, 2011

5 Page

ISL2671286

Functional Description

The ISL2671286 is based on a successive approximation register

(SAR) architecture utilizing capacitive charge redistribution

digital-to-analog converters (DACs). Figure 26 shows a simplified

representation of the converter. During the acquisition phase

(ACQ), the differential input is stored on the sampling capacitors

(CS). The comparator is in a balanced state since the switch

across its inputs is closed. The signal is fully acquired after tACQ

has elapsed, and the switches then transition to the conversion

phase (CONV) so the stored voltage can be converted to digital

format. The comparator becomes unbalanced when the

differential switch opens and the input switches transition

(assuming that the stored voltage is not exactly at mid-scale).

The comparator output reflects whether the stored voltage is

above or below mid-scale, which sets the value of the MSB. The

SAR logic then forces the capacitive DACs to adjust up or down by

one-quarter of full-scale by switching in binarily weighted

capacitors. Again, the comparator output reflects whether the

stored voltage is above or below the new value and sets the value

of the next lowest bit. This process repeats until all 12 bits have

been resolved.

VIN+

VIN–

CONV

ACQ

ACQ

ACQ CONV

CONV

VREF

SAR

LOGIC

FIGURE 26. SAR ADC ARCHITECTURAL BLOCK DIAGRAM

Analog Input

The ISL2671286 features a pseudo-differential input with a

nominal full-scale range equal to the applied VREF voltage. The

negative input (VIN–) must be biased within 200mV of ground.

Modes of Operation

There are two possible modes of operation, which are controlled

by the CS/SHDN signal. When CS/SHDN is high (deasserted), the

ADC is in static mode. Conversely, when CS/SHDN is low

(asserted), the device is in dynamic mode. There is no minimum

or maximum number of SCLK cycles required to enter static

mode. This simplifies power management and allows the user to

easily optimize power dissipation versus throughput for various

application requirements.

DYNAMIC MODE

This mode is entered when a conversion result is desired by

asserting CS/SHDN. Figure 28 shows the general operation in

this mode. The conversion is initiated on the falling edge of

CS/SHDN (refer to “Serial Digital Interface” section). When

CS/SHDN is deasserted, the conversion is terminated, and DOUT

returns to a high-impedance state. Sixteen serial clock cycles are

required to complete the conversion and access the complete

conversion result. CS/SHDN may idle high until the next

conversion or idle low until sometime prior to the next

conversion. Once a data transfer is complete (DOUT has returned

to a high-impedance state), another conversion can be initiated

by again asserting CS/SHDN.

CSB

SCLK

1

10 16

ADC Transfer Function

The output coding for the ISL2671286 is straight binary. The first

code transition occurs at successive LSB values (i.e., 1 LSB, 2

LSB, and so on). The LSB size is VREF/4096. The ideal transfer

characteristic of the ISL2671286 is shown in Figure 27.

111...111

111...110

1LSB = VREF/4096

100...001

100...000

011...111

000...010

000...001

000...000

0V +½LSB

+VREF +VREF

– 1½LSB – 1LSB

ANALOG INPUT

+IN – (–IN)

FIGURE 27. IDEAL TRANSFER CHARACTERISTICS

DOUT

4 LEADING ZEROS AND CONVERSION RESULT

FIGURE 28. NORMAL MODE OPERATION

STANDBY MODE

The ISL2671286 enters the power-saving static mode

automatically any time CS/SHDN is deasserted. The user is not

required to force a device into this mode following a conversion

in order to optimize power consumption.

SHORT CYCLING

In cases where a lower resolution conversion is acceptable,

CS/SHDN can be pulled high before 12 SCLK falling edges have

elapsed. This is referred to as short cycling, and it can be used to

further optimize power dissipation. In this mode, a lower

resolution result is acquired, but the ADC enters static mode

sooner and exhibits a lower average power dissipation than if the

complete conversion cycle is carried out. The acquisition time

(tACQ) requirement must be met for the next conversion to be

valid.

POWER-ON RESET

The ISL2671286 performs a power-on reset that requires

approximately 2.5ms to execute when the supplies are first

11 FN7863.0

November 1, 2011

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet ISL2671286.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL2671286 | 20kSPS SAR ADC | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |