|

|

PDF ACE25C200G Data sheet ( Hoja de datos )

| Número de pieza | ACE25C200G | |

| Descripción | 2M BIT SPI NOR FLASH | |

| Fabricantes | ACE Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ACE25C200G (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ACE25C200G

2M BIT SPI NOR FLASH

Description

The ACE25C200G is 2M-bit Serial Peripheral Interface(SPI) Flash memory, and supports the

Dual/Quad SPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2 (/WP), and I/O3 (/HOLD).

The Dual I/O data is transferred with speed of 216Mbits/s and the Quad I/O & Quad output data is

transferred with speed of 432Mbits/s. The device uses a single low voltage power

supply, ranging from 2.7 Volt to 3.6 Volt.

Additionally, the device supports JEDEC standard manufacturer and device ID and three

256-bytes Security Registers..

Features

● Serial Peripheral Interface (SPI)

- Standard SPI: SCLK, /CS, SI, SO, /WP, /HOLD

- Dual SPI: SCLK, /CS, IO0, IO1, /WP, /HOLD

- Quad SPI: SCLK, /CS, IO0, IO1, IO2, IO3

● Read

- Normal Read (Serial): 50MHz clock rate

- Fast Read (Serial): 108MHz clock rate

- Dual/Quad (Multi-I/O) Read: 108MHz clock rate

● Program

- Serial-input Page Program up to 256bytes

-Program Suspend and Resume

● Erase

- Block erase (64/32 KB)

- Sector erase (4 KB)

- Chip erase

- Erase Suspend and Resume

● Program/Erase Speed

- Page Program time: 0.7ms typical

- Sector Erase time: 60ms typical

- Block Erase time: 0.3/0.5s typical

- Chip Erase time: 2s typical

● Flexible Architecture

-Sector of 4K-byte

-Block of 32/64K-byte

● Low Power Consumption

- 20mA maximum active current

- 5uA maximum power down current

VER 1.1 1

1 page

ACE25C200G

2M BIT SPI NOR FLASH

HOLD (/HOLD)/IO3

The /HOLD signal goes low to stop any serial communications with the device, but doesn’t stop the

operation of write status register, programming, or erasing in progress.

The operation of HOLD, need /CS keep low, and starts on falling edge of the /HOLD signal, with SCLK

signal being low (if SCLK is not being low, HOLD operation will not start until SCLK being low). The HOLD

condition ends on rising edge of /HOLD signal with SCLK being low (If SCLK is not being low, HOLD

operation will not end until SCLK being low).

The Hold condition starts on the falling edge of the Hold (/HOLD) signal, provided that this coincides

with SCK being at the logic low state. If the falling edge does not coincide with the SCK signal being at the

logic low state, the Hold condition starts whenever the SCK signal reaches the logic low state. Taking the

/HOLD signal to the logic low state does not terminate any Write, Program or Erase operation that is

currently in progress.

VCC Power Supply

VCC is the supply voltage. is the single voltage used for all device functions including read, program,

and erase.

VSS Ground

VSS is the reference for the VCC supply voltage.

VER 1.1 5

5 Page

ACE25C200G

2M BIT SPI NOR FLASH

SRP1, SRP0 bits

The Status Register Protect (SRP1 and SRP0) bits are non-volatile Read/Write bits in the status

register. The SRP bits control the method of write protection: software protection, hardware protection,

power supply lock-down or one time programmable protection.

QE bit

The Quad Enable (QE) bit is a non-volatile Read/Write bit in the Status Register that allows Quad

operation. When the QE bit is set to 0 (Default) the /WP pin and /HOLD pin are enable. When the QE

pin is set to 1, the Quad IO2 and IO3 pins are enabled. (The QE bit should never be set to 1 during

standard SPI or Dual SPI operation if the /WP or /HOLD pins directly to the power supply or ground).

LB3/LB2/LB1 bit

The LB bit is a non-volatile One Time Program (OTP) bit in Status Register that provide the write

protect control and status to the Security Registers. The default state of LB is 0, the security registers

are unlocked. LB can be set to 1 individually using the Write Register instruction. LB is One Time

Programmable, once it’s set to 1, the 256byte Security Registers will become read-only permanently,

LB3/2/1 for Security Registers 3:1.

CMP bit

The CMP bit is a non-volatile Read/Write bit in the Status Register2 (bit6). It is used in conjunction the

SEC-BP0 bits to provide more flexibility for the array protection. Please see the Status registers

Memory Protection table for details. The default setting is CMP=0.

SUS bit

The SUS bit is a read only bit in the status register2 (bit7) that is set to 1 after executing an

Erase/Program Suspend (75H) instruction. The SUS bit is cleared to 0 by Erase/Program Resume

(7AH) instruction as well as a power-down, power-up cycle.

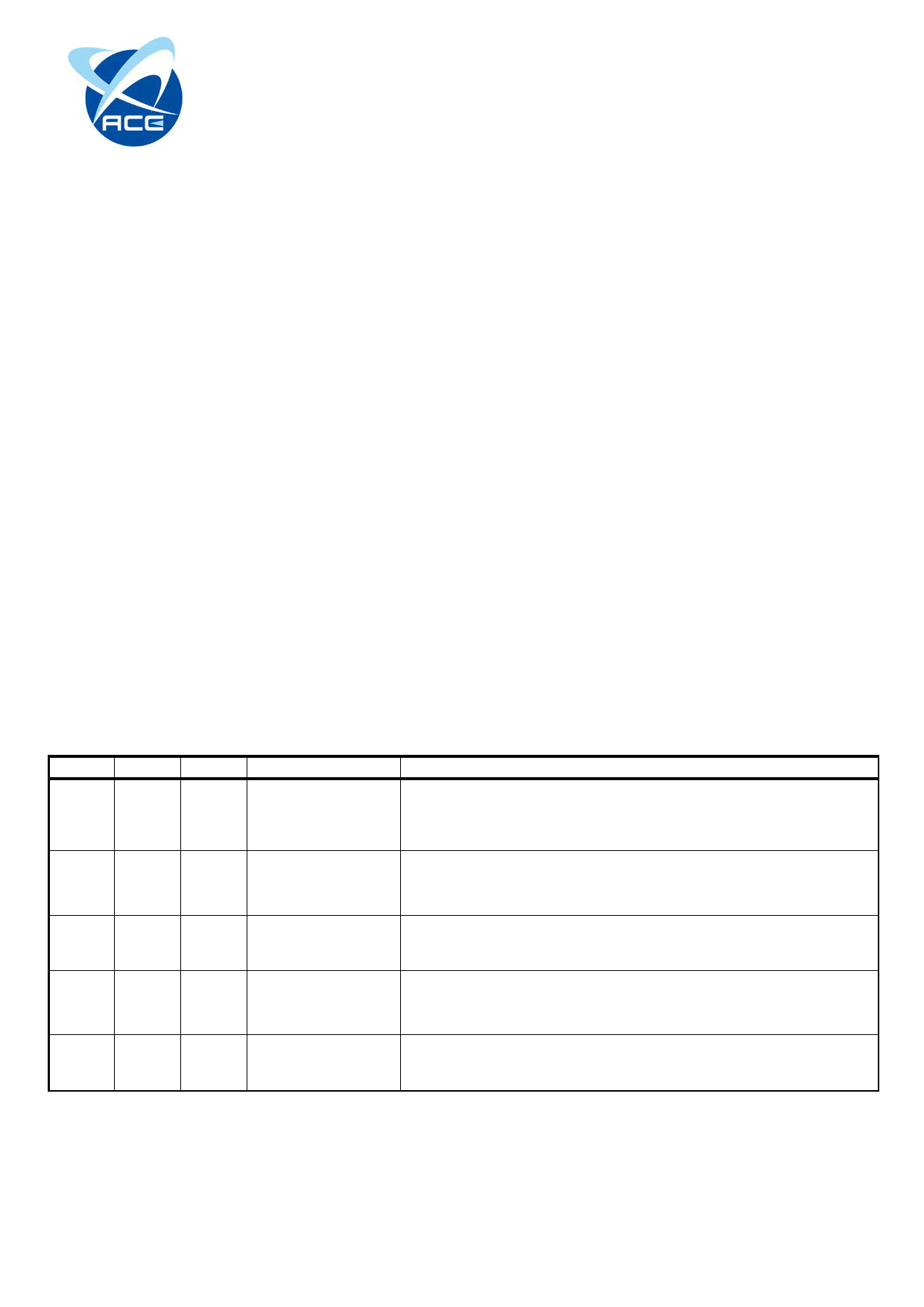

Status Register Protect Table (Table5)

SRP1 SRP0 /WP Status Register

00X

Software

Protected

Description

The Status Register can be written to after a Write

Enable instruction, WEL=1.(Factory Default)

010

Hardware

Protected

/WP=0, the Status Register locked and cannot be

written.

Hardware

/WP=1, the Status Register is unlocked and can be written

011

Unprotected

to after a Write Enable instruction, WEL=1.

Power Supply Status Register is protected and cannot be written

1 0 X Lock-Down(1) To again until the next Power-Down, Power-Up cycle.

11X

One Time

Program(2)

Status Register is permanently protected and cannot be

written to.

Notes:

1. When SRP1, SRP0= (1, 0), a Power-Down, Power-Up cycle will change SRP1, SRP0 to (0, 0) state.

2. The One time Program feature is available upon special order. Please contact ACE for details.

VER 1.1 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ACE25C200G.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ACE25C200G | 2M BIT SPI NOR FLASH | ACE Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |